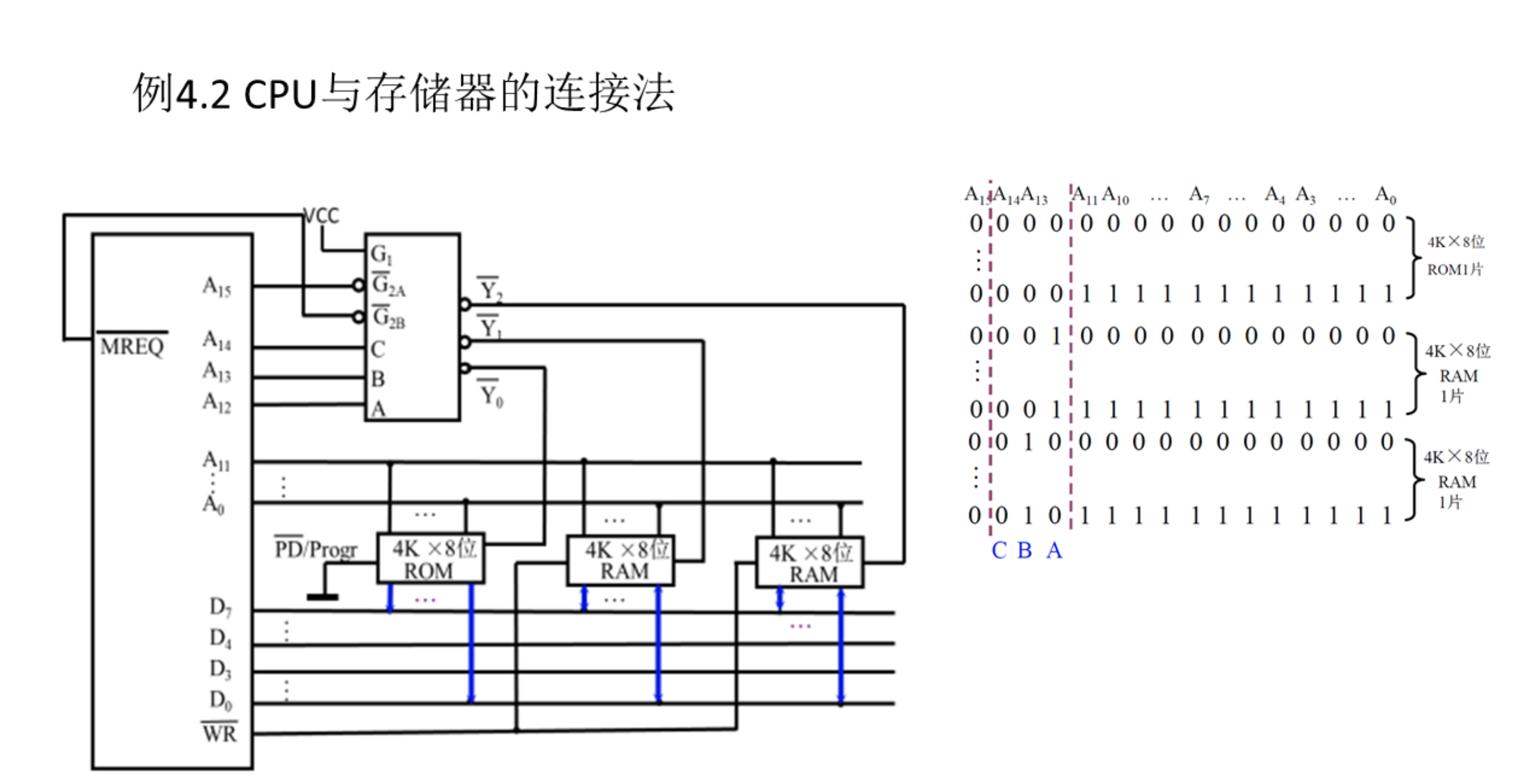

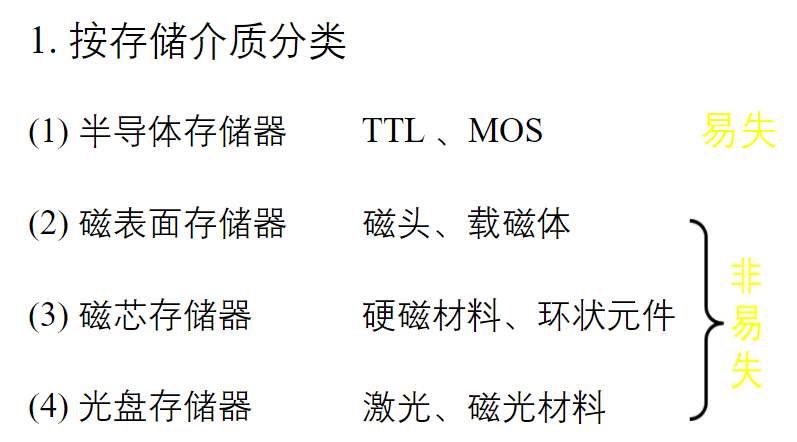

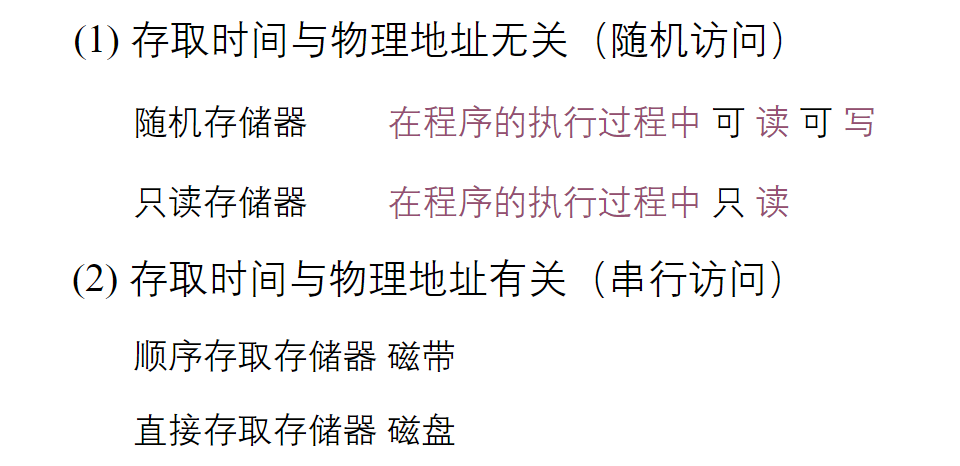

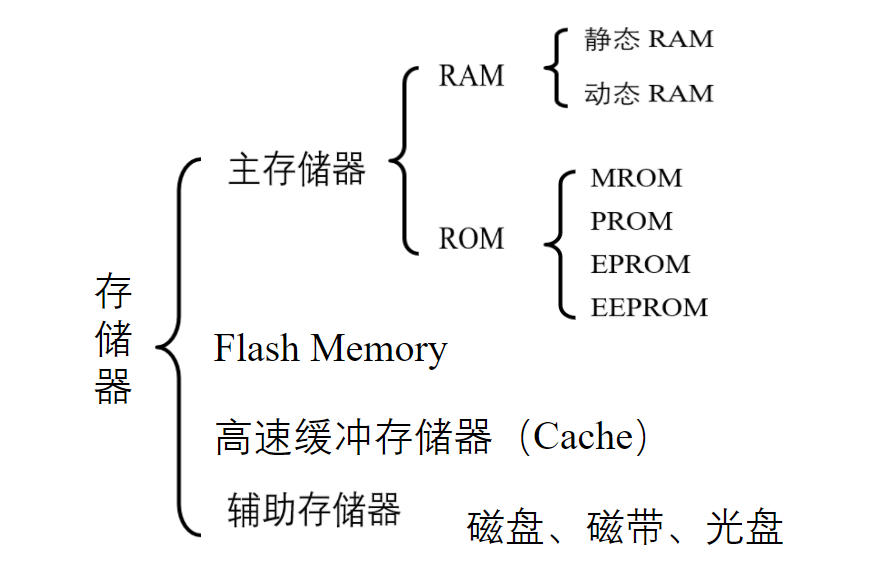

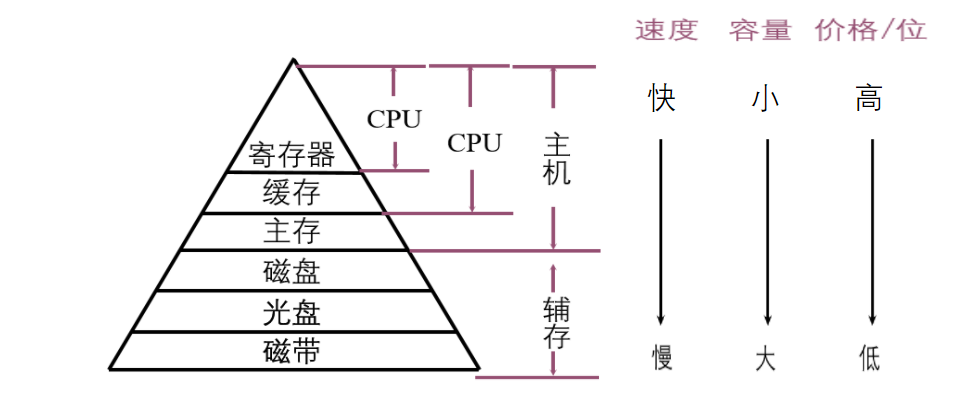

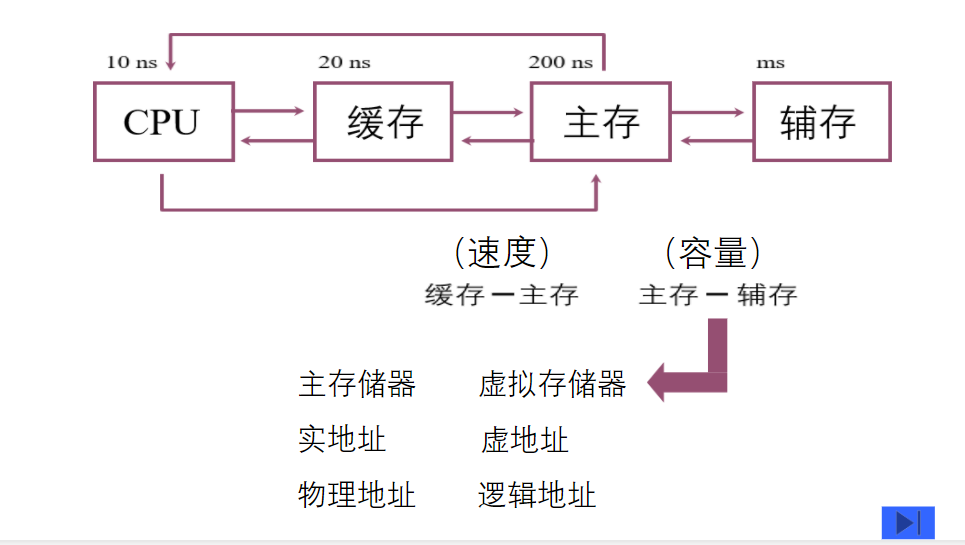

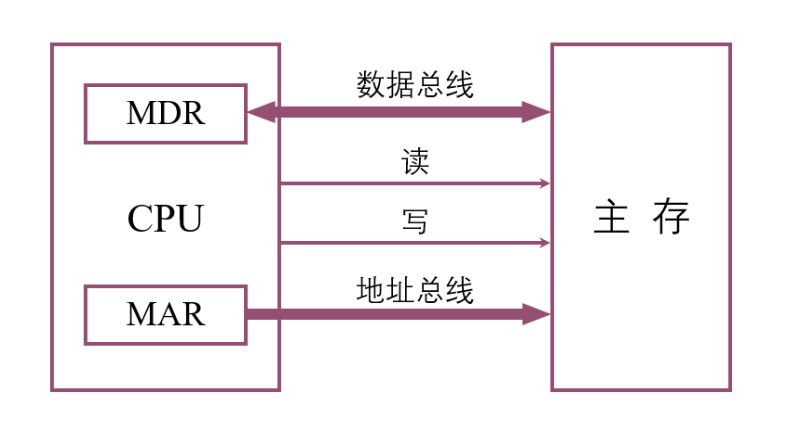

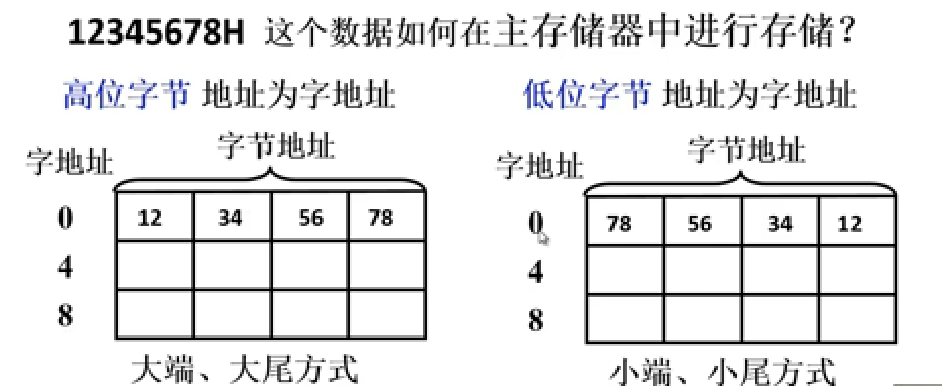

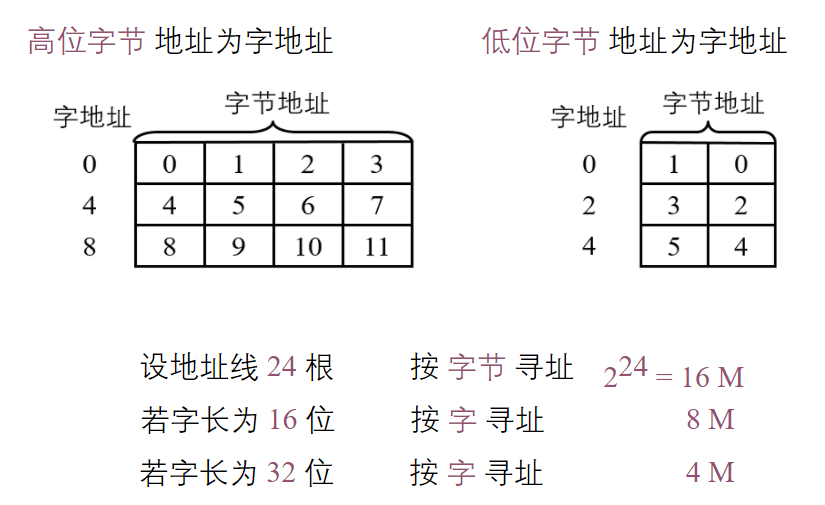

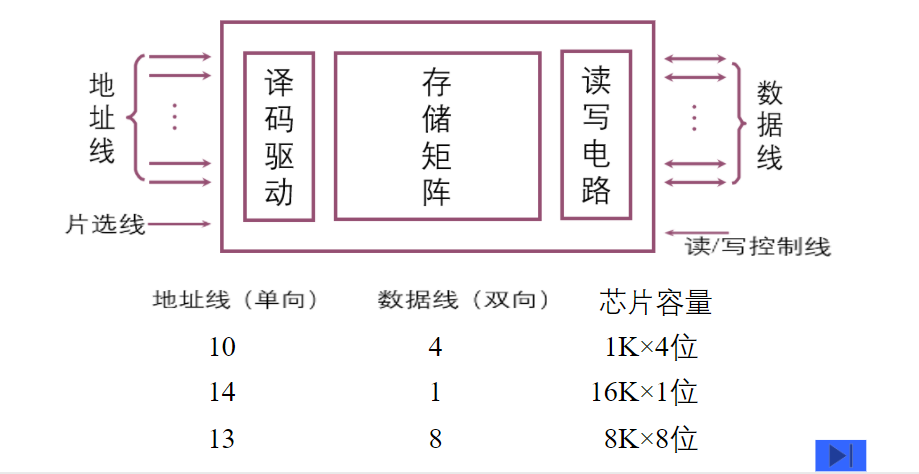

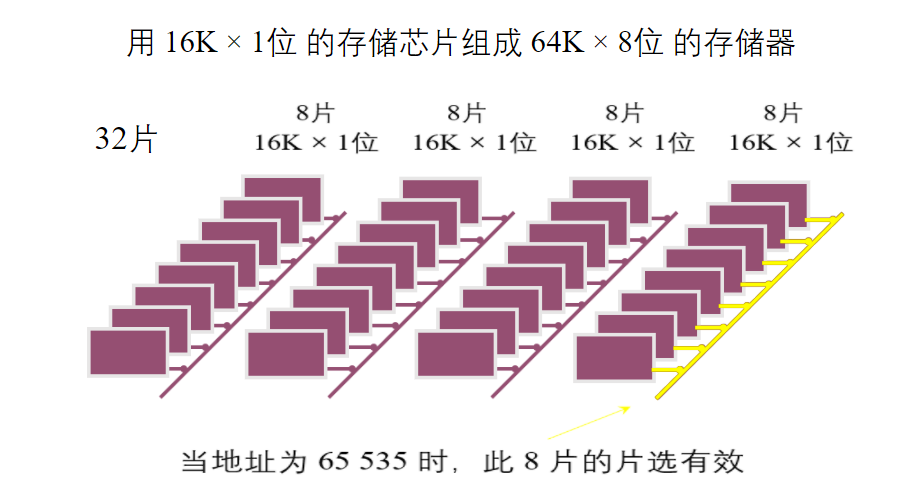

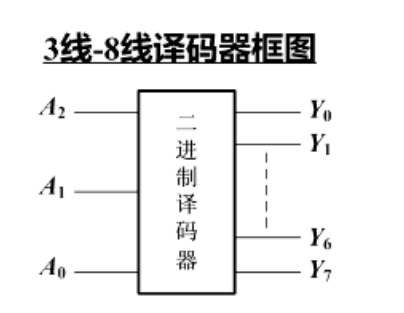

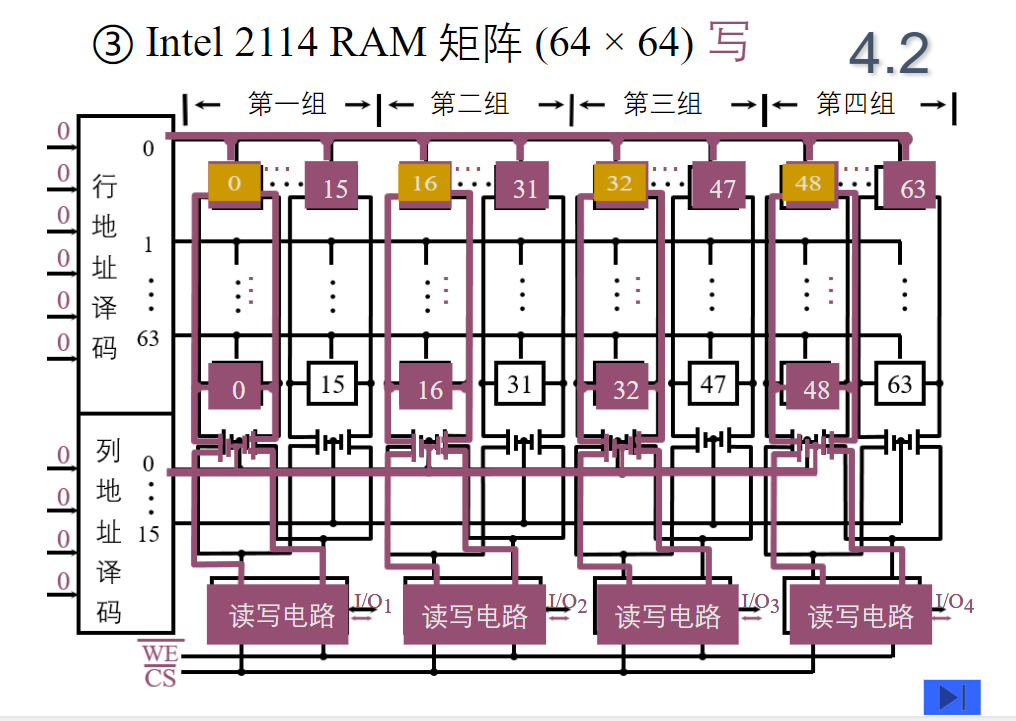

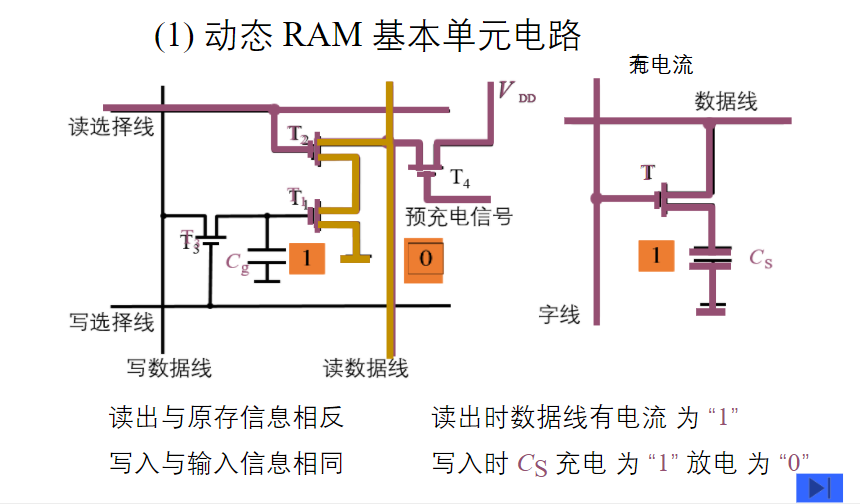

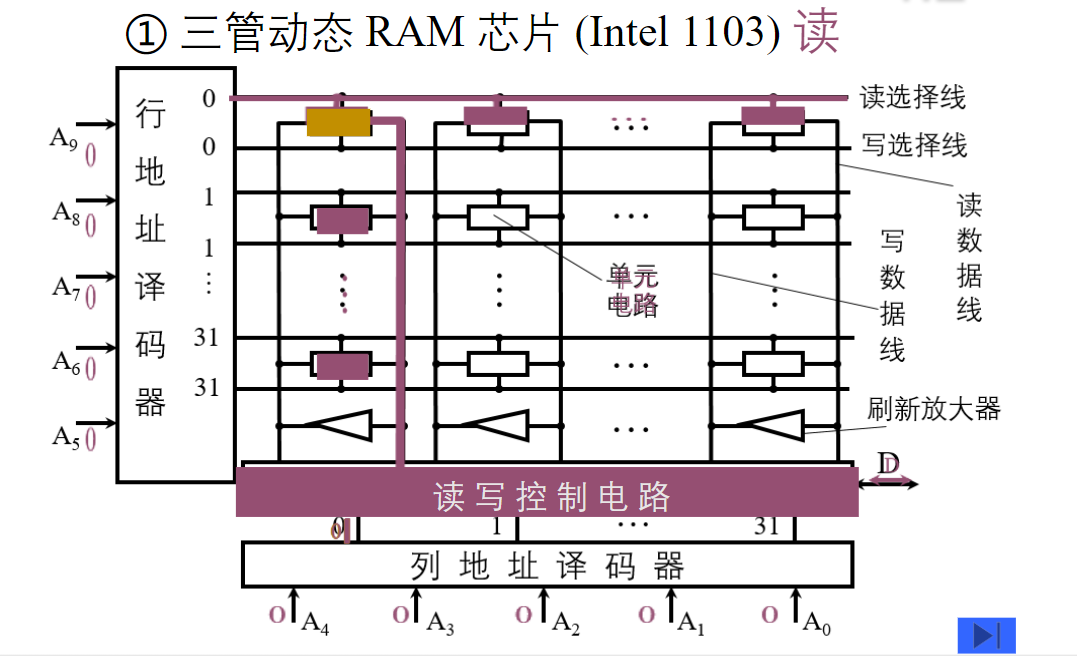

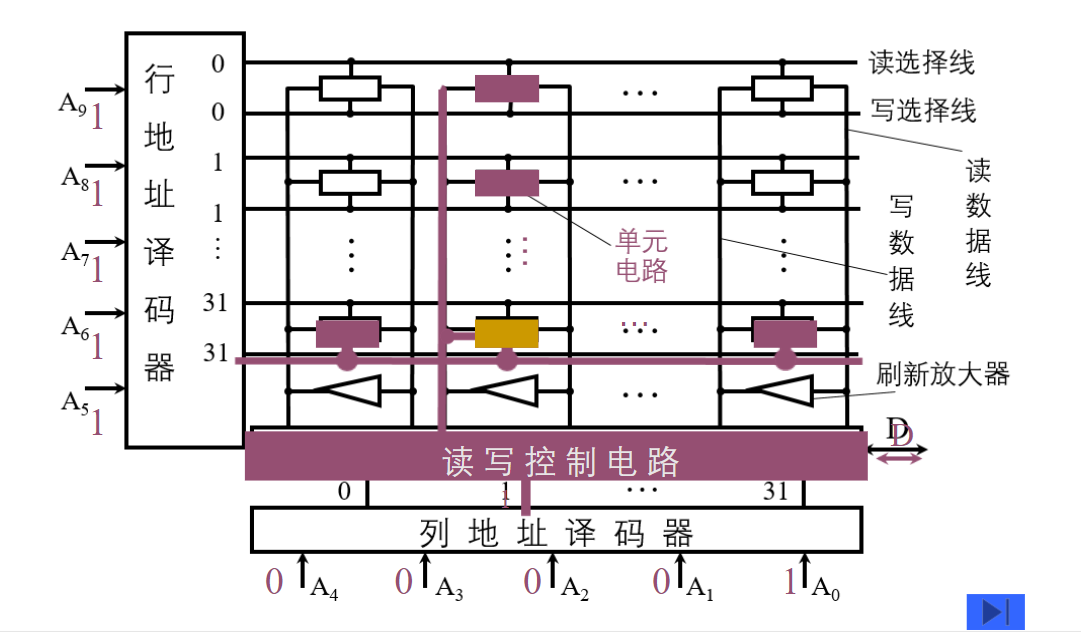

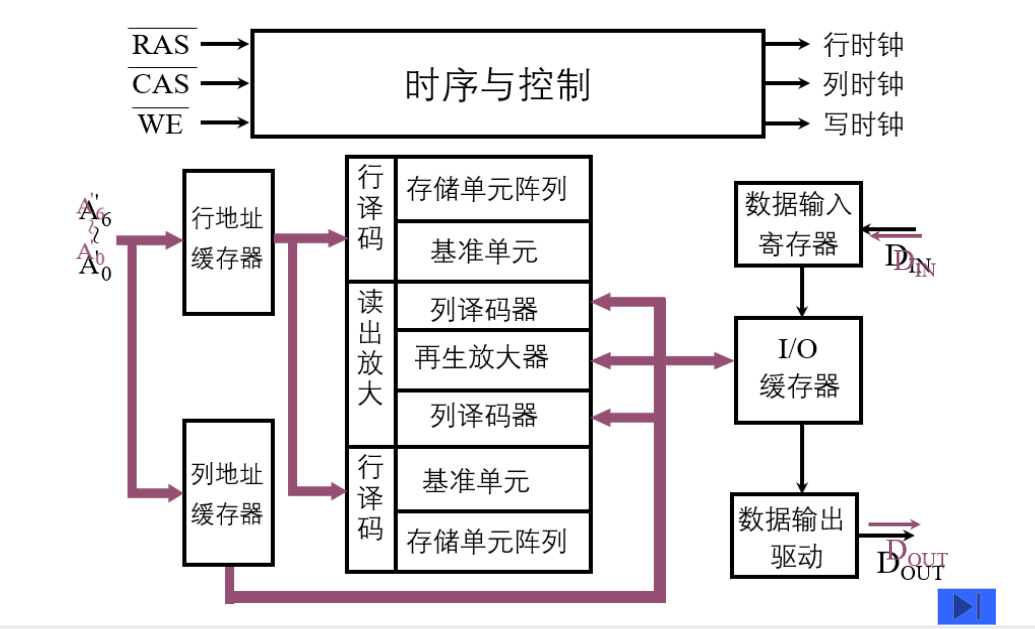

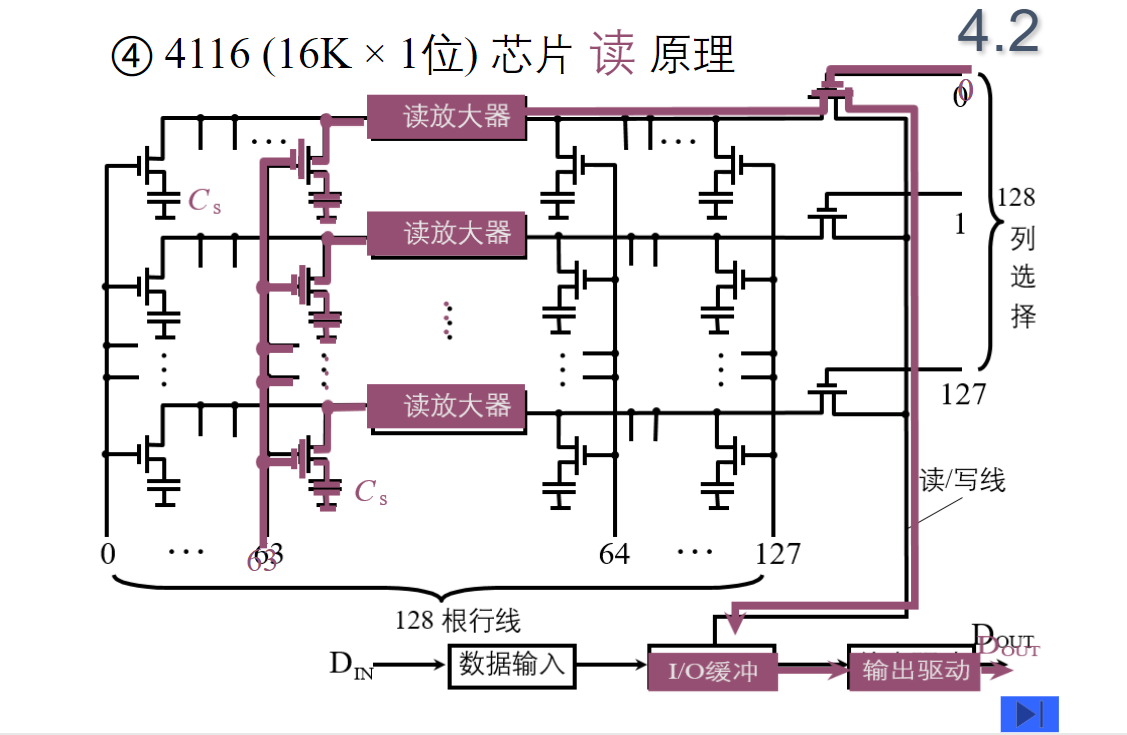

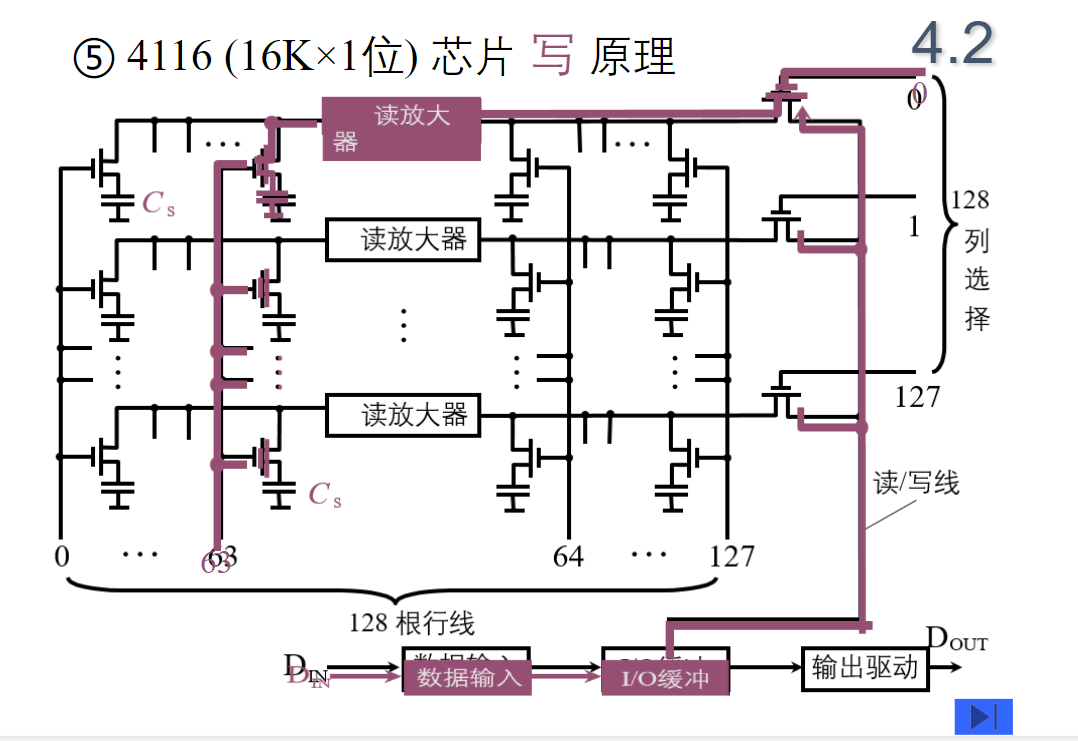

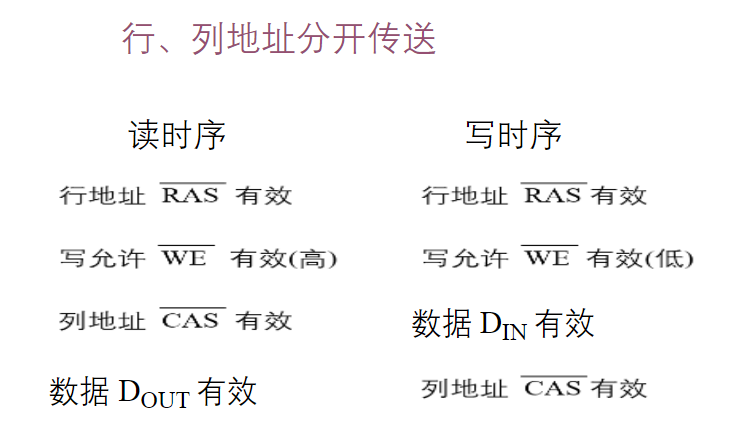

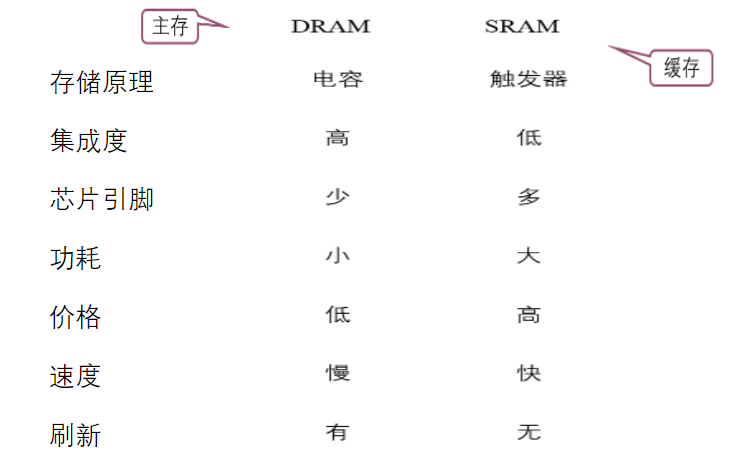

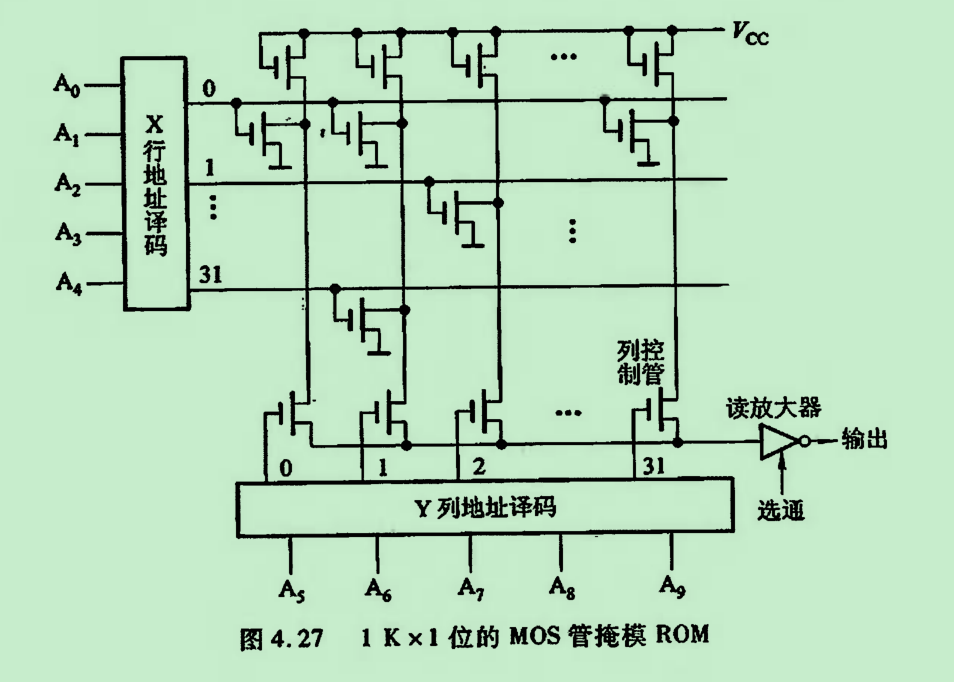

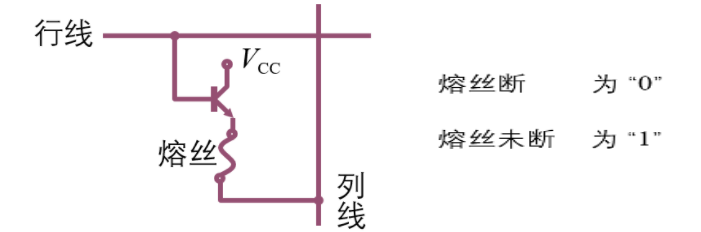

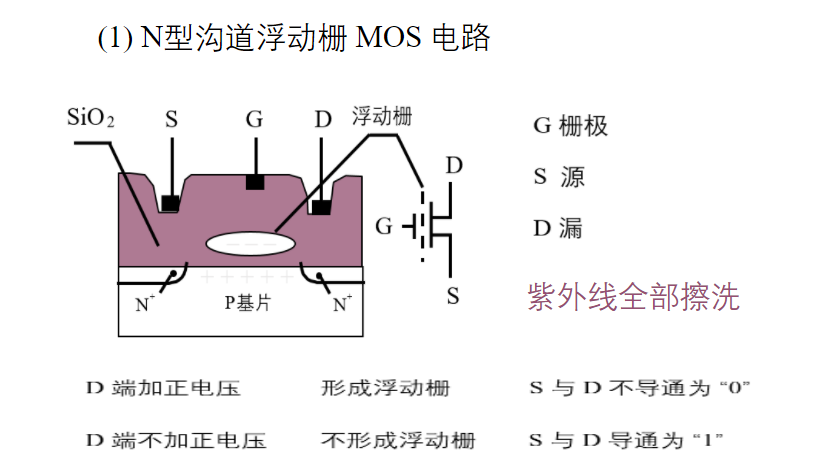

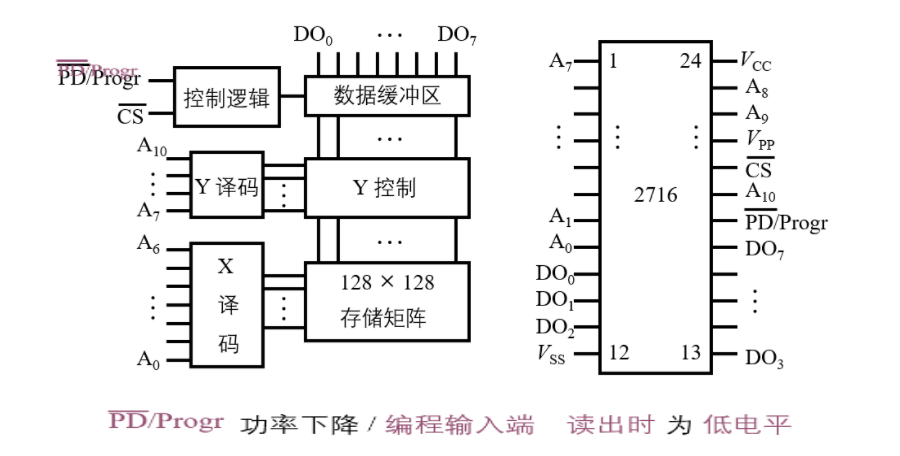

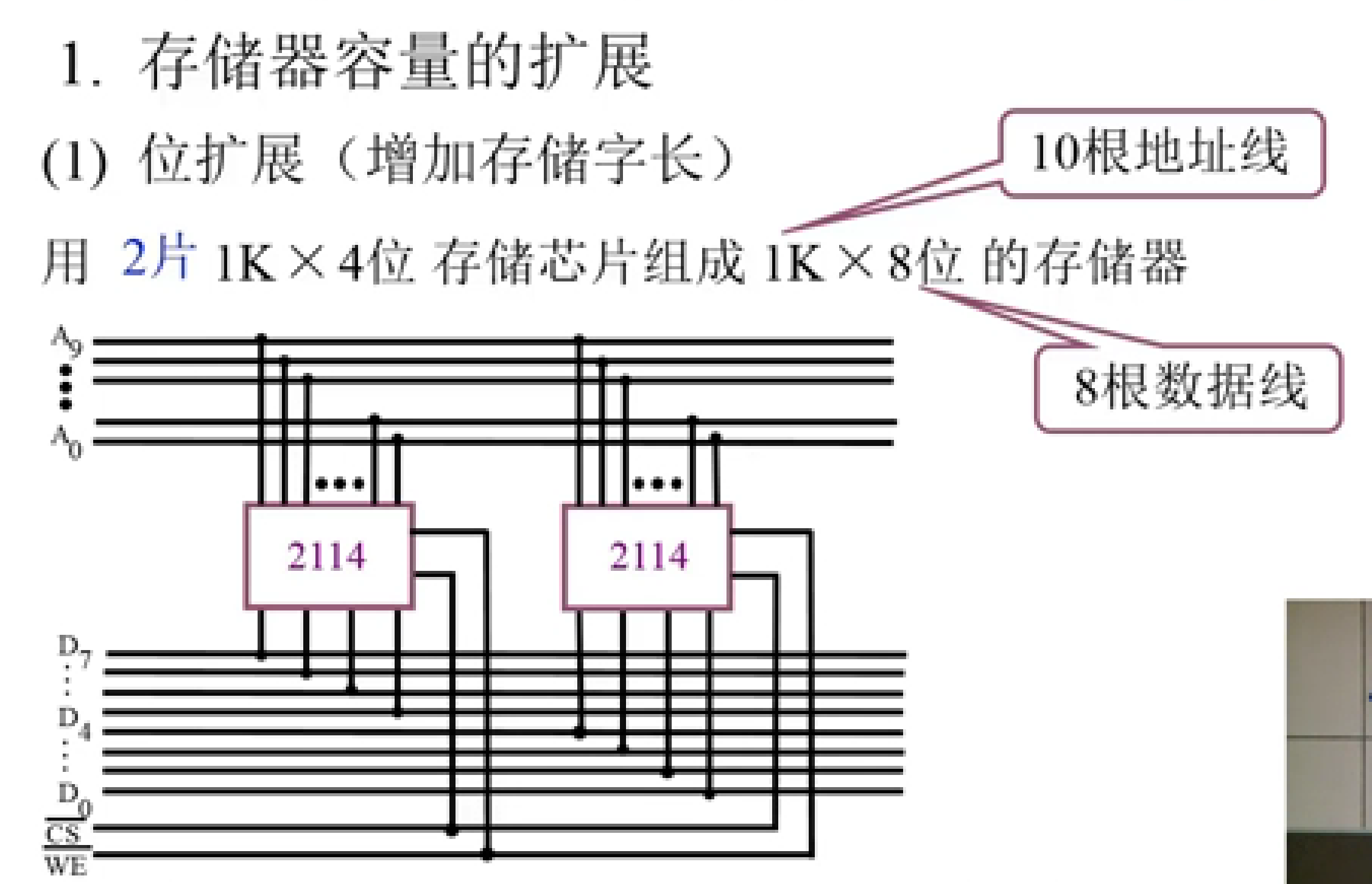

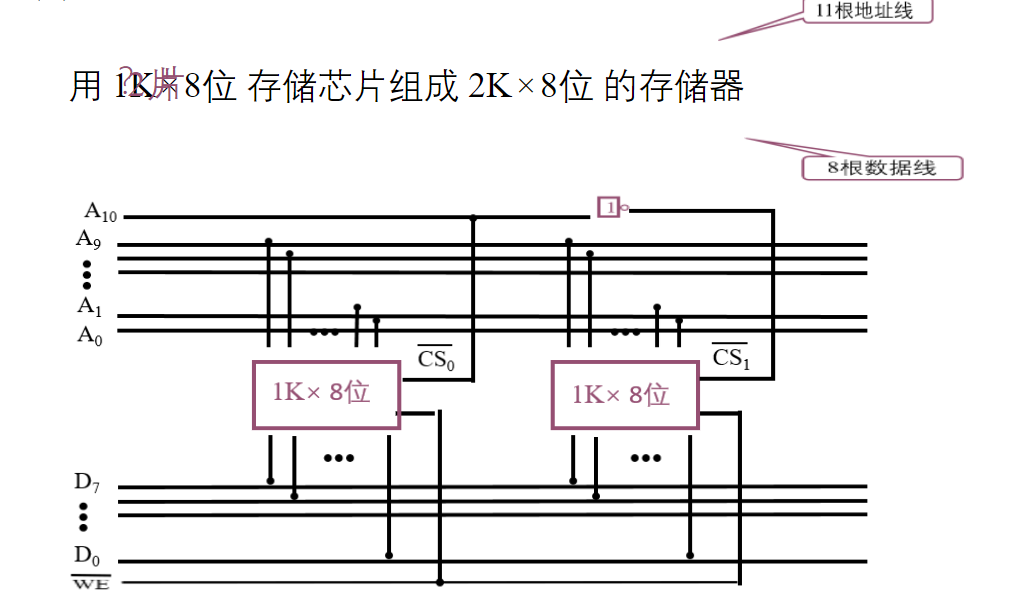

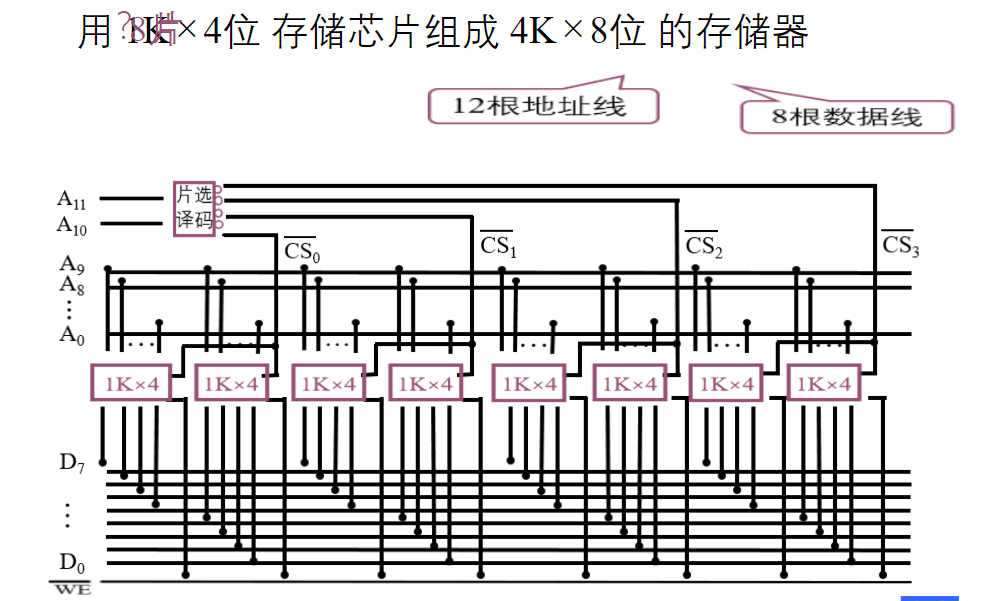

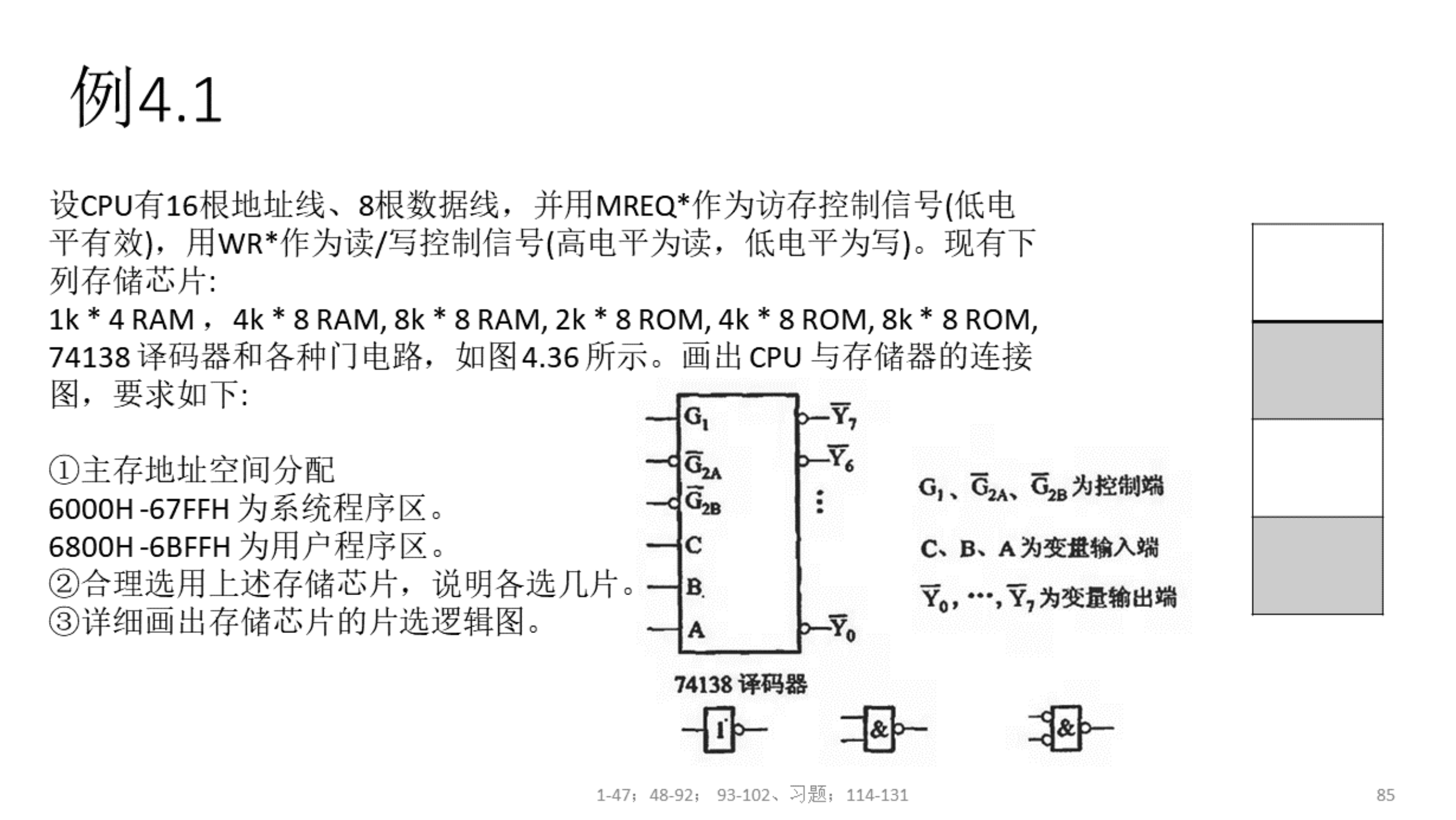

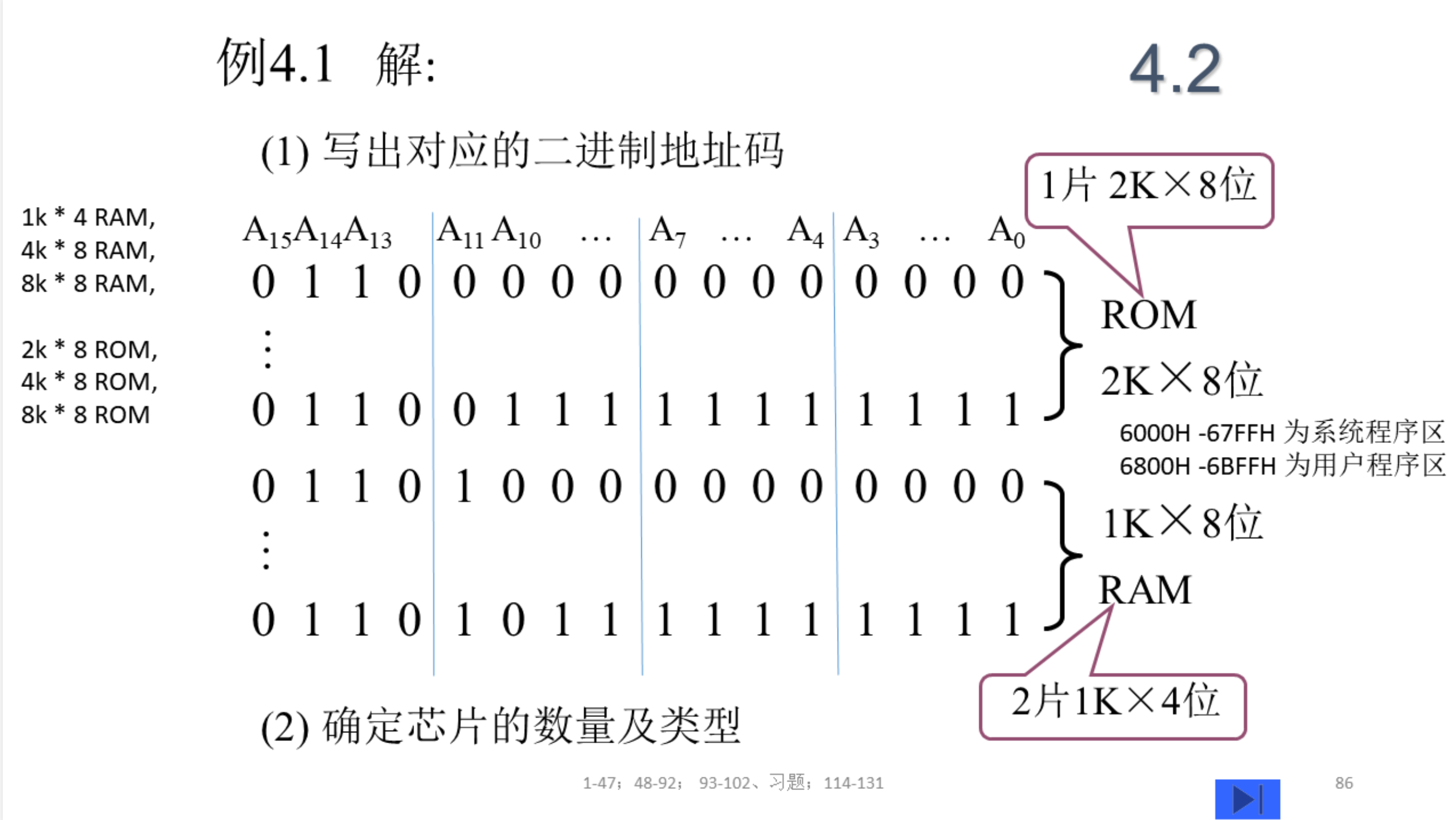

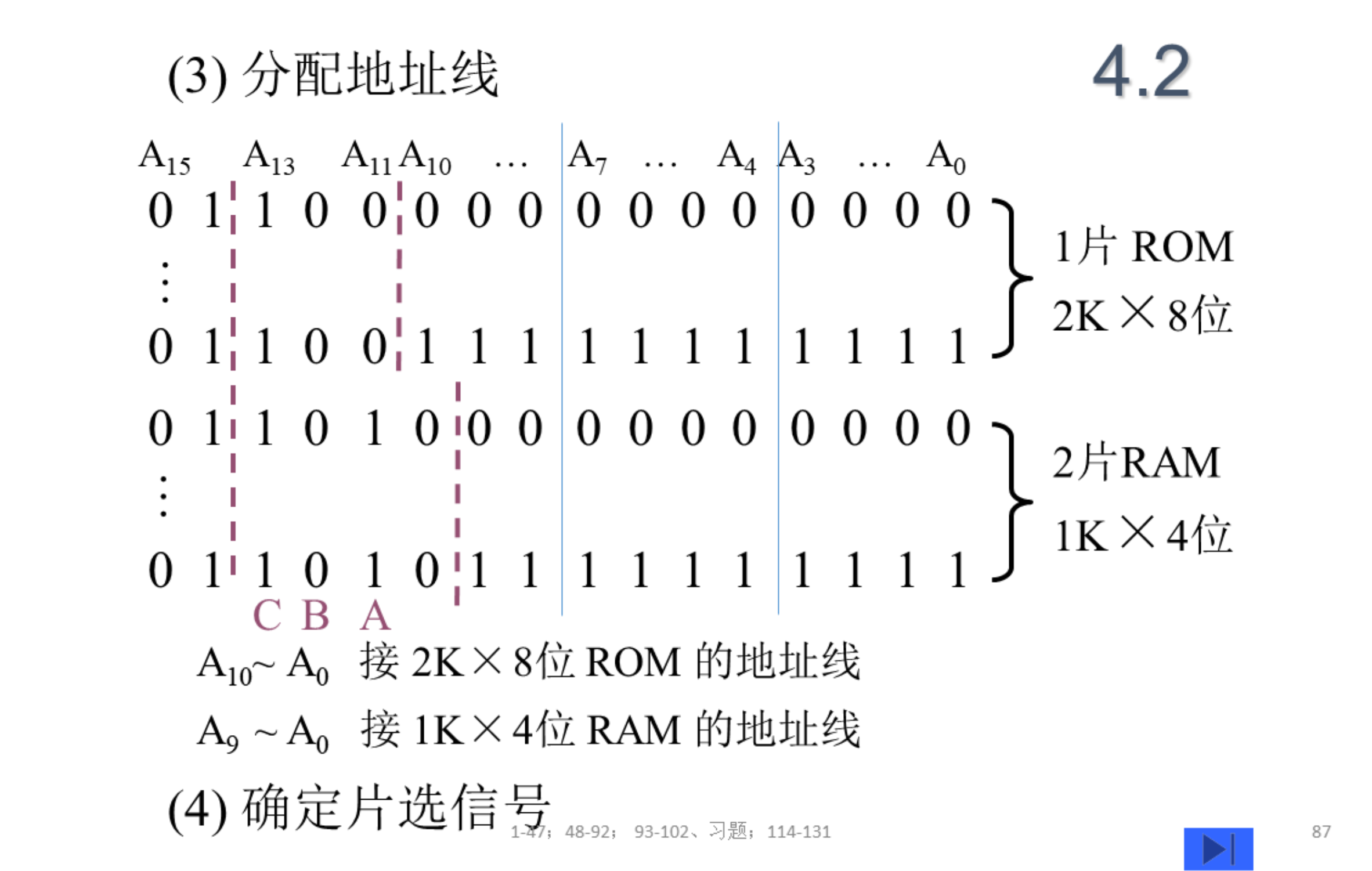

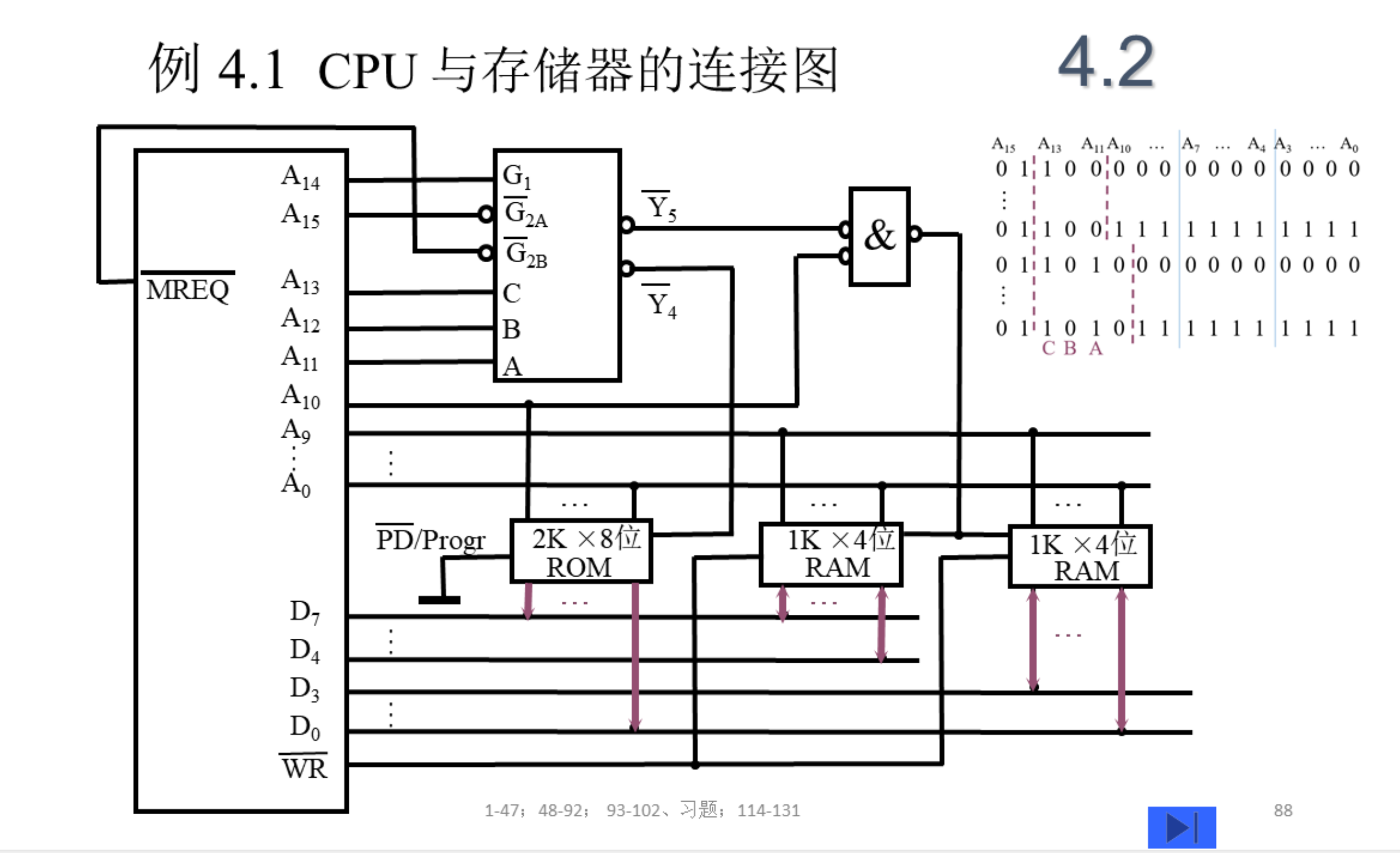

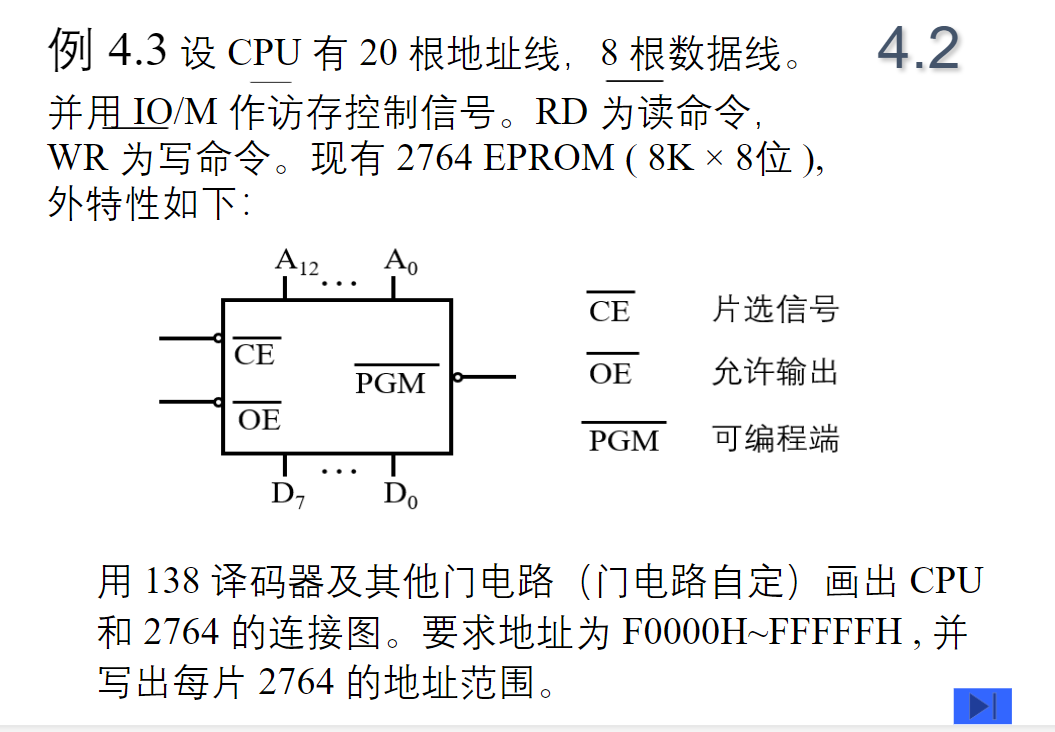

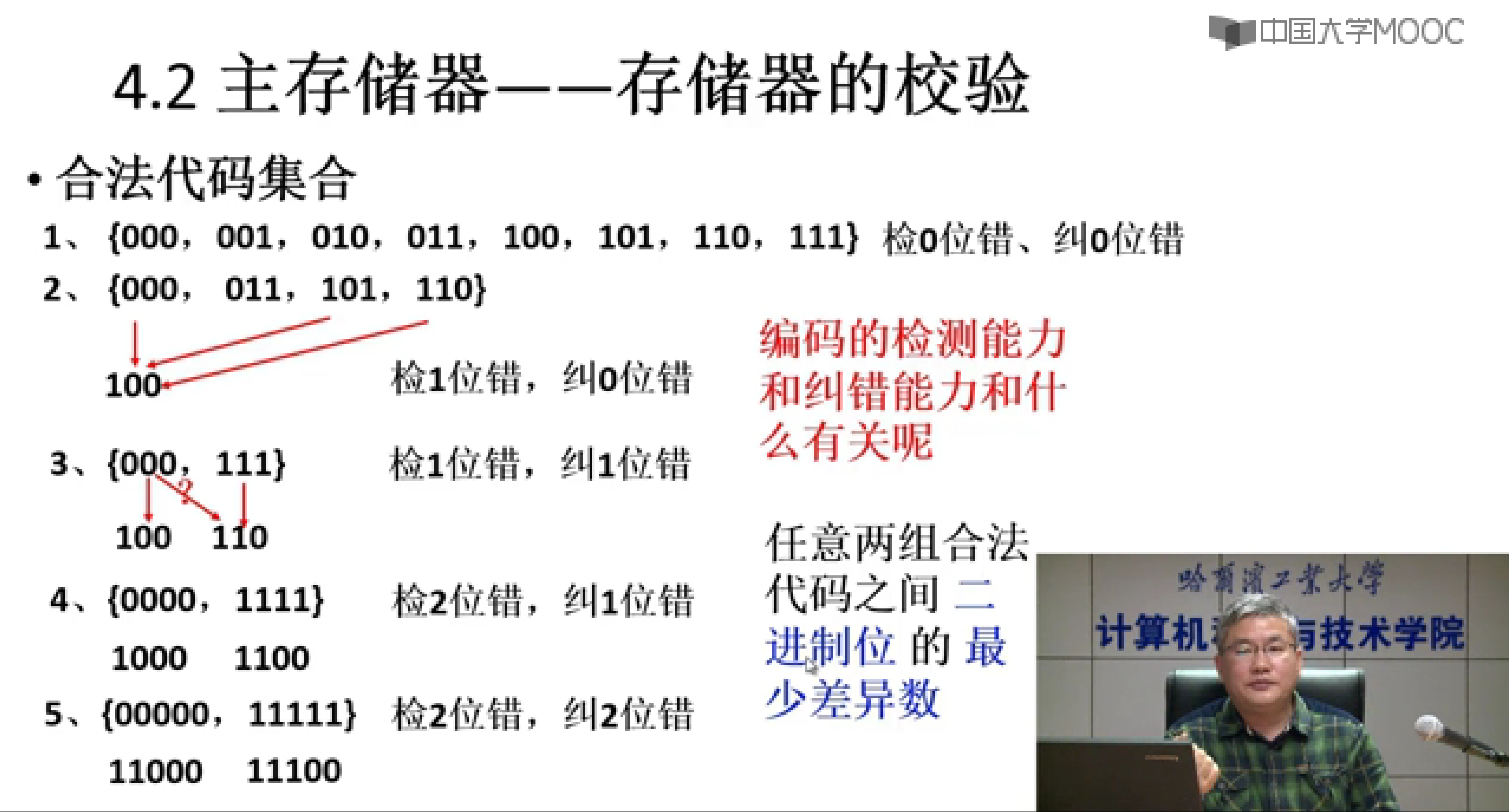

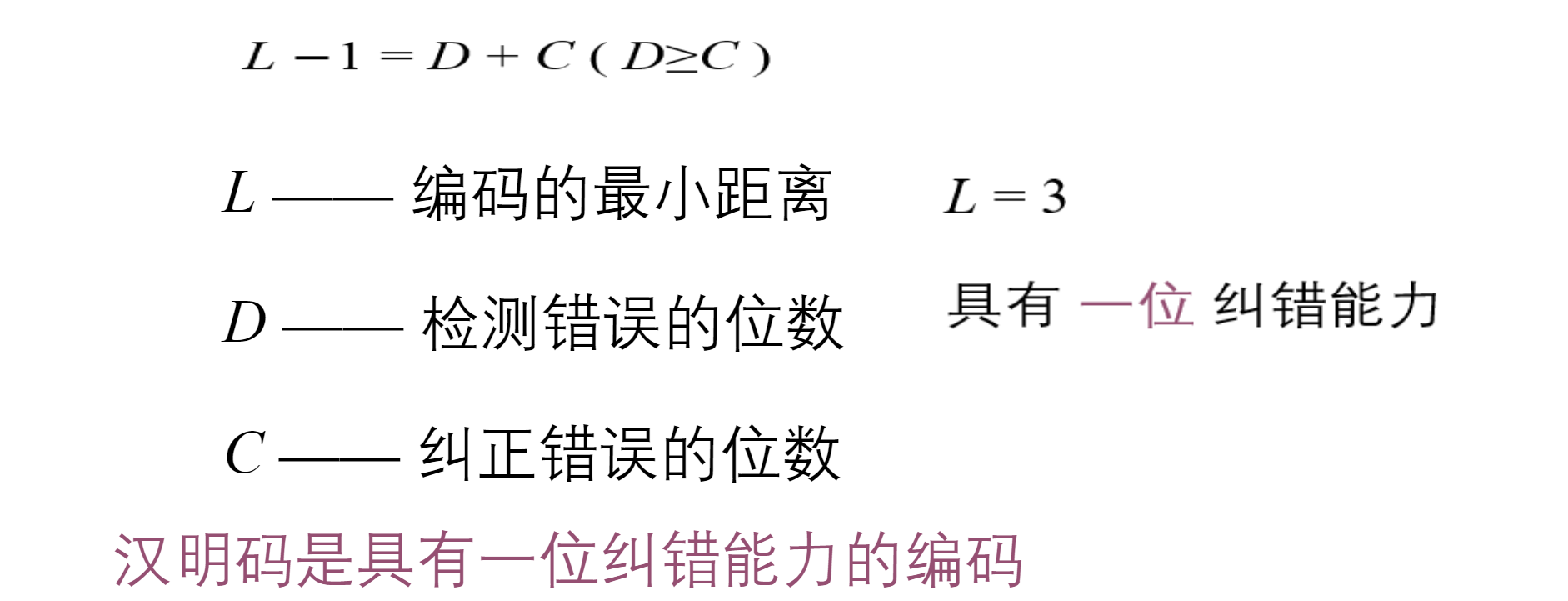

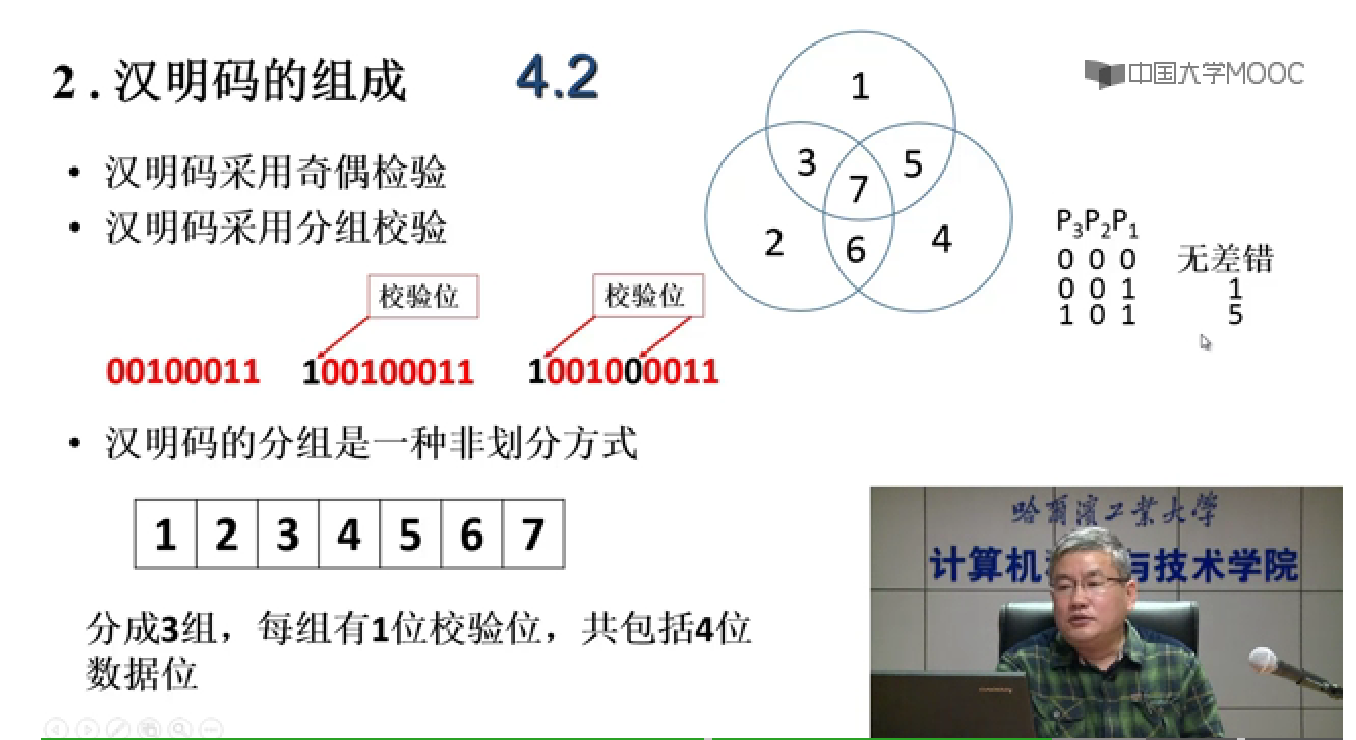

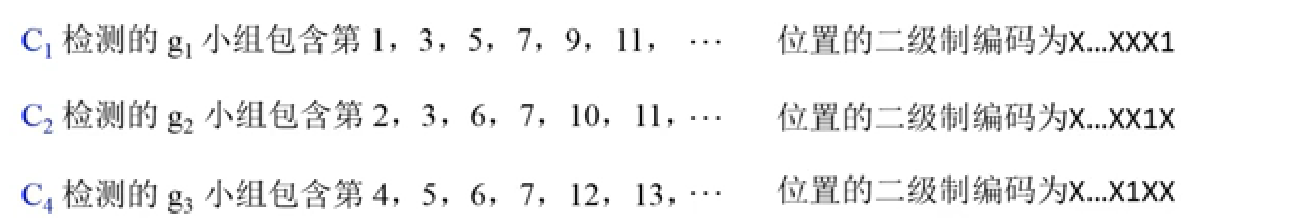

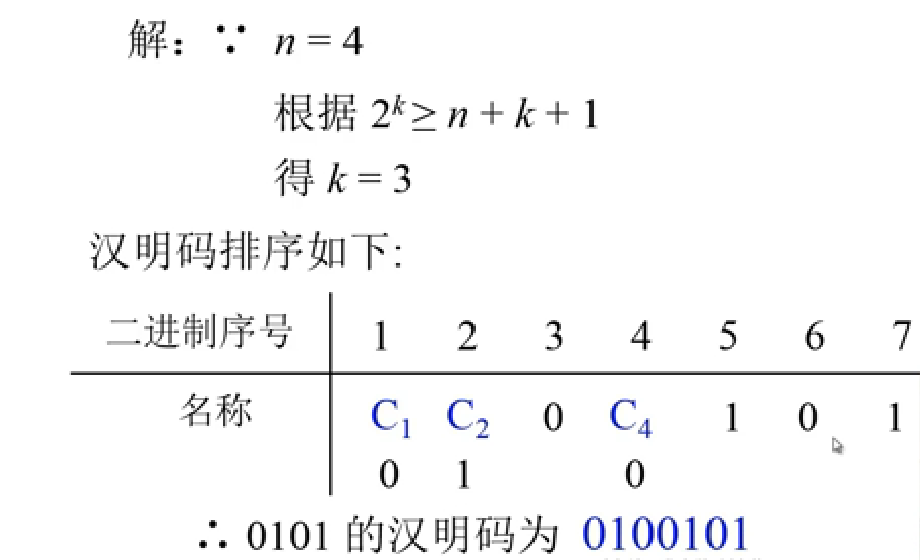

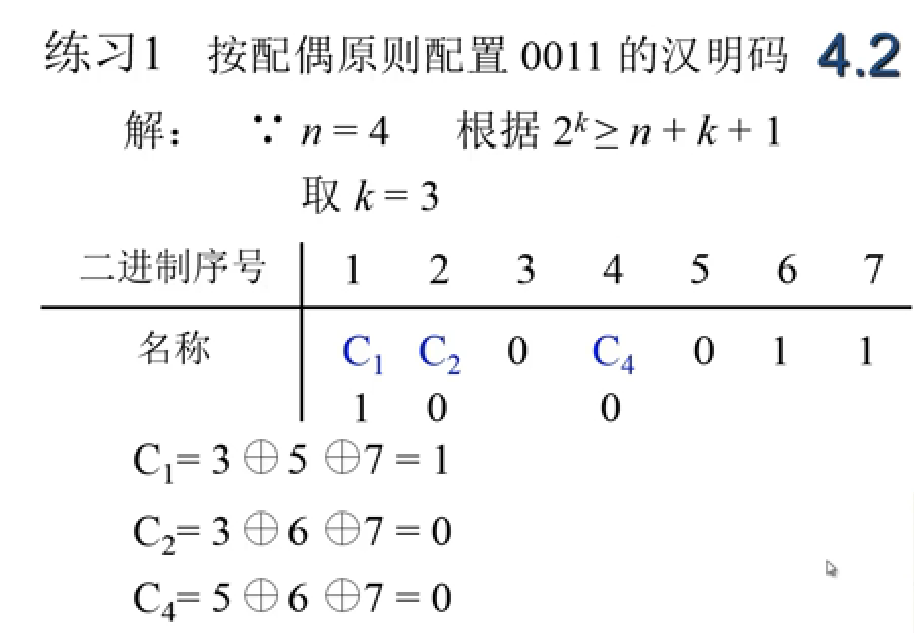

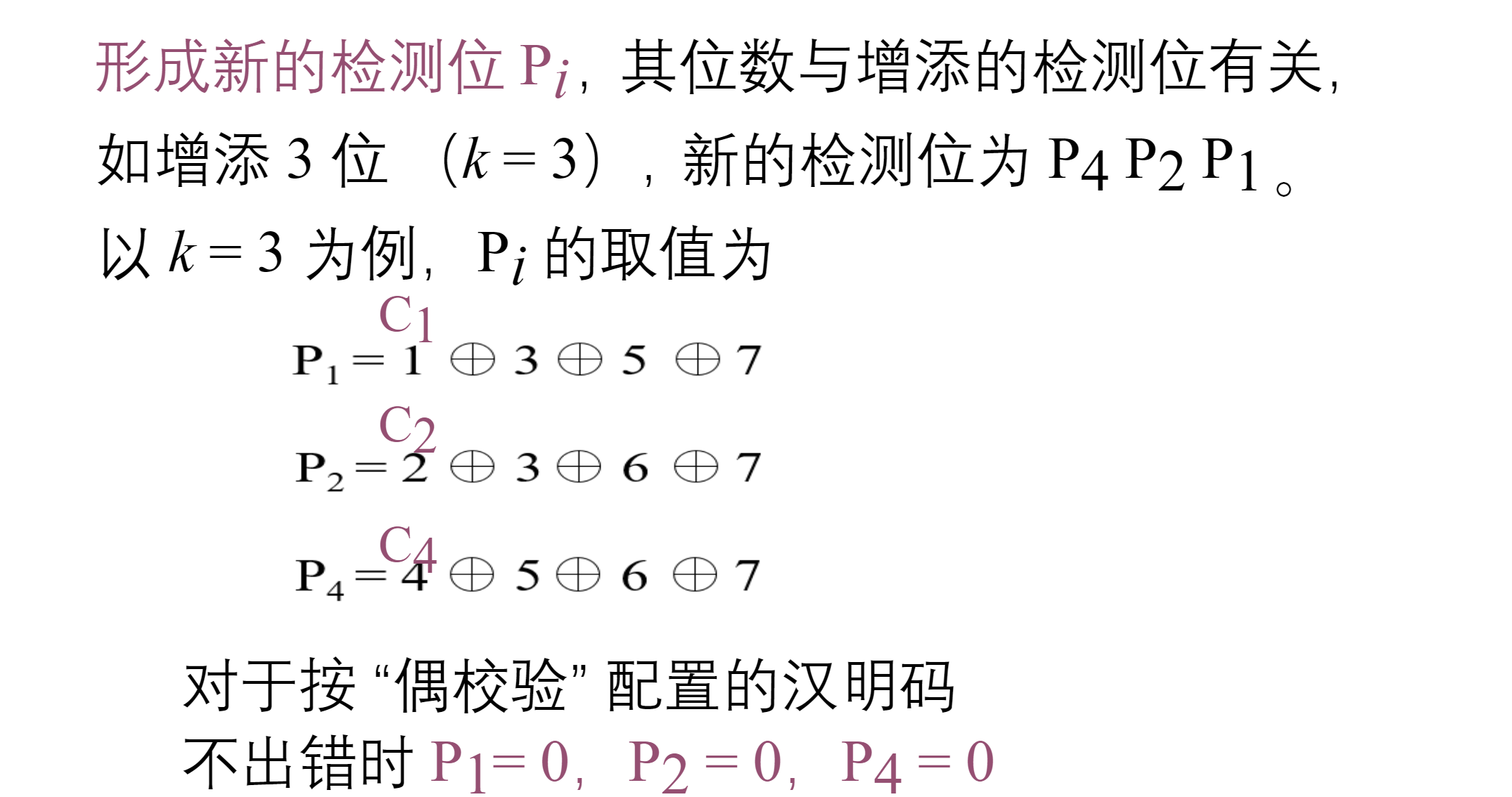

学习笔记|计算机组成原理3-存储器 教材:《计算机组成原理》第二版 作者:唐朔飞 出版社:高等教育出版社 参考课程: 《计算机组成原理》哈尔滨工业大学 ——刘宏伟 、张丽杰 、舒燕君 、张展 、潘道华 学习笔记|计算机组成原理3-存储器 目录 学习笔记|计算机组成原理3-存储器 4.1概述 4.1.1存储器分类 4.1.2存储器层次结构 4.2主存储器 4.2.1主存储器概述 4.2.2半导体存储芯片简介 4.2.3随机存取存储器(RAM) 4.2.4只读存储器(ROM) 4.2.5存储器与CPU的连接 !!!重难点!!! 4.2.6存储器的校验 4.1概述 存储器:是计算机系统中的记忆设备,用来存放程序和数据。 存储介质:能寄存“0”和“1”两种代码并能区分两种状态的物质或件,主要有半导体件、磁性材料和光盘等。 4.1.1存储器分类 (1)按存储介质分类 半导体存储器:TTL双极型(高速 、集成度低 、MOS(主流、集成度高、制造简单、成本低廉、功耗小

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/86737.html