Arm内核由哪些结构组成和特点介绍 ARM内核采用精简指令集结构(RISC,Reduced Instruction Set Computer)体系结构。RISC技术产生于上世纪70年代。其目标是设计出一套能在高时钟频率下单周期执行、简单而有效的指令集,RISC的设计重点在于降低硬件执行指令的复杂度,这是因为软件比硬件容易提供更大的灵活性和更高的智能。与其相对的传统复杂指令级计算机(CISC)则更侧重于硬件执行指令的功能性,使CISC指令变得更复杂。 RISC的设计思想主要有以下特性。 · Load/Store体系结构。 Load/Store体系结构也称为寄存器/寄存器体系结构或者RR系统结构。在这类机器中,操作数和运算结果不是通过主存储器直接取回而是借用大量标量和矢量寄存器来取回的。与RR体系结构相反,还有一种存储器/存储器体系结构,在这种体系结构中,源操作数的中间值和最后的运算结果是直接从主存储器中取回的。这类机器的缩写符号是SS体系结构。 · 固定长度指令。 固定长度指令使得机器译码变得比较容易。由于指令简单,需要更多的指令来完成相同的工作,但是随着存储器存取速度的提高,处理器可以更快地执行较大代码段(即大量指令)。 · 硬联控制。 RISC机以硬联控制指令为特点,而CISC的微代码指令则相反。使用CISC(常常是可变长度的)指令集时处理器的语义效率最大,而简单指令往往容易被机器翻译。像CISC那样通过执行较少指令来完成工作未必省时,因为还要包括微代码译码所需要的时间。因此,由硬件实现指令在执行时间方面提供了更好的平衡。除此之外,还节省了芯片上用于存储微代码的空间并且消除了翻译微代码所需的时间。 · 流水线。 指令的处理过程被拆分为几个更小的、能够被流水线并行执行的单。在理想情况下,流水线每周期前进一步,可获得更高的吞吐率。 · 寄存器。 RICS处理器拥有更多的通用寄存器,每个寄存器都可存放数据或地址。寄存器可为所有的数据操作提供快速的局部存储访问。 采用RISC架构的ARM微处理器一般具有如下特点: 支持Thumb(16位)/ARM(32位)双指令集,能很好的兼容8位/16位器件。Thumb指令集比通常的8位和16位CISC/RISC处理器具有更好的代码密度; ● 指令执行采用3级流水线/5级流水线技术; ● 带有指令Cache和数据Cache,大量使用寄存器,指令执行速度更快。大多数数据操作都在寄存器中完成。寻址方式灵活简单,执行效率高。指令长度固定(在ARM状态下是32位,在Thumb状态下是16位); ● 支持大端格式和小端格式两种方法存储字数据; ● 支持Byte(字节,8位)、Halfword(半字,16位)和Word(字,32位)三种数据类型。 ● 支持用户、快中断、中断、管理、中止、系统和未定义等7种处理器模式,除了用户模式外,其余的均为特权模式; ● 处理器芯片上都嵌入了在线仿真ICE-RT逻辑,便于通过JTAG来仿真调试ARM体系结构芯片,可以避免使用昂贵的在线仿真器。另外,在处理器核中还可以嵌入跟踪宏单ETM,用于监控内部总线,实时跟踪指令和数据的执行; ● 具有片上总线AMBA(Advanced Micro-controller Bus Architecture)。 AMBA定义了3组总线:先进高性能总线AHB(Advanced High performance Bus);先进系统总线ASB(Advanced System Bus);先进外围总线APB(Advanced Peripheral Bus)。通过AMBA可以方便地扩充各种处理器及I/O,可以把DSP、其他处理器和I/O(如UART、定时器和接口等)都集成在一块芯片中; ● 采用存储器映像I/O的方式,即把I/O端口地址作为特殊的存储器地址; ● 具有协处理器接口。ARM允许接16个协处理器,如CP15用于系统控制,CP14用于调试控制器; ● 采用了降低电源电压,可工作在3.0V以下;减少门的翻转次数,当某个功能电路不需要时禁止门翻转;减少门的数目,即降低芯片的集成度;降低时钟频率等一些措施降低功耗; ● 体积小、低成本、高性能。

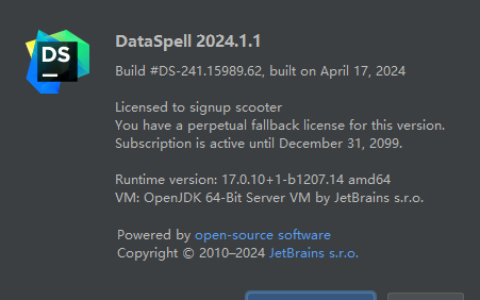

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/83786.html