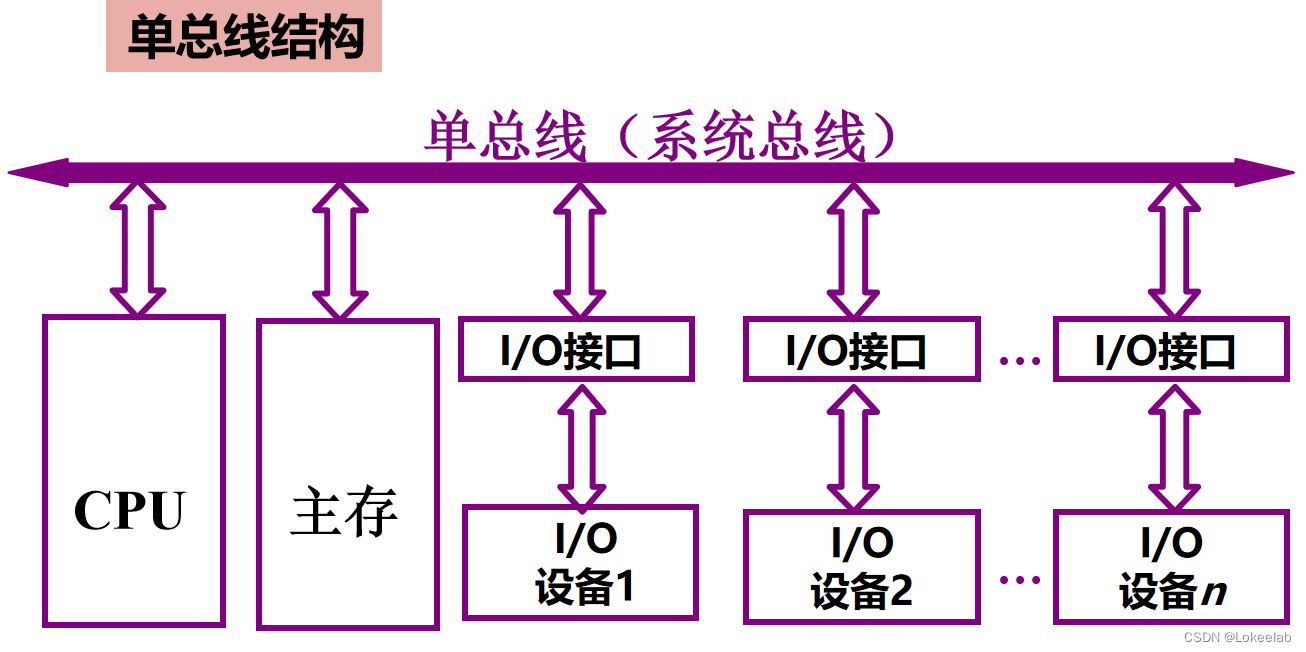

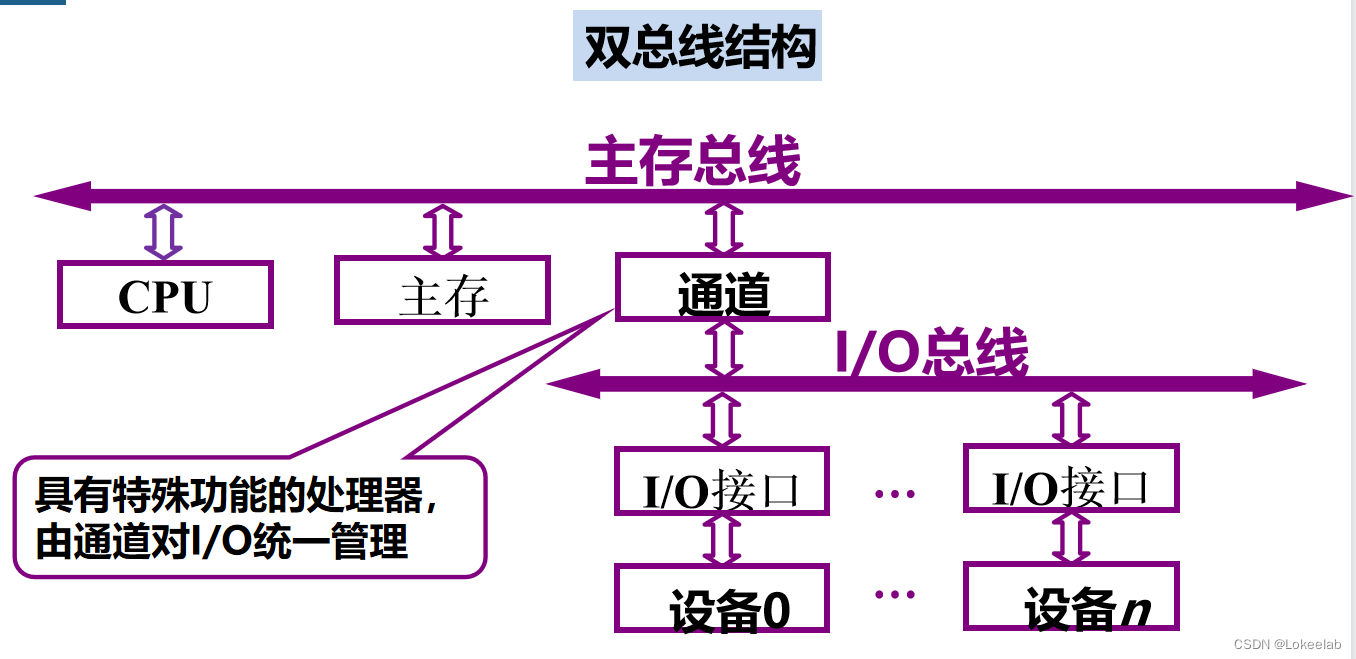

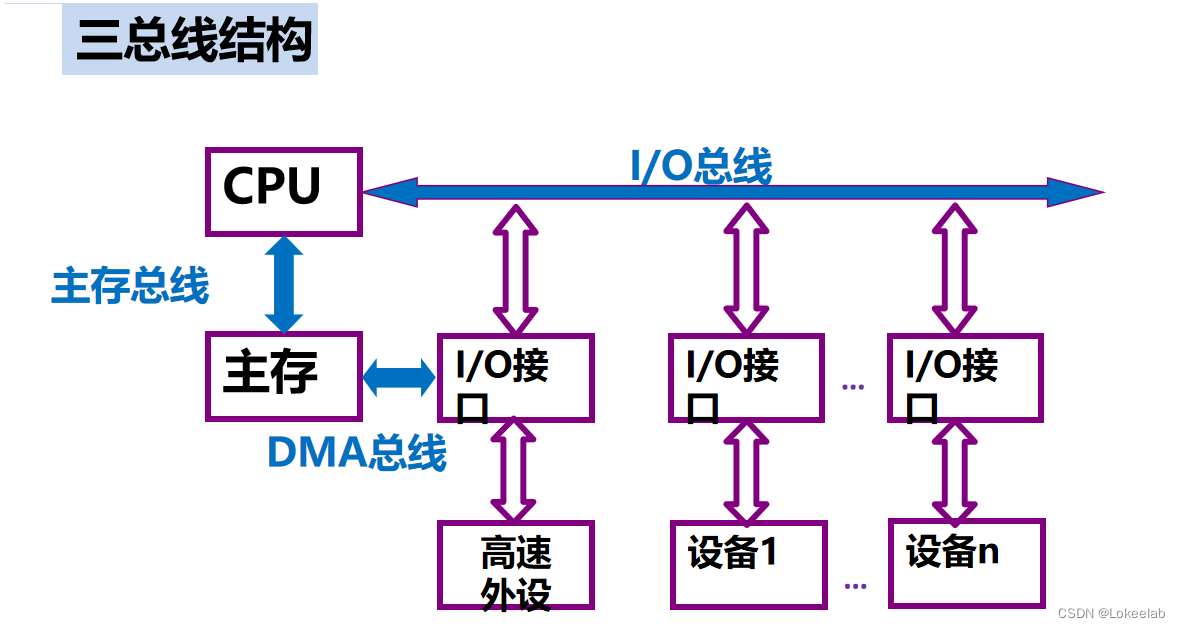

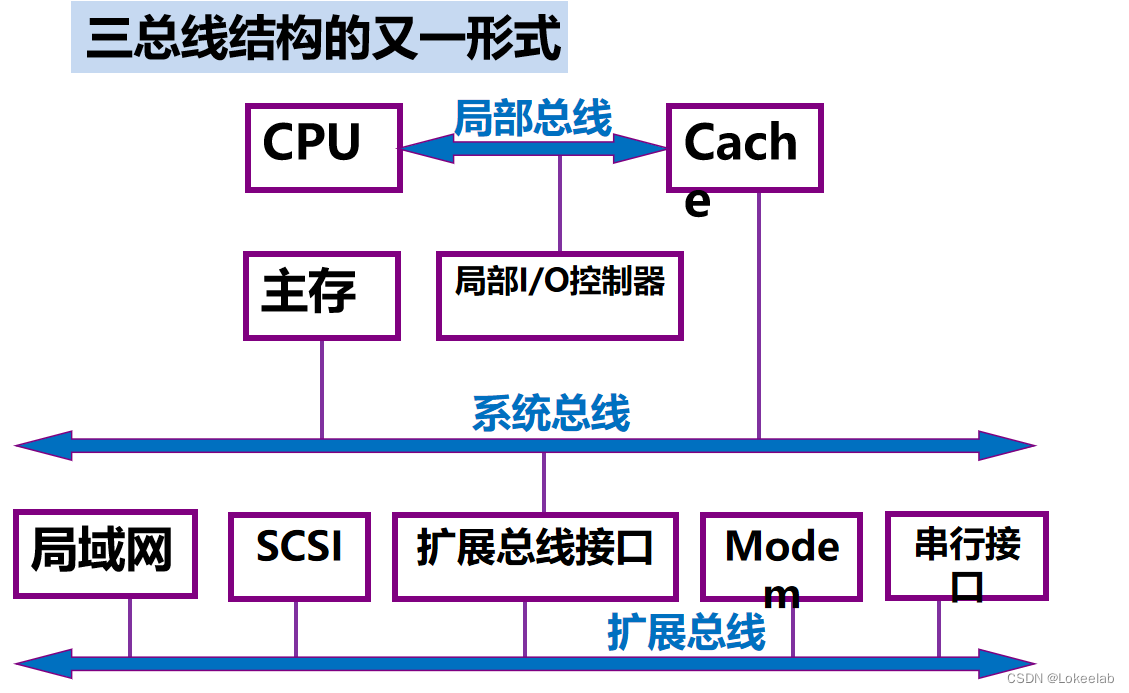

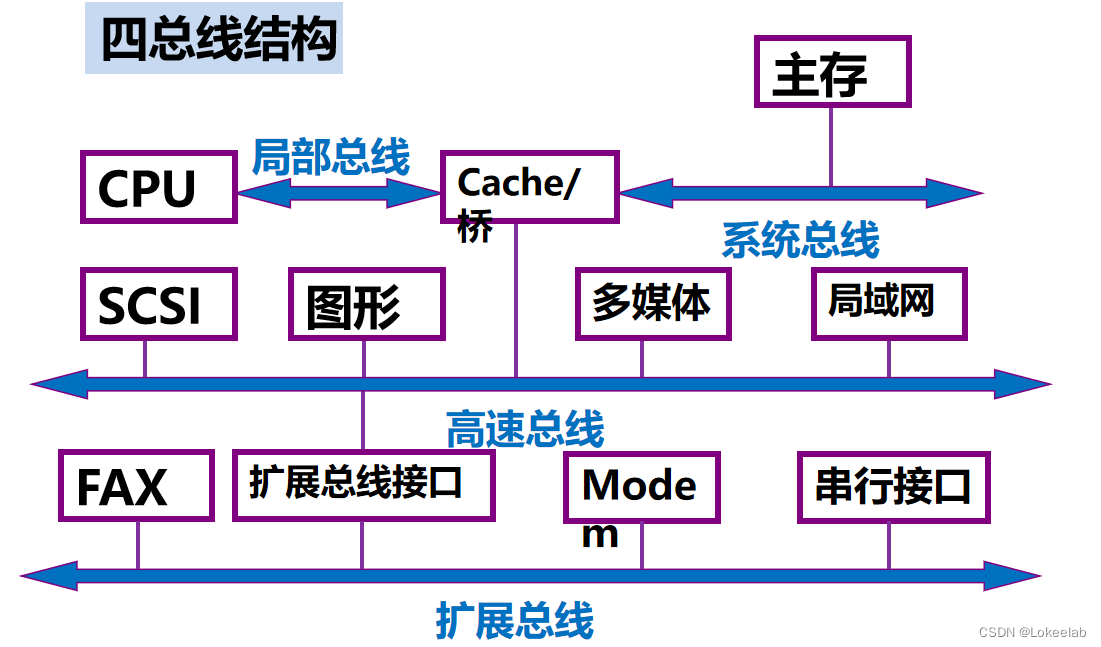

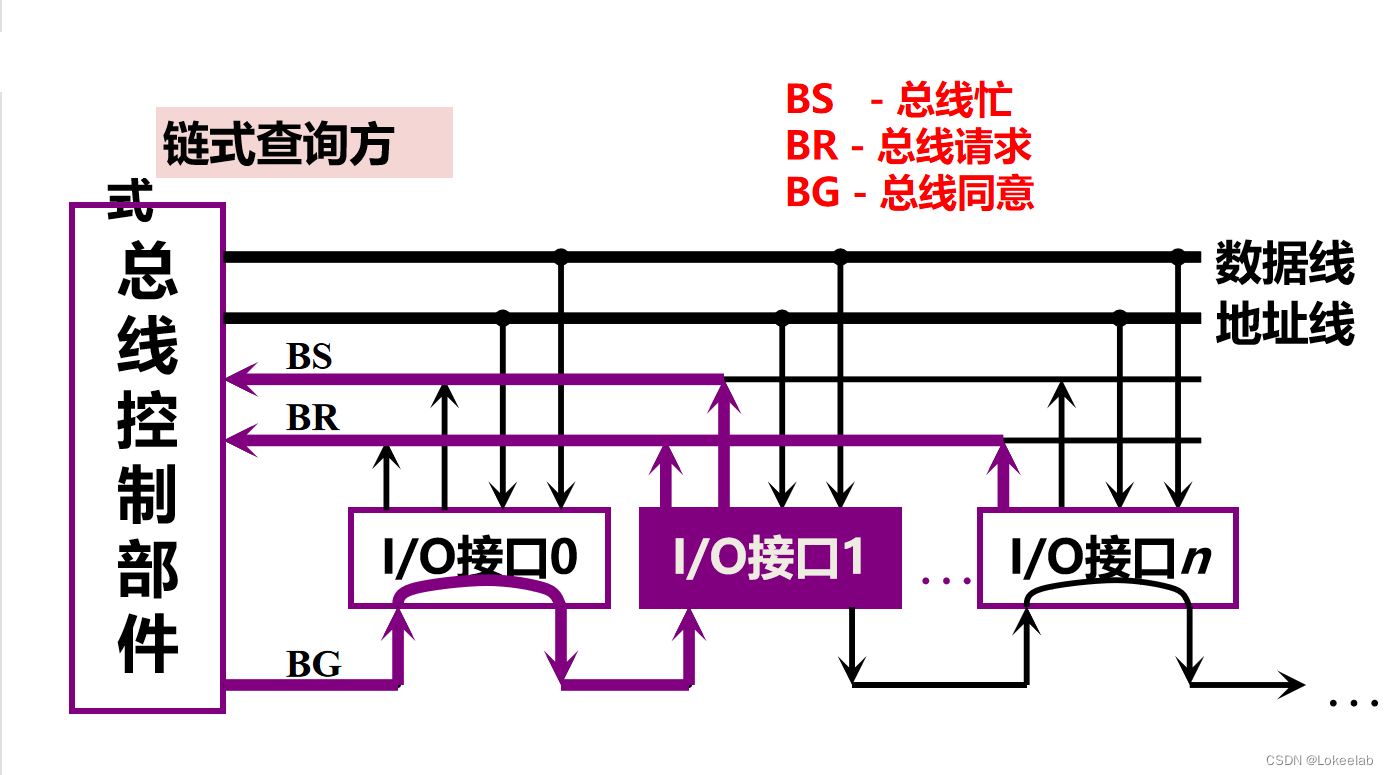

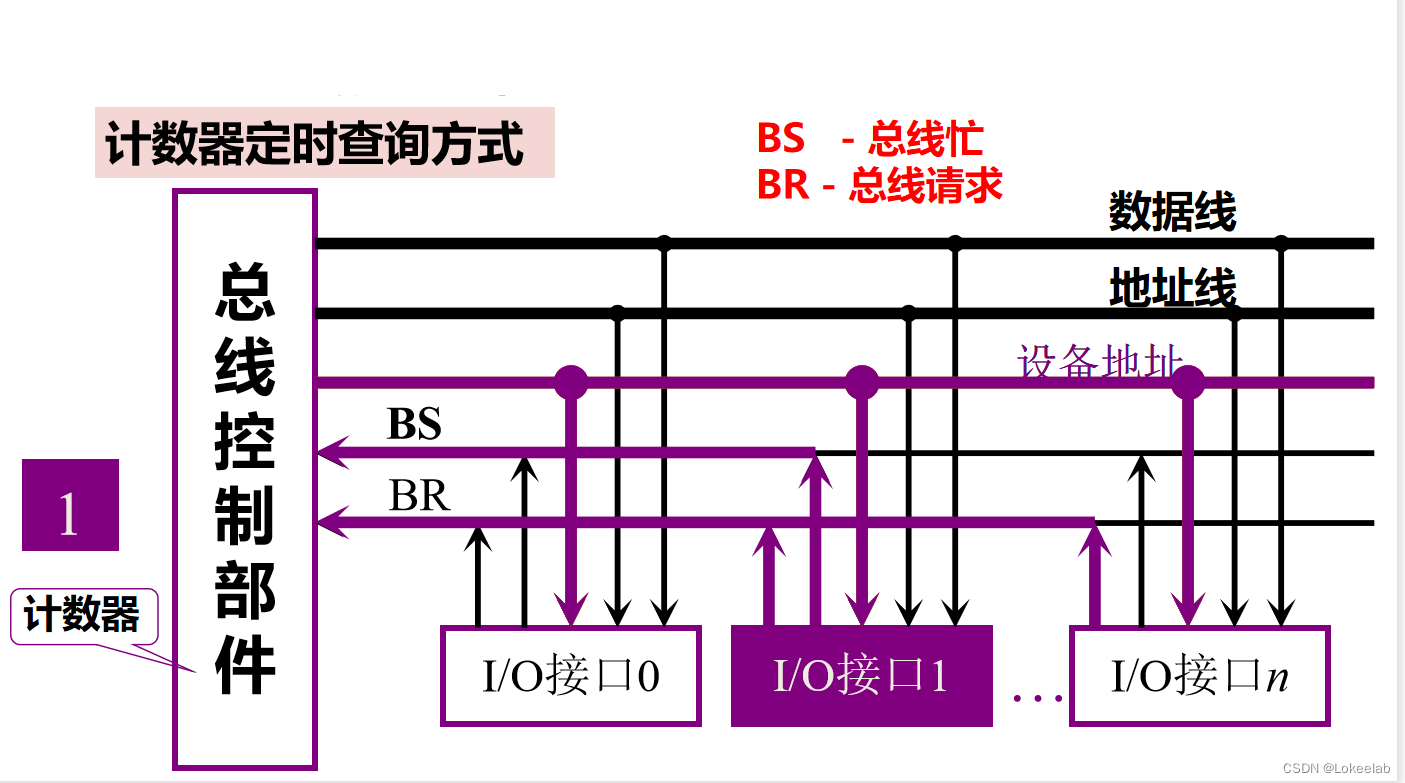

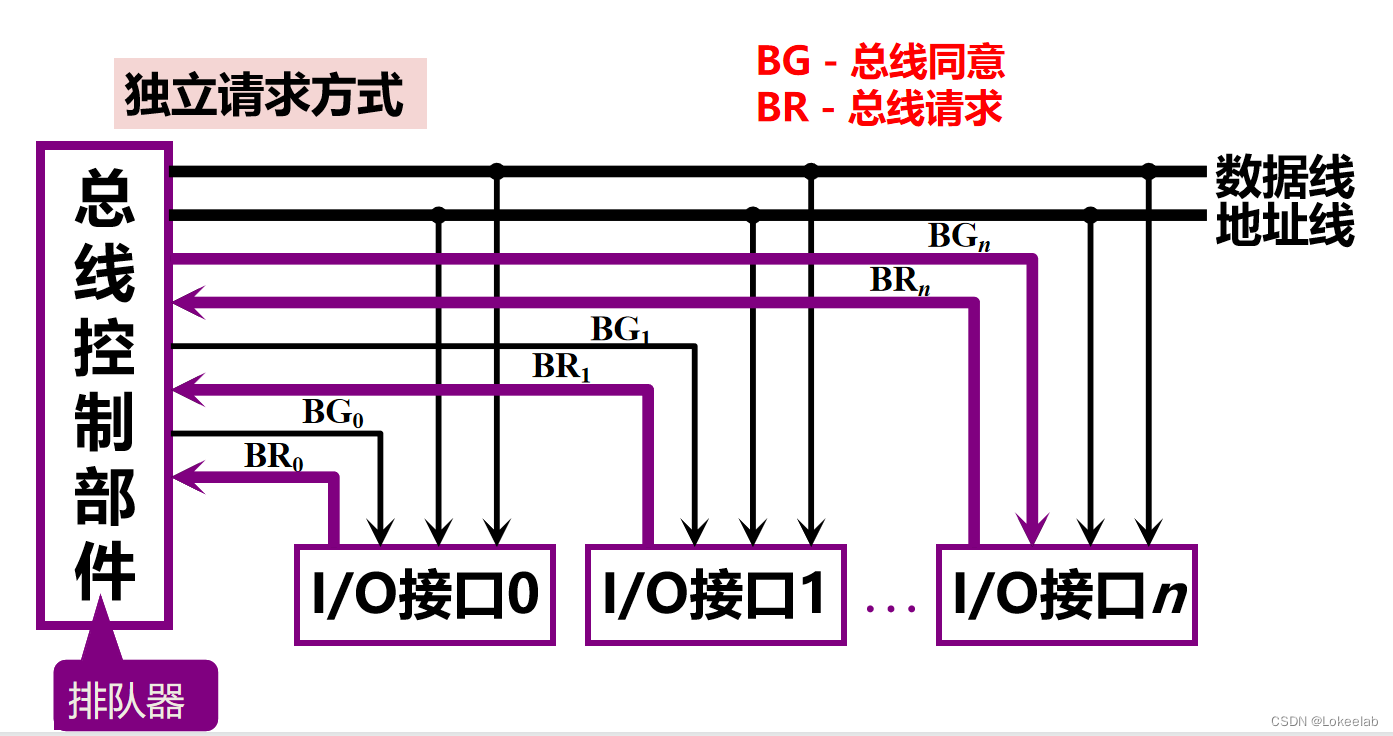

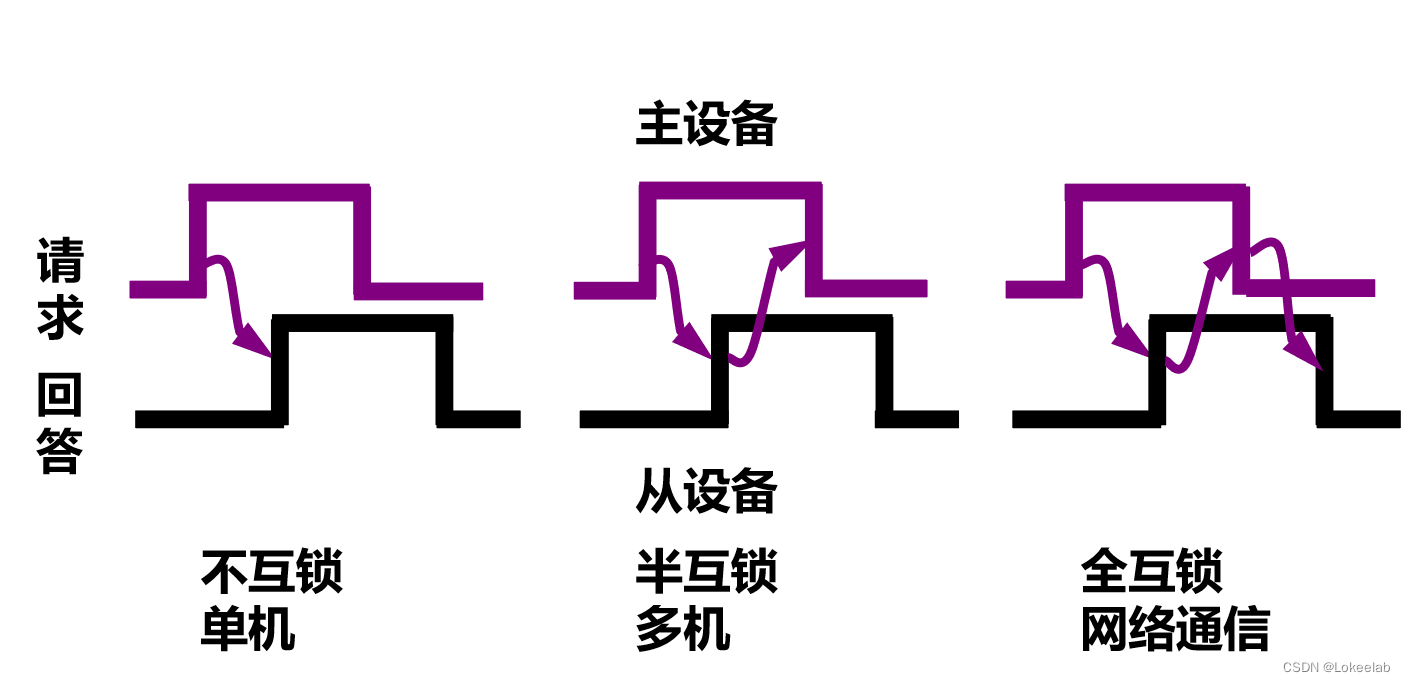

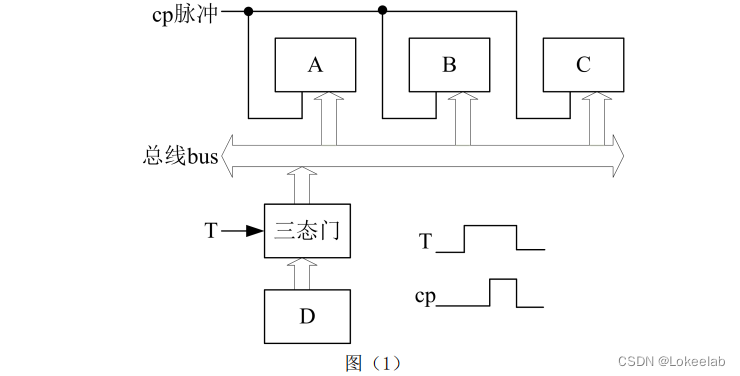

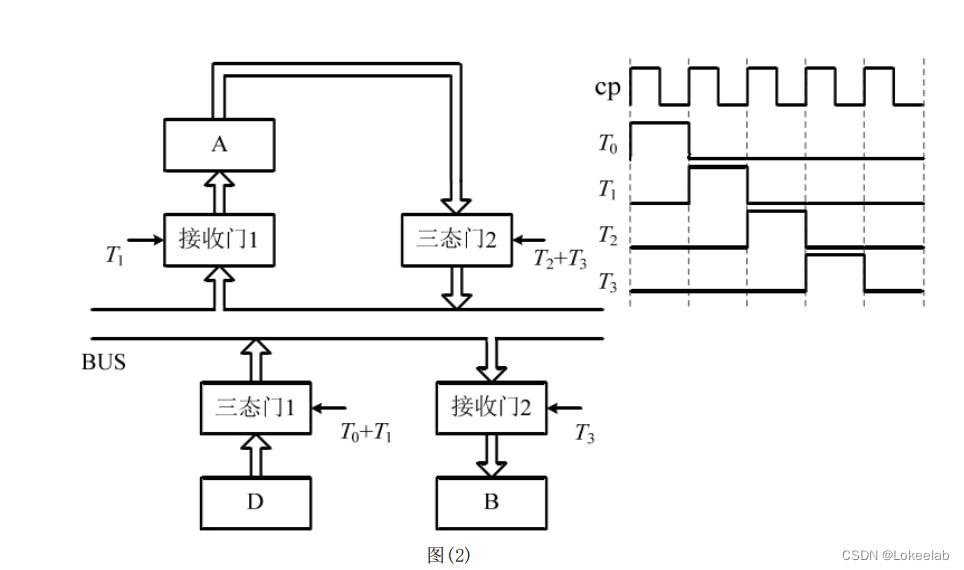

计算机组成原理课后答案(唐朔飞第三版) 第三章 计算机组成原理课后答案(唐朔飞第3版) 第3章 系统总线 教材课后思考题与习题: 3.1 什么是总线?总线传输有何特点?为了减轻总线负载,总线上的部件应具备什么特点? 总线:连接多个部件(模块)的信息传输线,是各部件共享的传输介质。 总线传输特点:某一时刻,只允许有一个部件向总线发送信息,而多个部件可以同时从总线上接收相同的信息。 为了减轻总线上的负载,各种 I/O 设备要通过 I/O 接口接在总线上,而且还要通过三态门挂在总线上,没有数据交换时置成高阻态。 3.2 总线如何分类?什么是系统总线?系统总线又分为几类,它们各有何作用,是单向的,还是双向的,它们与机器字长、存储字长、存储单有何关系? 总线分类: 按数据的传输方式: 分为并行传输总线和串行传输总线按使用范围: 分为计算机总线、测控总线、网络通信总线按连接部件: 片内总线、系统总线、通信总线系统总线: 指CPU、主存、I/O设备(通过I/O接口)各大部件之间的信息传输线。 按照系统总线传输信息的不同,又可分为三类:数据总线、地址总线和控制总线: 数据总线: 用来传输各功能部件之间的数据信息,它是双向传输总线,其位数与机器字长、存储字长有关,一般为8位、16位或32位。 地址总线: 用来指出数据总线上的源数据或目的数据在主存单的地址或 I/O设备的地址。单向传输,其位数与存储单的个数有关(几次幂的关系)。 控制总线: 用来发出各种控制信号的,对任意控制线而言,是单向的。与机器字长、存储字长、存储单无关。 3.3 常用的总线结构有几种?不同的总线结构对计算机的性能有什么影响?举例说明。 单总线结构:

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/35585.html