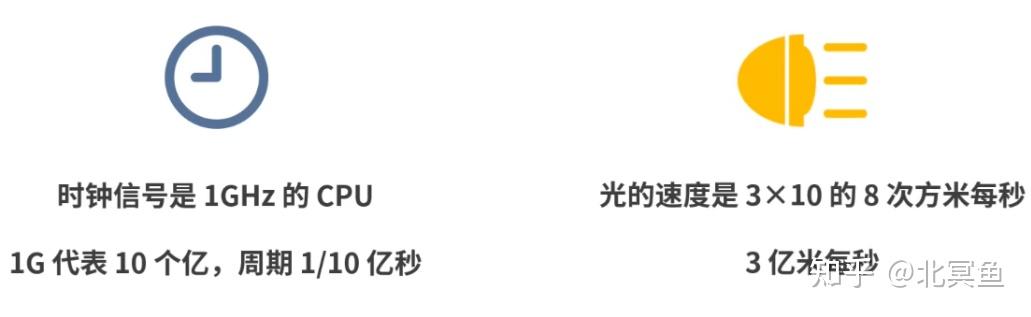

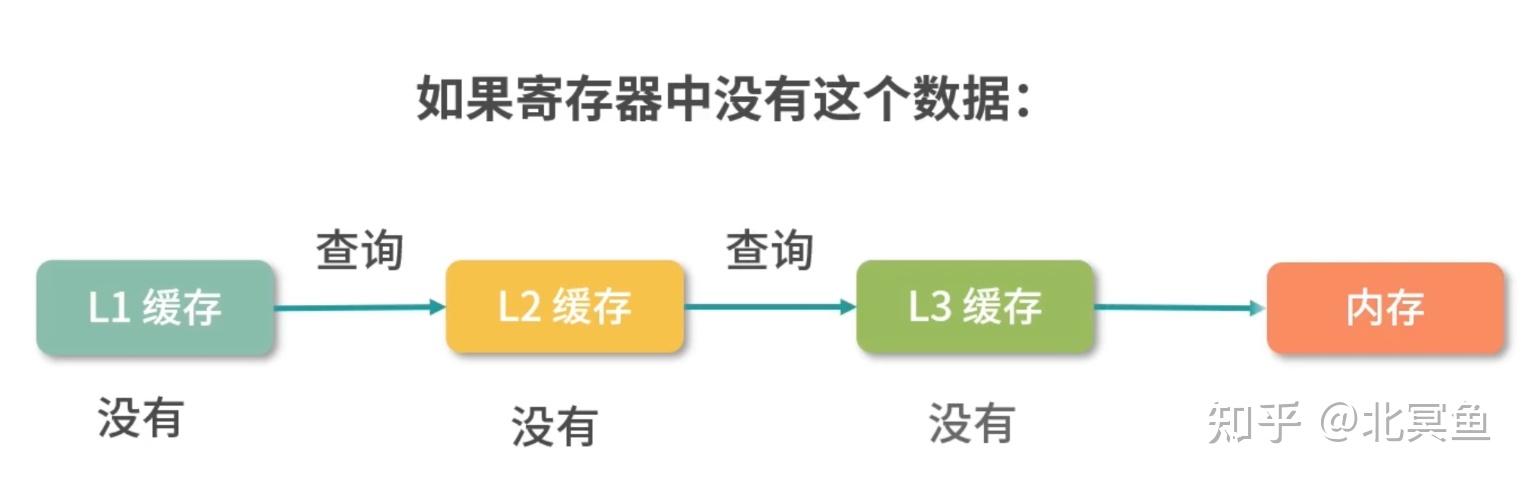

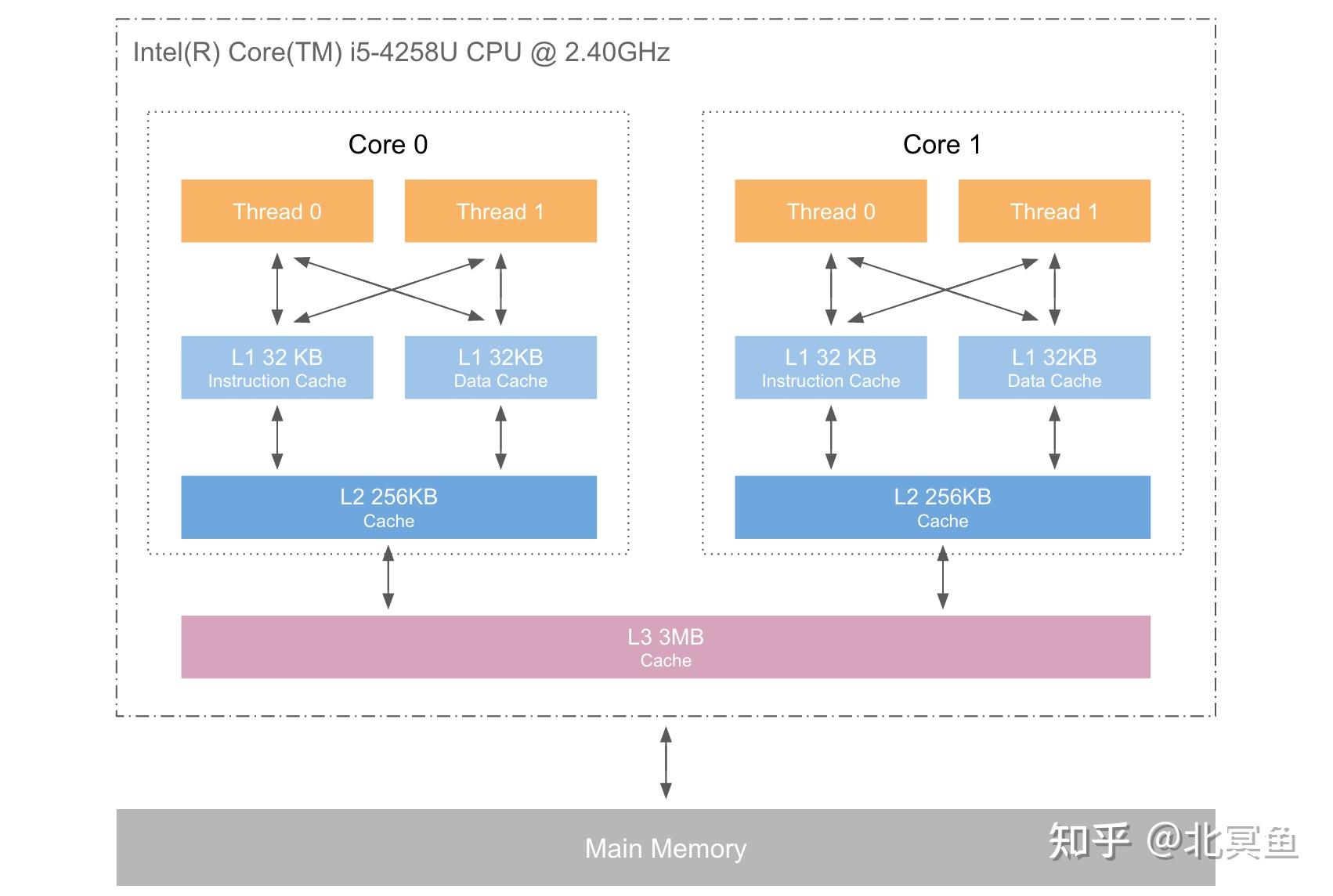

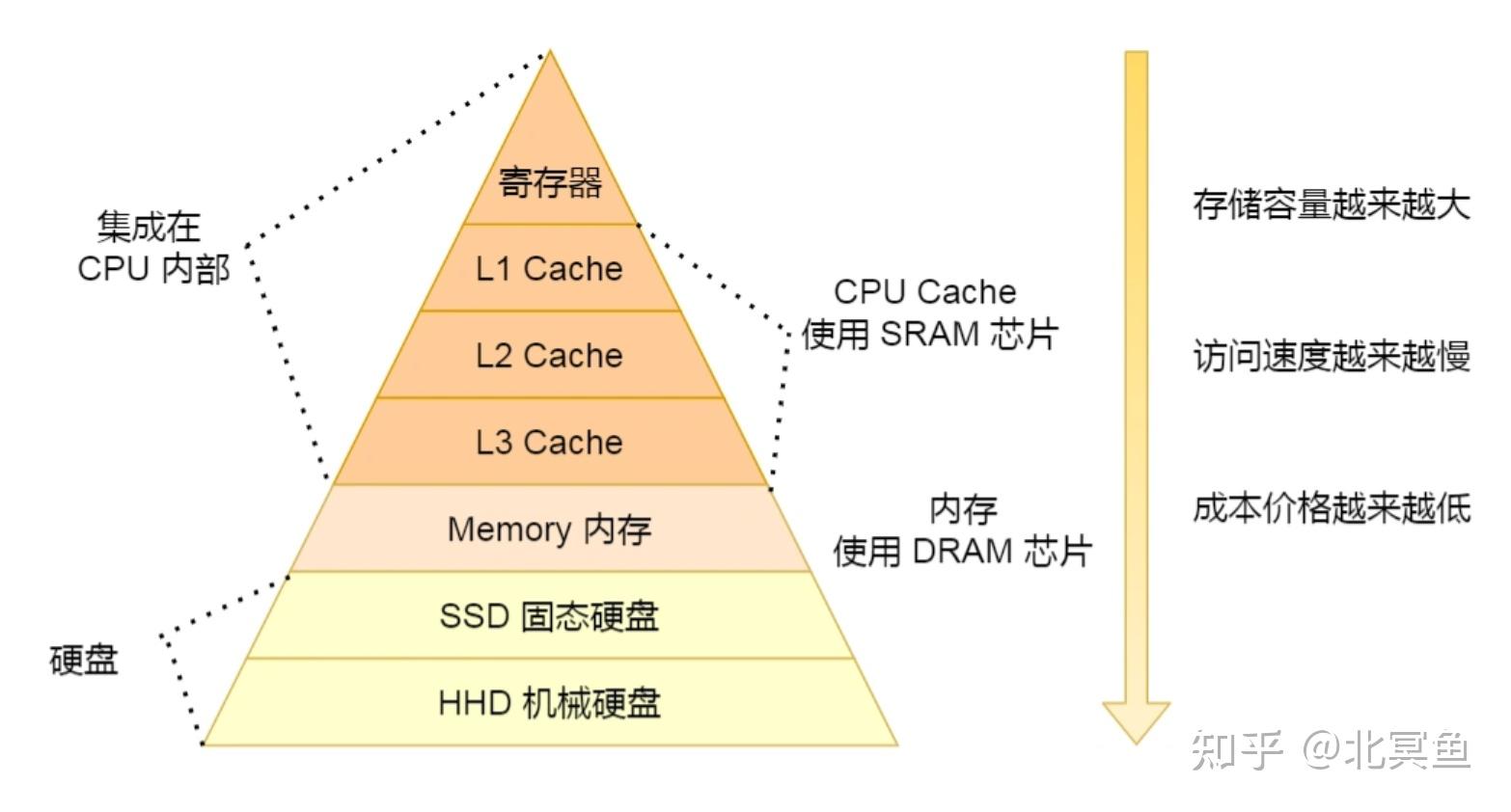

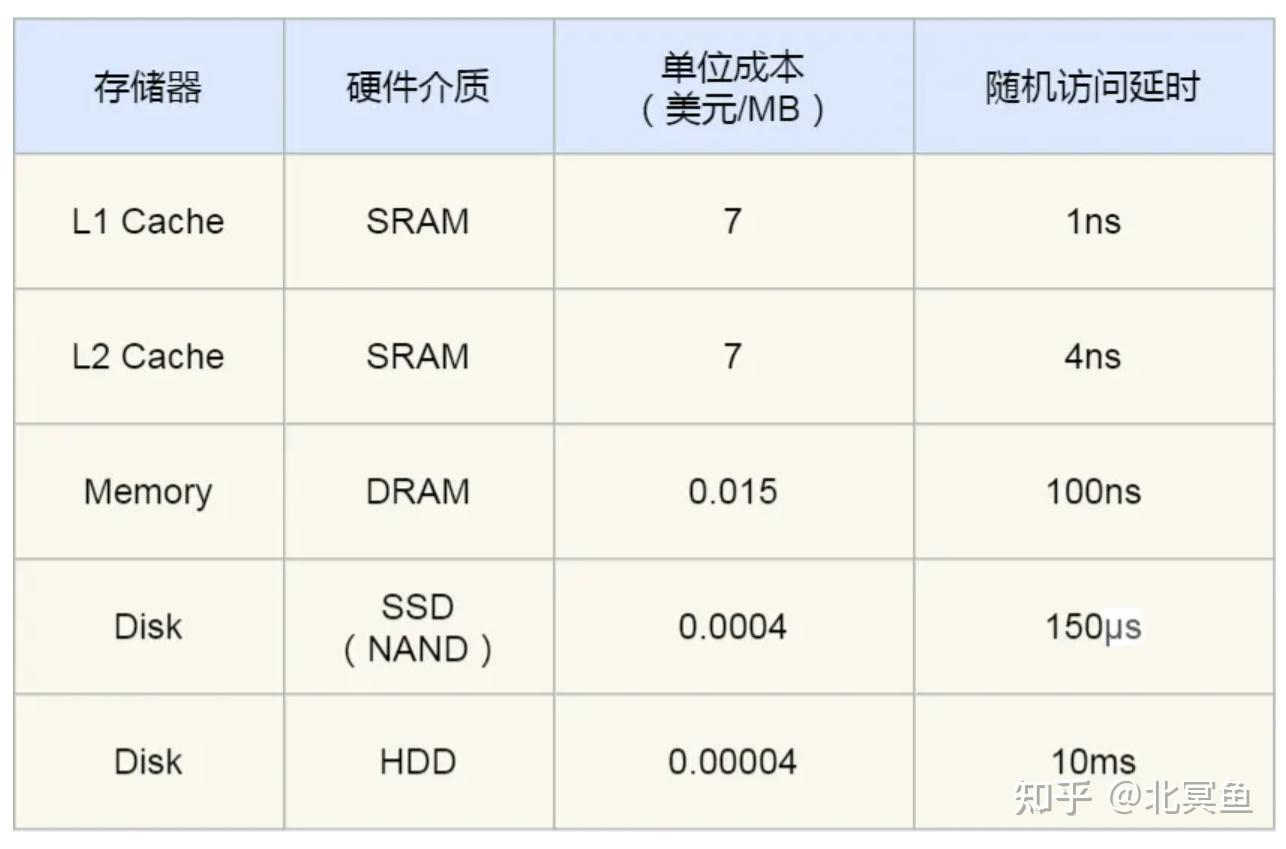

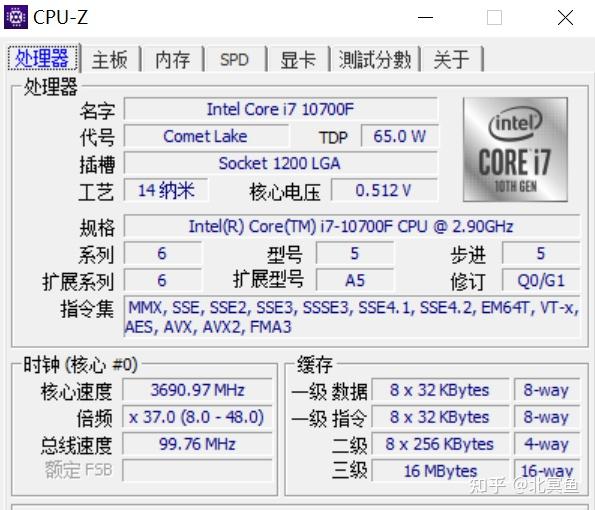

计算机系统:存储器分级 1、为什么会有存储器分级策略? 从需求上讲,我们希望存储器速度快、体积小、空间大、能耗低、散热好、断电数据不丢失。但在现实中,我们往往无法把所有需求都实现。 下面我们举几个例子,带你深入体会一下,比如:如果一个存储器的体积小,那它存储空间就会受到制约。如果一个存储器电子件密度很大,那散热就会有问题。因为电子件都会产生热能,所以电子件非常集中的 CPU,就需要单独的风扇或者水冷帮助电子件降温。如果一个存储器离 CPU 较远,那么在传输过程中必然会有延迟,因此传输速度也会下降。 大多数人的认知里,光速是很快的,而信号又是以光速传输的。既然光速这么快,那信号的延迟应该很小才对。但事实并不是这样,比如时钟信号是 1GHz 的 CPU,1G 代表 10 个亿,因此时钟信号的一个周期是 1/10 亿秒。而光的速度是 3×10 的 8 次方米每秒,就是 3 亿米每秒。所以在CUP的一个时钟周期内,光只能前进 30 厘米。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/51082.html