硬件测试实习生笔试试题 1、1、请简单阐述你所了解的local bus。如果设计或使用过local bus,请举例说明。答:一:Local Bus总线又称为 CPU总线,根据高低位地址线序的差异,又可分为Motorola CPU总线和In tel CPU总线。古老的 CS51单片机就是In tel CPU总线的典型代表,而我们常用的Power PC就是 Motorola CPU总线架构,它是从 60X总线衍变过来的(60X总线支持64、32、 16、8四种可选位宽模式),由于Local Bus总线是直接从60X总线上通过桥片分出来的,所 以它和60X总线是同步同频的,进行数据数据读写时与60X总线共享带宽,不需要内核提供 2、额外的处理。如下图所示:SDRMZDDRZ/ CHHER I/ODDR3 PORT PORT16KByteInstruction Cacheim呼 BUPower PC CPU CORECPU IC16KByteData Cachedmwu50X to LogqIBus ;BridgeLocal MS:Local BUS PORT二:数据/地址复用总线解复用后的Device Bus叫Local Bus, Device Bus总线一般采用数据/地址线复用的形式,通常为32位宽,使用时需要将总线的数据和地址分离出来 再分别接到目标器件的数据和地址端口,如连接到低速设备时还需要通过 Buffer起来 3、来进行驱动和隔离。在早期的设计中,通过用信号锁存器来分离总线中的数 据和地址(如经典锁存器 SN74LVC16373)不过现在基本上都是通过逻辑器件 CPLD来进行解复用的。利用锁存器 373对Device Bus总线数据/地址解复用原理 如下图所示在上图中,L_ALE是地址锁存信号,低电平有效,当L_ALE出现一个低电平脉冲时,锁存器的输入端口对LAD31:0信号进行采样、锁存并从输出端口输出,直到下一个L_ALE低电平脉冲到来时,其输出状态才发生改变,Device Bus总线在输出地址信号时将L_ALE信号驱动为低电平,输出数据信号时,将L_ALE驱动为高电平,锁存器正式利用这个特点轻松实 4、 现Device Bus总线上数据和地址的分离。三:Local Bus总线上的数据读写分为同步模式和异步模式。在同步模式下,钟信号供接收端和发送端共用,利用时钟信号的上升沿对数据进行采样, 等高速信号使用同步模式;异步传输模式下,不使用时钟信号对数据进行采样 是需要有系统参考时钟来产生时序的),而是利用片选信号 CS写使能信号号0E对数据进行采样,使用异步模式的器件有FLASH BOOTROM等。需要一个外部时SDRAM SSRAM(芯片内部还 WE和读使能信2、请描述以下local bus时序的逻辑功能图或者写一个test bench为该时序图添加激励(IcIkOIcIkO(33MHz)lb 5、a0:31lbd0:15lalelbctllcslwe可以不要求和其他信号同步),可以使用VHDL或者Verilog HDL语言。lclk0:同步 local bus 时钟Lba:地址线Lbd:数据线Lale:锁存Lbctl: local bus 控制信号Lcs:片选Lwe:写信号答:逻辑功能-实现的是异步模式器件(FLASH BOOTROM)的写数据功能1 在异步模式下,lclk0:同步local bus时钟作为系统时序产生的参考时钟,不需要外部加时钟进行同步。2 Lbctl: local bus控制信号控制 60X总线选定local bus总线模式,Lbctl信号高电平有效。3 开始时La 6、le信号为低电平有效,锁存器的输入端口对LBA31:0信号进行采样、锁存并从输出端口输出,即锁存要写的地址,Lale信号为高电平时,锁存器实现Device Bus总线上数据和地址的分离,即为我们所讲的local bus模式。4 cs片选信号为低电平时有效,这时选中要写的器件,Lwe信号为低时,写使能起作用,对器件进行写数据,所以片选信号和写使能信号结合对器件进行写数据。10ns 的脉冲。3、请介绍一款示波器,并分别说明如何测量电源纹波、4、PC上的串口引脚定义是什么如果需要制作连接2个PC串口互联的线缆,那么线缆应该如何定义答:串口的号码,相对应的信号以及功能如下:1 载波检测 (DCD);2 7、 接受数据 (RXD);3 发出数据 (TXD); 4数据终端准备好 (DTR);5 信号地线 (SG);6 数据准备好 (DSR); 7 请求发送 (RTS);8 清除发送 (CTS;)9 振铃指示 (RI) 信号的工作原理是这样的:首先发送数据 TXD DTE向DCE DTE发送串行数据; 然后接收数据 RXD DTE接受DCE DTE串行数据;请求发送RTS DTE向 DCE DTE青求DCE将线路切换到发送方式; 允许CTS DT歿受DCE DCE告诉DTE线路已接通可以发送信号; 数据设备准备好 DSR DTE;载波检测DCE DTE接受到DCE此时DCE接收到远程载波;数据终端准备好 DTR DTE通知 DCE DTEt备好; 至此串口引脚信号准备完毕,可以正常工作。5、你对硬件(或逻辑)开发和测试的理解 测试就是学习的过程 , 对硬件的理解更深刻 , 测试的过程就是解答的过程, 硬件的为 什么,其实我们的搞明白什么是测试, 测试并不像开发什么都得去实现, 一行一行代码去做, 每个电路都懂得设计。 其实主要是对整个系统, 从电路到系统实现上都要有建树 (要

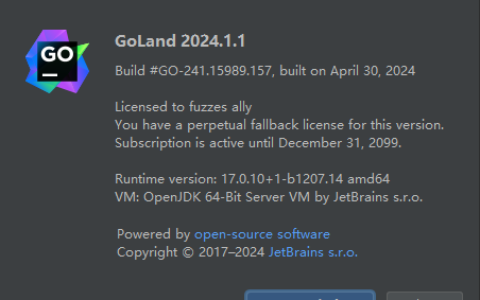

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/35242.html