嵌入式有哪些专业名词? ▎ A ASIC(专用集成电路)专用集成电路。一个在一个芯片上定制设计的硬件。 address bus (地址总线)一个连接处理器与所有外设的,用来通讯的电子线路集。地址总线被处理器用来选择在特定外设中的存储器地址或寄存器。如果地址总线有n条电子线路,处理器能唯一寻址高达2^n的地址空间。application software(应用软件)用来描述一个特定的嵌入式项目中的某一软件模块。应用软件不象可重用的交叉嵌入式平台,只是因为每一个嵌入式系统有不同的应用软件。assembler(汇编编译器) 一个能把人可读的汇编语言程序转换到处理器可理解和运行的机器指令的软件开发工具。assembly language(汇编语言)一种人可读的处理器指令集的形式。大多数处理器相关的功能必须用汇编语言编写。 ▎ B BSP(板卡支持包)binary semaphore(二信号)一种只有两种状态的信号。也叫互斥信号。board support package(板卡支持包)软件包的具有平台依赖性的那一部分。典型地,板卡支持包的样例源程序由包开发者提供。样例源程序必须能在需要时被修改、编译并与软件包的剩下的部分连接起来。bond-out processor (外合处理器) 一种特殊版本的处理器,它有一些,内部的信号能传达到外置的针脚上。一个外合处理器绝大多数情况下只用在模拟器上,从来不会被特意用在产品系统上。Breakpoint (断点)一个在程序中的地址,在那里程序的执行被停止,并且处理器的控制转换到了除错程序。大多数除错工具提供增加与删除一个断点的机制。 ▎ C CISC(复杂指令集计算机)复杂指令集计算机。对一种处理器架构的描述。CISC处理器一般产生变长的指令,多种地址格式,并且仅仅有少量的通用寄存器。Intel的80×86家族是是典型的CISC处理器。相对于RISC而言。CPU(中央处理器) 中央处理器。处理器中执行指令的那一部分。Compiler(编译器) 把高级编程语言程序转换到只有特定的处理器能了解和执行的机器指令的一种软件开发包。context (上下文) 处理器当前的状态和标志。context switch(上下文切换)在多任务操作系统中我一个任务切换到另一个的过程。上下文切换包括保存正在运行的任务的上下文和恢复早先保存的另一个任务的上下文。做这个工作的一段代码必须具有处理器特权。counting semaphore(计数信号)一种用来跟踪多个相同类型资源的信号灯。仅仅在所有可用的资源都被用完了时才阻塞。相对二信号而言。critical section(临界段) 一段必须按次序执行的代码,并且不能被中断,否则不能保证软件正确地操作。参照:竞争状况。cross-compiler(交叉编译器)一个运行在不同的平台上的编译器,其中之一能产生目标代码。交叉编译器在主机上运行并且产生目标机的目标代码。 ▎ D DMA(直接内存访问)直接内存访问。一种直接在两个外设(通常是内存和I/O设备)之间进行数据传输的技术,它只要处理器最少的介入。DMA传输由叫DMA控制器的第三方外设进行管理。DRAM(动态随机访问存储器)动态随机访问存储器。一种RAM,存储在其设备中的数据被定期刷新时才能保存它的内容。刷新周期一般由一个叫DRAM控制器的外设完成。Data bus(数据总线) 连接处理器与所有外设进行通讯的电子线路集。当一个处理器想去写(读)某一特定外设中的存储器地址或寄存器中的内容时,处理器设置地址总线并在数据总线上接收(传输)内容。Deadline(死线)一个特定计算必须被完成的时间。请看实时系统。Deadlock(死锁)一种不希望出现的软件状态,在这个状态下,所有的任务因为等待一个只有在这些被阻塞任务之一才能产生的事件而被阻塞。如果死锁发生,唯一解决的方法是重启动硬件。但是,通过可靠的软件设计实践活动通常可以防止死锁的发生。debug monitor(除错监视程序)嵌入式软件被特殊设计来作为除错工具的一部分。它一般被放在ROM中,通过串口或网络与除错器进行通讯。除错监视程序提供一个简单的命令集来显示和内存地址和寄存器、建立和移除断点,并且运行你的程序。除错监视器组合这些简单的命令去实现象程序下载各单步调试等高端的请求。Debugger(除错器)一个软件开发工具,被用来对嵌入式软件进行测试和除错。除错器在宿主机上运行并且通过串口或网络连接到目标机上。你能使用除错器下载软件到目标机并直接运行。你也可以设置断点并检查特定内存地址或寄存器的内容。device driver(设备驱动程序)一个软件模块,它隐藏特定外设的细节并提供高级的外设编程接口。device programmer(设备编程器)一种用来对不挥发内存和其他电可编程设备进行编程的工具。典型地,可编程设备被插到设备编程器的接口上,接着内存缓存器中的内容被传送到它里面。digital signal processor(数字信号处理器) 一种类似于微处理器的的设备,不同的是它内部的CPU被优化,用于特定的应用,如离散信号处理。除了标准的微处理器指令外,DSP常常支持复杂指令集去非常快地完成通用的信号处理计算。通用DSP家庭是TI的320Cxx和Motorola的5600x系列。 ▎ E EEPROM(电可擦的,可编程的只读存储器)可擦的,可编程的只读存储器。一种ROM能被电擦除。EPROM(可擦的,可编程的只读存储器)一种可用紫外线擦除的存储器。一次擦除后,EPROM可以在设备编程器的帮助下被重编程。embedded system(嵌入式系统) 计算机硬件和软件的结合体,或许还加上机械等其他部分,被设计来完成专门的功能。在一些情况下,嵌入式系统是一个大的系统或产品的一部分,就象汽车上的防抱死装置。与通用计算机相对。Emulator(仿真器) 在线仿真器的简写。一个在你的目标板上放置仿真的处理器的调试工具。仿真器经常和一目标处理器的一种“外合”版本合在一起,这个版本的的处理器充许你运行程序时观察和记录它的内部状态。Executable(可执行的) 一个包含准备在目标机上运行的目标代码的文件。放置目标代码到ROM中或通过调试工具下载。 ▎ F Firmware(固件)是作为目标代码存贮在ROM中的嵌入式软件。这个名字在数字信号处理器的用户中相当流行。 flash memory (闪存) 一种RAM-ROM的混血儿,它能在软件的控制下被擦除和重写。一些设备被分成叫段组的块,能个别地可擦。闪存用在需要很便宜的非易失数据存贮器的地方,一个大容量的闪存甚至被用作磁盘驱动器。 ▎ G general-purpose computer(通用计算机) 当作通用计算平台的计算机硬件与软件的组合。例如,PC。相对于嵌入式计算机。 ▎ H HLL 查阅高级语言。 Heap(堆) 一块被用作动态内存分配的内存区域。调用malloc和free、C++的操作符new、delete在运行时进行堆的操作。high-level language(高级语言)一种语言,象C或C++,是处理器独立的。当在高级语言上编程时,不需要考虑特定处理器的细节,只用关心算法和应用。Host(主机)一台通用计算机,它通过串口或网络连接与目标机通讯。这处名词一般用来区别调试程序运行的计算机和被开发的嵌入式系统。 ▎ I ICE 在线仿真器。查阅仿真器。I/O(输入/输出)输入/输出。处理器与外界的交互界面。最简单的例子是开关(输入)和发光二级管(输出)。I/O device(IO设备)一种介于处理器和外界之间的硬件设备。一般的实例是开关、LED、串口和网络控制器。I/O map(I/O映射)一张包含每个外设的名字和地址的表格或图表,可由处理器在I/O空间中设定地址。I/O映射对得知目标机情况非常有利。I/O space(I/O空间) 一个由处理器提供的特殊内存区域,一般为为I/O设备的附件保留。在I/O空间的内存位置和寄存器只能通过特殊的指定进行访问。例如:80X86家族的处理器有叫做in / out的特殊的I/O空间指令。相对内存空间而言。ISR(中断服务程序) 包含下一条要执行指令地址的处理器中的寄存器。也叫程序计数器。Interrupt(中断)一个从外设到处理器的异步电信号。当外设发出这个信号,我们说一个中断发生。当一个中断发生,当前的处理器状态被保存并且中断服务程序开始运行。当中断服务程序退出,对处理器的控制权转到先前运行的那个软件上。interrupt latency(中断延迟)在中断发生和相关的中断服务程序运行之间的时间长短。interrupt service routine(中断服务程序) 响应特定中断而运行的一小段软件。interrupt type(中断类型) 和每一个中断相关联的唯一数字。interrupt vector (中断向量)中断服务程序所在的地址。interrupt vector table(中断向量表) 一个表格,包含由中断类型决定的中断向量和索引。这个表格包含中断与中断服务程序之间的处理器的映射,必须由程序员进行初始化。intertask communication(进程间通讯)一种被用来在任务和中断服务程序之间共享信息和同步它们对共享资源访问的机制。大部分进程间通讯的建立的基石是信号灯和互斥。 ▎ K Kernel(内核)任何多任务操作系统的本质部分,内核仅仅包含调度程序和上下文切换进程。 ▎ L Linker(连接程序)一种能把一个或更多目标文件组合成可输入和输出的可重定位程序的开发工具。连接程序在所有的源文件都被编译或汇编之后运行。 Locator(定位程序) 一种分配物理地址给连接程序处理过的可重定位程序的软件开发工具。这是准备一个软件在嵌入式系统中运行的最后一步,并且结果文件叫做可执行的。在一些情况下,定位程序功能隐藏在连接程序中。logic analyzer(逻辑分析仪) 一种硬件调试工具,能捕获实时电信号的许多逻辑电平(0或1),逻辑分析仪在调试硬件问题和复杂的处理外设交互时相当有用。 ▎ M memory map(内存映射) 一个在内存空间中的,包含每个外设的名字和可由处理器设置的地址范围的表格或图表。内存映射有助于了解目标机情况。memory-mapped I/O(内存映射I/O) 一种日益流行的硬件设计方法,在这种方法中,I/O设备被放置在内存空间而不是I/O空间。从处理器的观点看,内存映射I/O设备看上去很象内存一样。memory space(内存空间) 一个处理器的标准地址空间。相对I/O空间。Microcontroller(微控制器) 微控制器很像微处理器。主要的差别在于微控制器被特殊设计用在嵌入式系统中。微控制器典型地包括CPU、内存(很小的RAM或ROM),还有其他的外设,它们在同一块芯片上。常见的例子是:8051、Intel80196、Motorola68HCxx系列。Microprocessor(微处理器) 一片包含通用CPU的硅片。常见的例子是:Intel80x86、Motorola 680×0系列。Monitor(监视器) 在这本书的上下文中,是指调试监视器。然而,第二个意思与任务间通讯相关联。在那个上下文中,监视器是高级同步机制的特性。Multiprocessing(多处理) 在单个的计算机系统中有多个处理器。被叫作“多处理器系统”的一般有公用的内存空间,处理器通过它们进行通讯和共享数据。另外,一些多处理器系统支持并行处理。Multitasking (多任务)伪并行运行的多个软件程序。每一个程序表现得像分开的“执行的线程”并且被看作是一个任务。操作系统通过分配处理器时间来模拟并行方式。Mutex(互斥) 表现互斥现象的数据结构,也被当作二信号灯。一个互斥基本上是一个多任务敏感的二信号,它能用作同步多任务的行为,它常用作保护从中断来的临界段代码并且在共享同步使用的资源。mutual exclusion(互斥现象)唯一访问共享资源的保证。在嵌入式系统中,共享的资源典型的有内存块或寄存器组。互斥现象能由使用信号灯或互斥完成。 ▎ N NVRAM 非易失的随机访问存储器。一种能在系统关机的情况下保持它的数据的RAM。NVRAM常常由SRAM和长寿命电池组成。 ▎ O OTP 处理器能读的操作码和数据。编译器、汇编器、连接器和定位器的输出文件都含有目标代码。 object file(目标文件)包含目标代码的文件。编译器或汇编器的输出。one-time programmable(一次可编程的) 任一可编程的设备,像PROM,仅仅能被最终用户编程一次。然而,这个术语一般被专有地使用在拥有片上PROM的微控制器上。opcode 一串被处理器验证过的二进制位的序列,它作为其指令集的一个子集。operating system(操作系统) 使多任务能够实现的一个软件。一个操作系统典型地由一个函数调用集、软件中断和定期时钟周期组成。一个操作系统负责决定哪一个任务在给定的时间将使用处理器,并且控制对共享资源的访问。Oscilloscope(示波器)一种硬件调试工具,它让你能观察到一个或更多电路上的电压。例如:如果一个特殊的中断发生,你可以用一个示波器去检测它。 ▎ P PROM(可编程只读存储器)可编程只读存储器。能被设备编程器写的一种ROM。这种内存设备可以被编程一次,所以它们有时被作为写一次或一次性编程设备来看待。parallel processing(并行进程)一种在单个计算机上运行两个或多个程序的能力。Peripheral (外设) 一种不同于处理器的硬件设备,常指内存或I/O设备。外设经常和处理器在一片芯片上,在这种情况下,它被称为集成外设。physical address(物理地址)当访问内存位置或寄存器时,在地址总线上的真实的地址。Preemptive(抢先)当一个高优先级的任务准备好时,充许正在运行的任务被挂起的调度策略被称为优先。无优先的调度策略更容易实现一些但适合在嵌入式系统中使用。Polling(轮询)一种硬件交互方法,不断读状态寄存器,直到设备进入等待状态。设备驱动程序不是轮询的就是中断驱动的,后一种越来越成为首选的。Priority(优先) 一个任务与其他任务相比的重要关系。priority inversion(优先转置)一种不希望发生的软件状态,在此状态一个高优先级任务因为等待访问一个那时不再使用的共享资源而被延迟。在所有的实践目标中,这个任务的优先级在延迟周期内都被降低。Process(进程) 这个名词经常与任务或线程混淆。至关重要的差别在于系统中的所有任务共享公共的内存空间。进程,另一方面,常常有它们自己的私有内存空间。进程在多用户系统中,但少有地,如有可能,也可在嵌入式系统中。Processor(处理器) 一个对于微处理器、微控制器他数字信号处器无差别的通用术语。processor family(处理器族)一个相关的处理器集,常常连续地从一个生产商产生。例如:Intel”s 80×86族开始从8086开始,现在有80186, 286, 386, 486, Pentium及其他。在一个族中,稍后的产品典型地向后兼容在它以前生产的产品。processor-independent(处理器无关)一个与处理器无关的,并能在其上运行的软件。大多数用高级语言编写程序是处理器无关的。相对于处理器定制。processor-specific(处理器定制) 一个高度依赖处理器的软件,在上其才能运行。一些代码必须用汇编语言编写。相对于处理器无关。Profiler(明细观察程序)一种报告你的程序运行统计数据的软件调试工具。这些统计数据包括调用每个子程序的次数和用去的时间。这些数据常被用来了解哪些子程序是最关键的,并且,由此要求使最好的代码有效率。 ▎ R RAM(随机访问存储器) 随机访问存储器。一个包含了所有每个地址能被按需读写的存储设备的粗略分类。RISC(精简指令集计算机) 精简指令集计算机。一个处理器族的描述。RISC处理器一般的特征是固定长度的指令集,一个负载储备存储结构,和大量通用寄存器,及寄存器窗口。MIPS处理器族是极好的例子。相对CISC而言。ROM(只读存储器)只读存储器。一个包括所的的每个地址只能被读,不能被写的存储器的大概分类。ROM emulator(ROM模拟器) 一种在你的目标板上代替或模拟ROM的调试工具。ROM模拟器动作起来象一个除错监视器,除了它包含自己连到主机上的串口或网络外。ROM monitor See debug monitor.RTOS(实时操作系统) 实时操作系统。一种被特殊设计来用在实时系统中的操作系统。race condition(竞争状态)一种程序运行的结果可能被指令执行的顺序影响的情形。竞争状态仅仅有一种情况下产生,在此处中断或(和)优先抢占是充许的并且有一个临界区存在。real-time system(实时系统) 任何计算机系统,嵌入的或其他的,有一个死线。以下的问题可经被用来区分实时系统与其他的系统:“是迟到的回答坏,还是一个错误的回答坏?”换句话说,如果计算机没有在指定时间内完成它的工作会发生什么?如果什么也没有发生,它不是一个实时系统。如果一些人死或任务失败,它被认为是“硬”实时系统,意思是系统有一个“硬”死线。介于两者之间的是“软”实时系统。Recursive(递归) 自己调用自己的程序的说法。递归一般在嵌入式系统中是不充许的,因为它常常占有大量的堆栈空间。Reentrant(可再入的) 可同时多次运行的程序的说法。可再入的函数可以被安全地递归调用或由多任务多次调用。使代码可再入的关键在于确保在访问全局变量或共享寄存器时互斥现象发生。Register(寄存器) 是处理器或I/O设备一部分的储存器的地址。换句话说,不是标准的储存器。一般地,在寄存器控制每一二进制位或二进制位的集控制大量设备的一些行为。Relocatable(可重定位的) 包含几乎可以准备好在目标机上运行的目标代码的文件。最后一步是使用定位程序去整理保留在代码中的可重定位地址。这个步骤的结果是一个可执行的程序。reset address(重启地址)一个处理器上电或重启后第一个指令能被从之取出来的地址。reset code(重启代码)一段被放置在重启地址的代码。重启代码一般用汇编语言编写并且可能相当简单,只是与”跳转到开始代码”这样的意思相同。reset vector See reset address. ▎ S SRAM(静态随机访问储存器) 静态随机访问储存器。一种在系统上电时以保持它的内容的储存器。当系统断电或重启时,保存在SRAM中的内容将丢失。Scheduler(调度程序) 操作系统中决定下一次哪个任务运行的那部分。决定基于每一个任务的就绪,它们的优先级关系,和特殊调度算法的实现。Semaphore(信号灯)用于进程间同步的数据结构。信号灯常常由操作系统提供。Simulator(仿真器)一种运行在主机上,装作目标机处理器的调试工具。仿真器一般用来测试嵌入式硬件可用之前的软件。不幸地,与模拟与复杂地外设进行交互的尝试常常比它们做到的更差。software interrupt(软件中断) 由软件指令发起的的一个程序的中断。软件中断被用来实现中断点他操作系统进入点。不象真实的中断,那些中断在不防碍程序执行时同步发生。换句话说,软件中断常常在指令运行周期的开始发生。Stack(堆栈)一个包含后进先出队列的内存区域,用来存储参数、自动变量、返回地址和其他一些必须在函数调用中进行维护的信息。在多任务情况下,每一个任务一般都有自己的堆栈区。stack frame(堆栈帧)一个关联特殊函数调用的堆栈区域。startup code(启动代码一个汇编语言代码,它为高级语言写的软件准备好运行的前期工作。大多数C/C++交叉编译器在你可以修改、编译他连接你的嵌入式程序时与启动代码一起来到。 ▎ T Target(目标机)嵌入式系统的另一个名字。这个术语常常在软件开发期间使用,用来区别与嵌入式系统通讯的主机。 Task(任务)Thread(线程)Tracepoint (跟踪点)象中断点,除了停止程序时,计数器还被增加外。跟踪点不是被所有的调试工具支持。Trap(陷入)一个由处理器内部硬件触发的程序中断。例如,处理器可能在一个错误的代码在程序中被发现时陷入。对比软件中断。 ▎ V volatile(动态)一个可能不需要软件的的干涉就可改变的值被叫作动态。例如:在一些I/O设备的寄存器的值可能在响应外部事件时被改变。C语言中的volatile关键字被用来警告你的编译器那是一个指向一些寄存器的指针,请不要优化它。这个将确认在数据使用中的每一时间实际的值是要重新读入的。 ▎ W watchdog timer(看门狗定时器)一种由软件定时重设的硬件定时器。如果软件被破坏而挂起,看门狗定时器将超时,整个系统将自动重启。 嵌入式专业术语概念 SDK 概念:软件开发工具包(SDK,全称:Software Development Kit) SDK是Software Development Kit的缩写,中文意思是“软件开发工具包”。这是一个覆盖面相当广泛的名词,可以这么说:辅助开发某一类软件的相关文档、范例和工具的集合都可以叫做“SDK”。SDK是一系列文件的组合,它为软件的开发提供一个平台(它为软件开发使用各种API提供便利) API 概念:API(Application Programming Interface,应用程序编程接口) 一般是指一些预先定义的函数,目的是提供应用程序与开发人员基于某软件或硬件得以访问一组例程的能力,而又无需访问源码,或理解内部工作机制的细节。 参考链接:https://blog.csdn.net/ITBigGod/article/details/86703336 GLIBC glibc是GNU发布的libc库,即c运行库。glibc是linux系统中最底层的api,几乎其它任何运行库都会依赖于glibc。glibc是一种按照LGPL许可协议发布的,自由的,公开源代码的,方便从网络下载的C的编译程序。 GCC (GNU Compiler Collection,GNU编译器套件)是由GNU开发的编程语言译器。GNU编译器套件包括C、C++、 Objective-C、 Fortran、Java、Ada和Go语言前端,也包括了这些语言的库(如libstdc++,libgcj等。)虽然我们称GCC是C语言的编译器,但使用gcc由C语言源代码文件生成可执行文件的过程不仅仅是编译的过程,而是要经历四个相互关联的步骤∶预处理(也称预编译,Preprocessing)[生成.i]、编译(Compilation)[生成汇编代码.s]、汇编(Assembly)[生成目标文件.o]和链接(Linking)。 命令gcc首先调用cpp进行预处理,在预处理过程中,对源代码文件中的文件包含(include)、预编译语句(如宏定义define等)进行分析。接着调用cc1进行编译,这个阶段根据输入文件生成以.i为后缀的目标文件。汇编过程是针对汇编语言的步骤,调用as进行工作,一般来讲,.S为后缀的汇编语言源代码文件和汇编、.s为后缀的汇编语言文件经过预编译和汇编之后都生成以.o为后缀的目标文件。当所有的目标文件都生成之后,gcc就调用ld来完成最后的关键性工作,这个阶段就是连接。在连接阶段,所有的目标文件被安排在可执行程序中的恰当的位置,同时,该程序所调用到的库函数也从各自所在的档案库中连到合适的地方. 可用如下命令检查gcc版本。 gcc参数详解:https://www.runoob.com/w3cnote/gcc-parameter-detail.html gdb gdb是GNU开源组织发布的一个强大的Linux下的程序调试工具。 https://blog.csdn.net/weixin_37921201/article/details/120117096 core文件 core文件是死机之后为了还原现场进行分析而生成的,使用gdb工具可以翻译对于异常时的函数行号。 CPIO cpio是用来建立、还原备份档的工具程序,它可以加入、解开cpio或tar备份档内的文件。 https://blog.csdn.net/wh_19910525/article/details/8112538?spm=1001.2101.3001.6650.2&utm_medium=distribute.pc_relevant.none-task-blog-2~default~CTRLIST~Rate-2-8112538-blog-116961555.pc_relevant_antiscanv2&depth_1-utm_source=distribute.pc_relevant.none-task-blog-2~default~CTRLIST~Rate-2-8112538-blog-116961555.pc_relevant_antiscanv2&utm_relevant_index=5 http://www.360doc.com/content/21/1118/09/3046928_1004674088.shtml GPIO (General-purpose input/output)通用型输入输出的简称。 通俗地说,就是芯片上的一些引脚(当然并不是芯片上所有的引脚都叫GPIO),可以通过编程控制它们输出高低电平或者通过它们读入引脚的状态-是高电平或是低电平。 GPIO口一是个比较重要的概念,用户可以通过GPIO口和硬件进行数据交互(如UART),控制硬件工作(如LED、蜂鸣器等),读取硬件的工作状态信号(如中断信号)等。GPIO口的使用非常广泛。 https://blog.csdn.net/doitsjz/article/details/70193790 LPC总线 (Low pin count Bus),是在IBM PC兼容机中用于把低带宽设备和“老旧”连接到CPU上。那些常见低速设备有:BIOS,串口,并口,PS/2的键盘和鼠标,软盘控制器,比较新的设备有可信平台模块。LPC总线通常和主板上的南桥物理相连,南桥在IBM PC AT平台上通常连接了一系列的“老旧”设备,例如两个可编程中断控制器, 可编程计时器和两个 ISA DMA 控制器。 https://wenku.baidu.com/view/76556299dfccda38376baf1ffc4ffe473268fd3e.html I2C总线 I2C(Inter-Integrated Circuit)总线是由Philips公司在上世纪80年代开发的一种简单、双向二线制同步串行总线。它只需要两根线即可在连接于总线上的器件之间传送信息。 I2C既是一种总线,也是一种通信协议。总线和通信协议之间的关系类似于硬件和基于此硬件的软件,同一种总线上可以跑多种协议,如在RS485总线上可以跑莫迪康的MODBUS,松下的MEWTOCOL,西门子的profibus/DP等协议;同样地,同一种协议也可以跑在不同的总线上,如上述协议还可以跑在以太网上。一言以蔽之,总线涉及的是物理层的硬件,而协议可以认为是在物理层上传递信息的约定或规则。 或者也可以这么说。在嵌入式开发中,通信协议可分为两层:物理层和协议层。物理层是数据在物理媒介传输的保障;协议层主要规定通信逻辑,如同一收发双方的数据打包、解包标准。 打个比方,物理层相当于现实中的公路,而协议层则是交通规则,汽车可以在路上行驶,但是需要交通规则对行驶规则进行约束,不然将出现危险,也就是数据传输紊乱、丢包。 原文链接:https://blog.csdn.net/ctyqy2015301200079/article/details/83830326 SPI总线 (Serial Peripheral interface)串行外围设备接口,是一种高速的,全双工,同步的通信总线。 SPI接口主要应用在 EEPROM,FLASH,实时时钟,AD转换器,还有数字信号处理器和数字信号解码器之间。 UART 通用异步收发传输器(Universal Asynchronous Receiver/Transmitter,通常称作UART) 是一种串行异步收发协议,应用十分广泛。UART工作原理是将数据的二进制位一位一位的进行传输。在UART通讯协议中信号线上的状态位高电平代表’1’低电平代表’0’。当然两个设备使用UART串口通讯时,必须先约定好传输速率和一些数据位。 AMBA总线 AMBA是由ARM公司研发推出的一种高级微控制器总线架构(Advanced Microcontroller Bus Architecture)。其中AMBA包含了四种不同的总线标准,分别是: AHB ASB APB AXI https://blog.csdn.net/little_ox/article/details/118399117 https://zhuanlan.zhihu.com/p/155629044 JTAG Joint Test Action Group;联合测试工作组 JTAG是一种IEEE标准用来解决板级问题,开发于上个世纪80年代。用于芯片内部测试,今天JTAG被用来烧录、debug、探查端口。当然,最原始的使用是边界测试。 https://www.cnblogs.com/kingstacker/p/7454814.html RTC 实时时钟的缩写是RTC(Real_Time Clock)。RTC 是集成电路,通常称为时钟芯片。 实时时钟芯片是日常生活中应用最为广泛的消费类电子产品之一。它为人们提供精确的实时时间,或者为电子系统提供精确的时间基准,目前实时时钟芯片大多采用精度较高的晶体振荡器作为时钟源。 https://wenku.baidu.com/view/6a00d5487b3e0912a21614791711cc7931b77804.html https://blog.csdn.net/God__Rain/article/details/113664728 https://www.sigusoft.com/p/724a80adb7a5 DS1337时钟芯片手册: https://www.icspec.com/specification/specification_detail/21c5508c-0239-11eb-8577-00163e14a913 内存SPD SPD是内存模组上面的一个可擦写的eeprom,里面记录了该内存的许多重要信息,诸如内存的芯片及模组厂商、工作频率、工作电压、速度、容量、电压与行、列地址带宽等参数。SPD信息一般都是在出厂前,由内存模组制造商根据内存芯片的实际性能写入到eeprom芯片中。 GIC Generic Interrupt Controller。是ARM公司提供的一个通用的中断控制器。 https://blog.csdn.net/yhb1047818384/article/details/86708769 TLB Translation Lookaside Buffer页表缓存 TLB是一个内存管理单用于改进虚拟地址到物理地址转换速度的缓存. TLB是位于内存中的页表的cache,如果没有TLB,则每次取数据都需要两次访问内存,即查页表获得物理地址和取数据. https://blog.csdn.net/jeiwt/article/details/5911358?utm_medium=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-1.control&depth_1-utm_source=distribute.pc_relevant.none-task-blog-BlogCommendFromMachineLearnPai2-1.control 页表一般都很大,并且存放在内存中,所以处理器引入MMU后,读取指令、数据需要访问两次内存:首先通过查询页表得到物理地址,然后访问该物理地址读取指令、数据。为了减少因为MMU导致的处理器性能下降,引入了TLB,TLB是Translation Lookaside Buffer的简称,可翻译为“地址转换后援缓冲器”,也可简称为“快表”。简单地说,TLB就是页表的Cache,其中存储了当前最可能被访问到的页表项,其内容是部分页表项的一个副本。只有在TLB无法完成地址翻译任务时,才会到内存中查询页表,这样就减少了页表查询导致的处理器性能下降。 来自 https://www.cnblogs.com/alantu2018/p/9000777.html 快表,直译为旁路快表缓冲,也可以理解为页表缓冲,地址变换高速缓存。 由于页表存放在主存中,因此程序每次访存至少需要两次:一次访存物理地址,第二次访存才获得数据。提高访存性能的关键在于依靠页表的访问局部性。当一个转换的虚拟页号被使用时,它可能在不久的将来再次被使用到,。 TLB是一种高速缓存,内存管理硬件使用它来改善虚拟地址到物理地址的转换速度。当前所有的个人桌面,笔记本和服务器处理器都使用TLB来进行虚拟地址到物理地址的映射。使用TLB内核可以快速的找到虚拟地址指向物理地址,而不需要请求RAM内存虚拟地址到物理地址的映射关系。这与data cache和instruction caches有很大的相似之处。 来自 https://www.cnblogs.com/alantu2018/p/9000777.html TLB原理 当cpu要访问一个虚拟地址/线性地址时,CPU会首先根据虚拟地址的高20位(20是x86特定的,不同架构有不同的值)在TLB中查找。如果是表中没有相应的表项,称为TLB miss,需要通过访问慢速RAM中的页表计算出相应的物理地址。同时,物理地址被存放在一个TLB表项中,以后对同一线性地址的访问,直接从TLB表项中物理地址即可,称为TLB hit。 来自 https://www.cnblogs.com/alantu2018/p/9000777.html 参考 http://www.wowotech.net/memory_management/tlb-flush.html ROM&RAM rom是固态储存,ram是动态储存。 ROM属于内存,也称作只读存储器,只能读出事先所存数据的固态半导版体存储器;ROM的特点是一次写入,反复读取;RAM的特点是随机存取的。 广义上内存指Cache、ROM和RAM三部分,其中Cache现在是做在CPU里面的,ROM在主板上,用来存放BIOS,装机内存指的是RAM。 两个最大的区别从字面上就能看出其rom是相当于一个永久硬盘。存东西在上面可反复使用,不易丢失!ram相当于网吧电脑上的c盘。重启等原因就会丢失数据,在手机上起到缓存的作用! http://www.elecfans.com/d/1386845.html SRAM和DRAM https://zhuanlan.zhihu.com/p/52272990 https://blog.csdn.net/sigusoft_16933601/article/details/111876189?spm=1001.2014.3001.5502

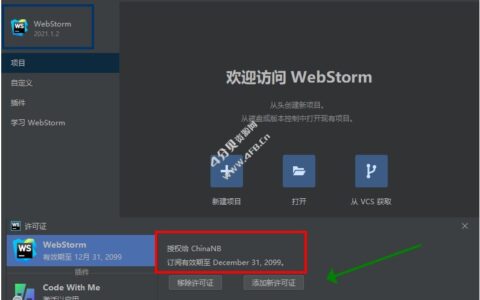

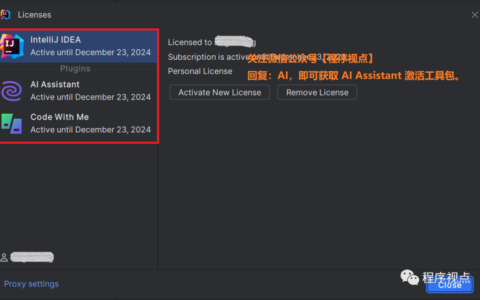

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/70842.html