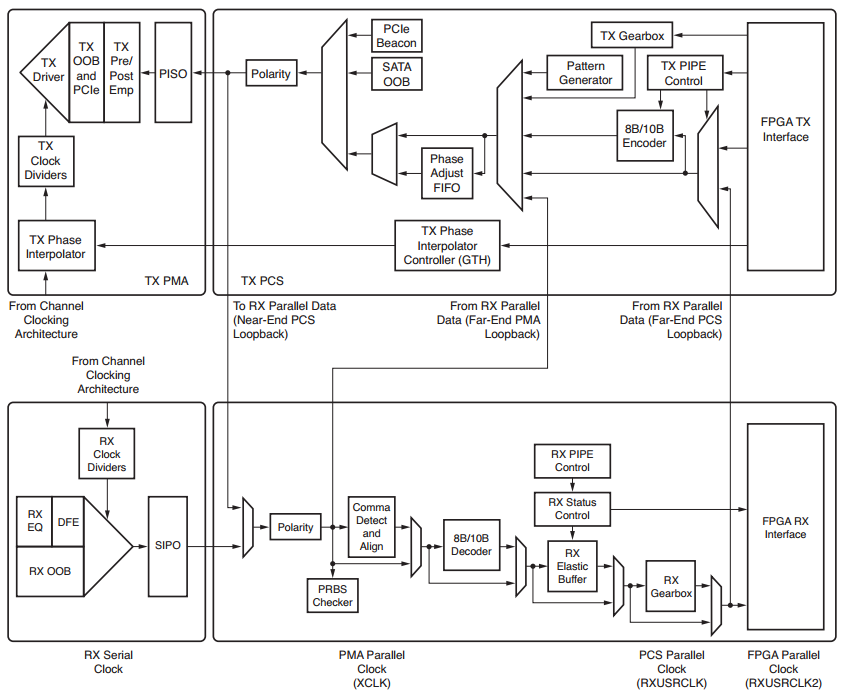

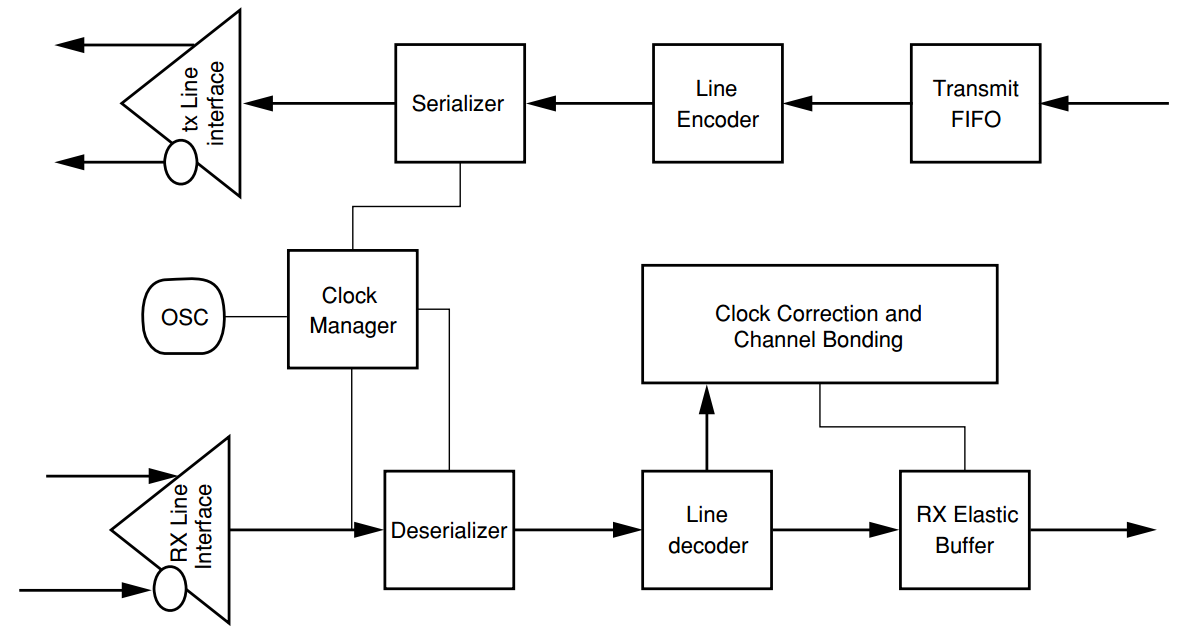

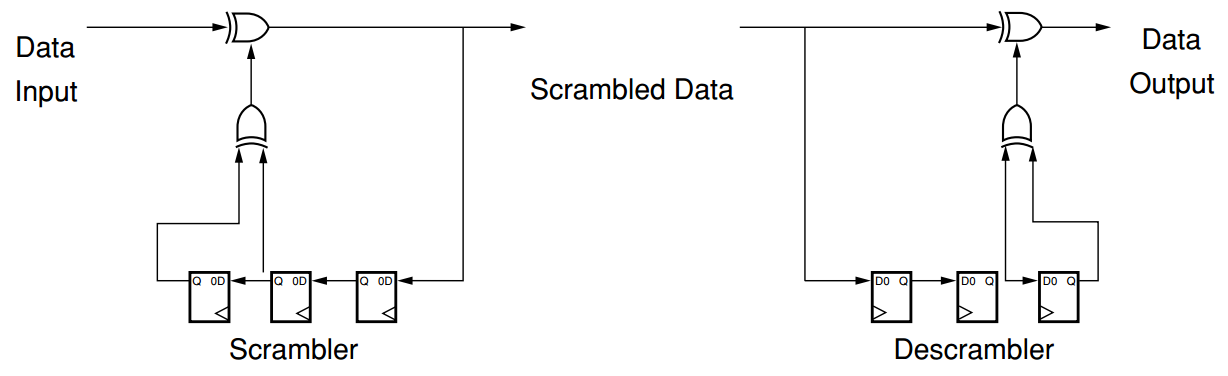

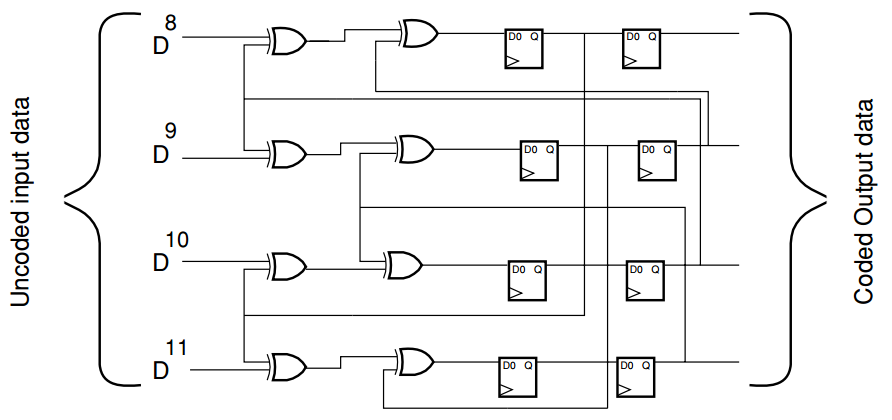

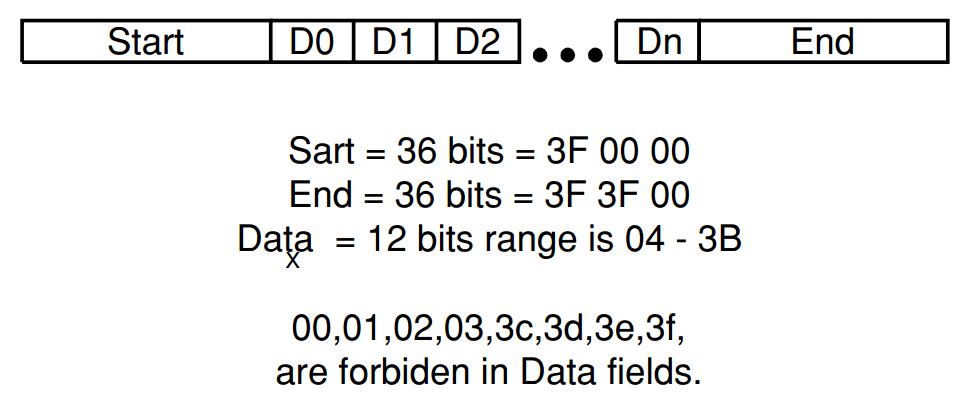

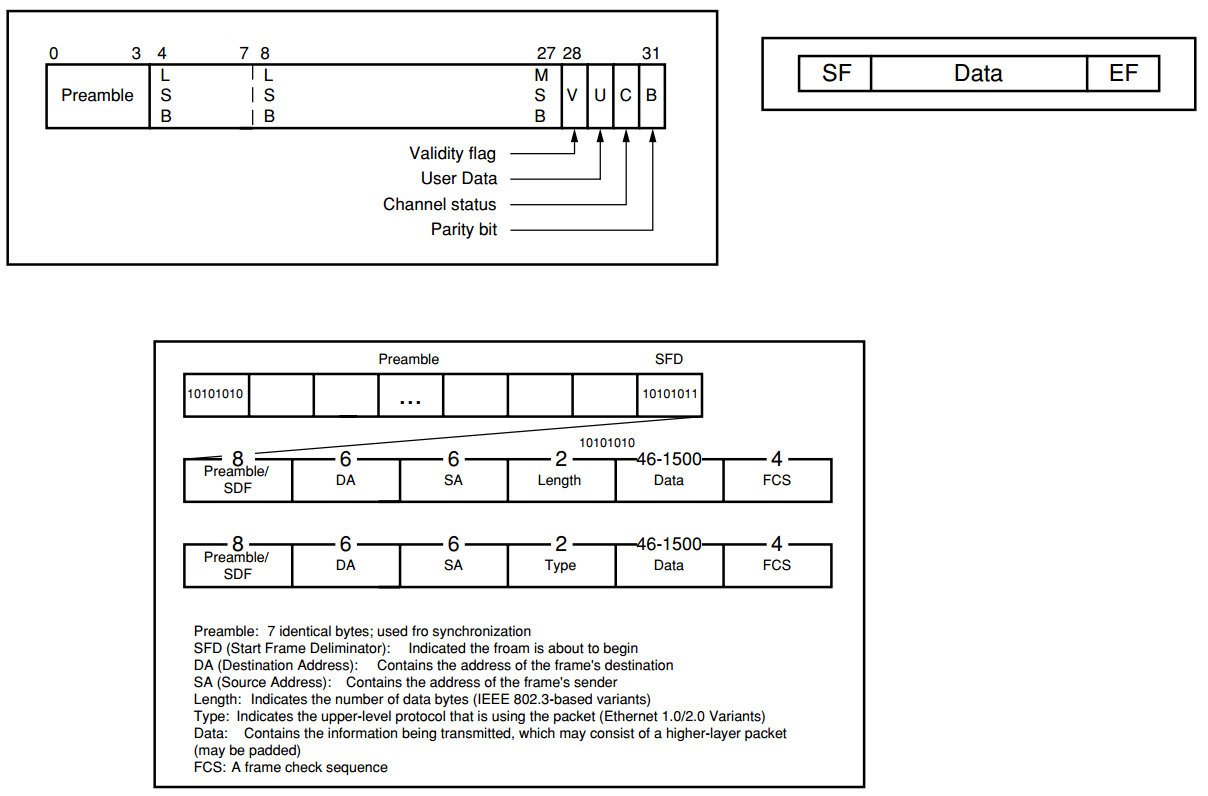

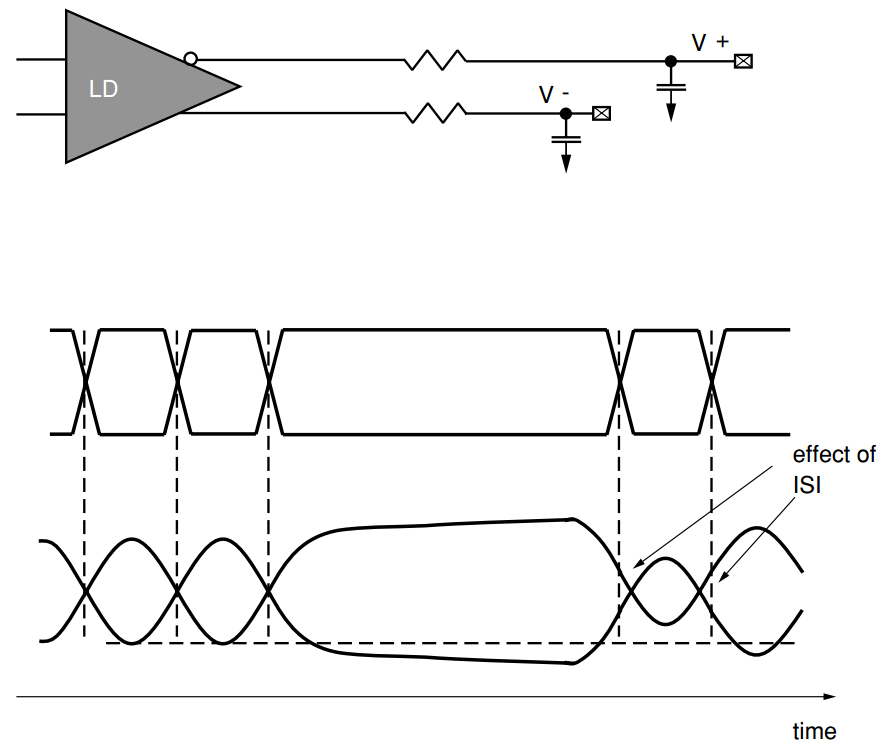

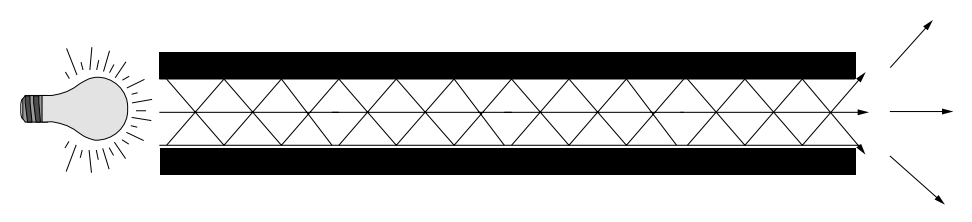

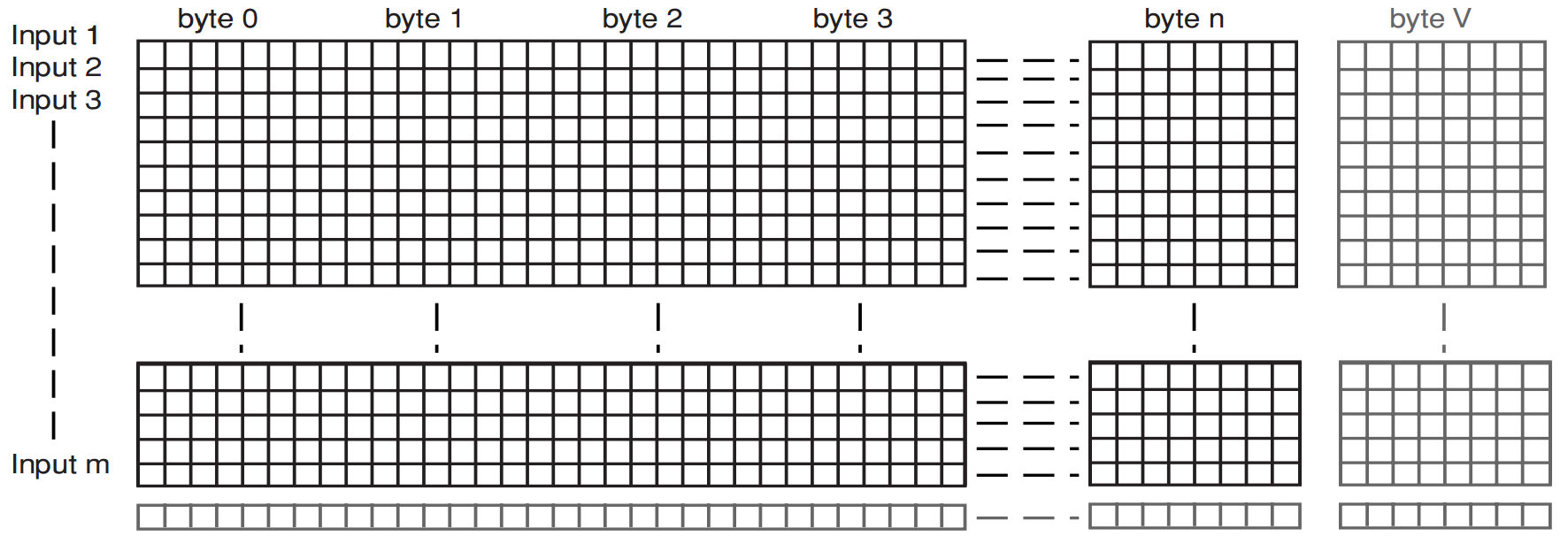

SERDES关键技术总结 转自https://www.cnblogs.com/liujinggang/p/10125727.html 一、SERDES介绍 随着大数据的兴起以及信息技术的快速发展,数据传输对总线带宽的要求越来越高,并行传输技术的发展受到了时序同步困难、信号偏移严重,抗干扰能力弱以及设计复杂度高等一系列问题的阻碍。与并行传输技术相比,串行传输技术的引脚数量少、扩展能力强、采用点对点的连接方式,而且能提供比并行传输更高带宽,因此现已广泛用于嵌入式高速传输领域。 Xilinx公司的许多FPGA已经内置了一个或多个MGT(Multi-Gigabit Transceiver)收发器,也叫做SERDES(Multi-Gigabit Serializer/Deserializer)。MGT收发器内部包括高速串并转换电路、时钟数据恢复电路、数据编解码电路、时钟纠正和通道绑定电路,为各种高速串行数据传输协议提供了物理层基础。MGT收发器的TX发送端和RX接收端功能独立,而且均由物理媒介适配层(Physical Media Attachment,PMA)和物理编码子层(Physical Coding Sublayer,PCS)两个子层组成,结构如下图所示

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/51936.html