如何查看bios支持pcie启动_PCIE连接器通过BIOS实现PCIE设备热插拔功能的方法及主板与流程本发明属于计算机技术领域,尤其涉及一种通过bios实现pcie设备热插拔功能的方法及主板。背景技术:在主板领域,目前主流的外围设备包括usb接口设备、sata接口设备、pcie接

通过BIOS实现PCIE设备热插拔功能的方法及主板与流程

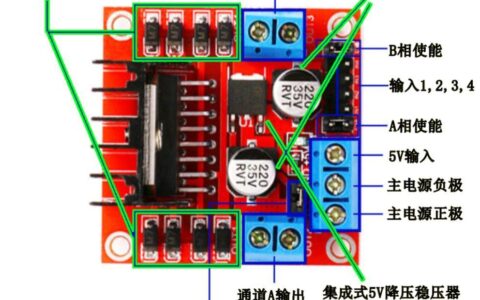

本发明属于计算机技术领域,尤其涉及一种通过bios实现pcie设备热插拔功能的方法及主板。 背景技术: 在主板领域,目前主流的外围设备包括usb接口设备、sata接口设备、pcie接口设备等,无论在主板启动过程还是在各种不同类型系统下面,usb和sata接口设备都能随意进行热插入和热拔出,实现即插即用的功能,用户操作非常方便。但是市面上主流的主板,都没有设计pcie设备热插拔的功能,要插拔更换pcie设备,必须在主板关机状态下进行。现在的技术,通过硬件设计、bios程序设计和操作系统支持,已经能实现pcie设备的热插拔功能。硬件上,需要增加热插拔控制器、电源指示灯、提示按钮等,要设计卡槽电源切换逻辑电路、板卡重置逻辑电路;固件bios要提供软件支持;操作系统要提供支持pcie设备热插拔所需要的功能组件,包括用户操作界面软件、热插拔服务程序、标准热插拔系统驱动、设备驱动,整个功能实现的过程硬件成本增加,并且实现起来也很复杂,所以主流主板都没有去实现pcie设备热插拔功能。 目前主流主板没有去实现pcie设备热插拔功能,可以通过硬件、bios、操作系统的配合,是能实现这个功能的,但是即使实现这个功能,热插拔的操作也只能在acpi操作系统下来完成,开机过程bios运行阶段不能进行热插拔操作,non-acpi系统(例如dos系统)不能进行热插拔操作,一方面,这些non-acpi环境下,pcie设备热插拔功能是缺失的,不能满足操作需求,另外一方面,操作人员可能会误以为所有环境都支持pcie设备热插拔功能,在进入了acpi操作系统前进行热插拔操作,导致误操作。 技术实现要素: 针对以上技术问题,本发明公开了一种通过bios实现pcie设备热插拔功能的方法及主板,能在non-acpi环境下有效地支持pcie设备热插拔功能,弥补了non-acpi环境下功能的缺失,满足操作人员的需求;而且硬件线路设计简单,不会增加主板的成本,也不会增加开发调试时间. 对此,本发明采用的技术方案为: 一种通过bios实现pcie设备热插拔功能的方法,主板包括pch和与其连接的bios基本输入输出模块;pch包括gpio1、gpio2、gpio3、gpio4、gpio5、gpio6和gpio7,所述gpio1、gpio2和gpio3分别与pcie插槽电连接;所述gpio1通过电阻r1与3.3v辅助电源连接,所述gpio1同时通过电阻r2接地;所述gpio2通过电阻r1与3.3v电源连接,所述gpio2同时通过电阻r2接地;所述gpio3通过电阻r1与12v电源连接,所述gpio3同时通过电阻r2接地;gpio4与pcie插槽的热插拔检测信号prsnt1#电连接;gpio5与热插拔检测信号prsnt2#电连接,gpio6连接发光二极管后通过电阻r接地,gpio7通过电阻r连接3.3v电源,并通过按键接地。 作为本发明的进一步改进,所述bios基本输入输出模块设定gpio1、gpio2、gpio3、gpio6、gpio7为gpio输出功能;所述bios基本输入输出模块设定gpio4和gpio5为gpio输入功能。 作为本发明的进一步改进,在pcie设备热插入阶段,所述bios基本输入输出模块采用以下步骤进行控制: 步骤s101,运行bios程序,进行gpio初始化,将gpio1、gpio2、gpio3和gpio6设置为gpio输出功能,输出低电平,pcie插槽电源关闭,发光二极管熄灭; 步骤s102,将gpio4、gpio5、gpio7设置为输入功能,打开gpio4、gpio7触发smi中断功能,然后bios程序进入non-acpi环境; 包括gpio初始化之后bios运行过程、dos系统等。 步骤s103,在non-acpi环境下,若有pcie设备插入pcie插槽,则将gpio5拉低,不触发中断程序,将gpio4拉低,触发smi中断程序; 步骤s104,中断程序首先检查gpio5是否是低电平,如果不是,则不处理,说明设备接触不良或者其他原因导致的gpio拉低;如果gpio5是低电平,说明gpio4、gpio5都被拉低,有设备插入插槽且接触良好;smi中断程序将gpio6设置为方波输出,发光二极管闪烁,提醒操作人员不能拔出设备; 步骤s105,然后将gpio1、gpio2、gpio3设置为高电平输出,打开pcie插槽的3.3v辅助电源、3.3v电源和12v电源,然后读取插槽设备的父级桥,为设备分配bus号资源,等待pcie设备和父级桥linktraining结束;linktraining结束后,为pcie设备分配内存资源、io资源,为设备分配中断。 作为本发明的进一步改进,步骤s105中,linktraining结束后,检查mmio资源当中是否有足够资源分配给pcie设备,如果有资源,根据基地址计算,为pcie设备分配内存资源、io资源,为设备分配中断;如果没有资源,首先修改tolm低内存顶端寄存器,将值减小,增加mmio的大小,然后设置mmiorule寄存器来说明mmio的大小,修改mtrr(内存类型范围寄存器)寄存器,设置新增的mmio为不可缓冲类型,然后更新e820表,说明当前所有内存的类型使用情况,然后再分配内存、io和中断资源,分配完资源后,打开内存、io资源的开关,让资源处于可使用状态。 作为本发明的进一步改进,还包括步骤s106,将gpio6设置为高电平输出,让发光二极管常亮,表明设备可以正常工作了。 作为本发明的进一步改进,在pcie设备热拔出阶段,所述bios基本输入输出模块采用以下步骤进行控制: 步骤s201,初始化gpio1、gpio2、gpio3和gpio6设置为输出低电平,发光二极管熄灭;然后设置gpio4、gpio5和gpio7为输入功能,打开gpio4、gpio7触发smi中断功能,然后bios程序进入non-acpi环境;包括gpio初始化之后bios运行过程、dos系统等。 步骤s202,gpio7一直输入高电平,如果操作人员有拔出pcie设备的需求,首先按下按键,使gpio7产生一个低电平,触发smi中断程序; 步骤s204,bios程序通过设备的命令寄存器禁止内存和io空间,再在父级桥里面禁止与pcie设备的链接,将gpio1、gpio2、gpio3设置为输出低电平,关闭pcie插槽的电源,释放掉pcie设备所需要的内存、io和中断资源。 这里释放掉的内存资源并没有给系统使用,仍然保留mmio属性,方便再次插入设备时候优先分配这部分资源。 作为本发明的进一步改进,还包括步骤s203,smi中断程序启动中,先将gpio6设置为输出方波,使发光二极管闪烁,提醒操作人员不能拔出设备。 作为本发明的进一步改进,还包括步骤s205,将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。 作为本发明的进一步改进,所述gpio4、gpio5、gpio6与3.3v电源连接。 本发明还公开了一种bios阶段实现pcie设备热插拔的主板,其采用如上任意一项通过bios实现pcie设备热插拔功能的方法。 与现有技术相比,本发明的有益效果为: 采用本发明的技术方案,实现了在non-acpi环境中pcie设备热插拔的功能,弥补这种环境下功能的缺失,而硬件成本基本没有增加。通过单个gpio和发光二极管连接,完成与操作人员的交流,避免误操作。在内存资源方面,无需要预先预留资源,插入设备后,再资源分配给设备,增加了内存资源的利用率。资源分配过程中,不会对其他设备进行资源重新分配,中断其他设备的使用,最大限度降低插拔设备对系统的影响,侦测设备热插入时,采用双在位pin角侦测,无需按钮提示。 附图说明 图1是本发明一种实施例的硬件连接结构示意图。 图2是本发明一种实施例的pcie设备热插入时的方法的流程图。 图3是本发明一种实施例的pcie设备热拔出时的方法的流程图。 具体实施方式 下面对本发明的较优的实施例作进一步的详细说明。 一种通过bios实现pcie设备热插拔功能的方法,其包括硬件电路设计部分和bios程序设计部分。 硬件电路设计部分如下: 如图1所示,硬件上,主要是pch的gpio和pcie插槽之间的线路设计。pch的gpio1、gpio2和gpio3都设置为gpio输出功能,gpio1通过r1和r2电阻将3.3v辅助电源(3.3vaux)连接到pcie插槽上,gpio2通过电阻r1和r2将3.3v电源连接到pcie插槽上,gpio3通过电阻r1和r2将12v电源连接到pcie插槽上,gpio4和gpio5设置为gpio输入功能,gpio4连接到热插拔检测信号prsnt1#上面,gpio5连接到热插拔检测信号prsnt2#上面,gpio6设置为gpio输出功能,连接发光二极管,通过电阻r接地,gpio7设置为gpio输入功能,3.3v电源连接电阻r,电阻r既连接gpio7,也通过按键接地。 以下为pcie设备热插入操作。 操作人员将pcie设备热插入pcie插槽内,prsnt1#和prsnt2#信号会被同时拉低,低电平信号通过gpio4和gpio5输入到pch,产生smi中断,运行bios中断程序,bios程序将光电二极管设置为闪烁状态,提醒操作人员,此时不要拔出pcie设备,然后bios将gpio1、gpio2和gpio3设置为高电平输出,12v电源、3.3v电源和3.3v辅助电源给pcie插槽供电,等待bios对设备进行初始化完成,初始化完成后,bios将发光二极管设置为常亮状态,提醒操作人员,pcie设备已经初始化完成,可以进行正常工作了。这里我们采用prsnt1#和prsnt2#两个信号同时被拉低来判断设备的插入状态,防止pcie设备接触不良或者其他误操作,导致单个信号被拉低,误报设备接入状态。 以下为pcie设备热移除操作。 操作人员按下按键,会产生一个低电平信号,通过gpio7输入到pch,产生一个smi中断,运行bios中断程序,bios程序将光电二极管设置为闪烁状态,提醒操作人员,此时不要拔出pcie设备,直到bios程序完成相关设置,并将gpio123设置为输出低电平,关闭插槽的电源,释放掉设备所需要的内存、io和中断资源,最后将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。 bios程序设计部分如下: pcie设备热插入程序设计: 如图2所示,bios程序开始运行,首先进行gpio初始化,将gpio1236设置为gpio输出功能,输出低电平,pcie插槽电源关闭,发光二极管熄灭,将gpio457设置为输入功能,打开gpio47触发smi中断功能,然后bios程序进入non-acpi环境,包括gpio初始化之后bios运行过程、dos系统等。在non-acpi环境下,若有pcie设备插入插槽,会将gpio5拉低,但不会触发中断程序,会将gpio4拉低,触发smi中断程序。中断程序首先检查gpio5是否是低电平,如果不是,则不处理,说明设备接触不良或者其他原因导致的gpio拉低,如果是低电平,说明gpio45都被拉低,有设备插入插槽且接触良好。中断程序将gpio6设置为方波输出,让发光二极管闪烁,提醒操作人员不能拔出设备,然后将gpio123设置为高电平输出,打开pcie插槽的3.3v辅助电源、3.3v电源和12v电源,然后读取插槽设备的父级桥,为设备分配bus号资源,等待pcie设备和父级桥linktraining结束,training结束后,检查mmio资源当中是否有足够资源分配给pcie设备,如果有资源,根据基地址计算,为设备分配内存资源、io资源,为设备分配中断,如果没有资源,首先修改tolm(低内存顶端寄存器),将值减小,增加mmio的大小,然后设置mmiorule寄存器来说明mmio的大小,修改mtrr(内存类型范围寄存器)寄存器,设置新增的mmio为不可缓冲类型,然后更新e820表,说明当前所有内存的类型使用情况,然后再分配内存、io和中断资源,分配完资源后,打开内存、io资源的开关,让资源处于可使用状态。最后,将gpio6设置为高电平输出,让发光二极管常亮,表明设备可以正常工作了。 pcie设备热拔出程序设计: 同热插入程序一样,如图3所示,首先要初始化gpio1236设置为输出低点平,发光二极管熄灭,然后设置gpio457为输入功能,打开gpio47触发smi中断功能,然后bios程序进入non-acpi环境,包括gpio初始化之后bios运行过程、dos系统等。gpio7一直输入高电平,如果操作人员有拔出pcie设备的需求,首先按下提示按钮,会使gpio7产生一个低电平,将触发smi中断程序。中断程序中,首先将gpio6设置为输出方波,使发光二极管闪烁,提醒操作人员不能拔出设备,然后程序通过设备的命令寄存器禁止内存和io空间,再在父级桥里面禁止与设备的链接,将gpio123设置为输出低电平,关闭插槽的电源,释放掉设备所需要的内存、io和中断资源,最后将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。这里释放掉的内存资源并没有给系统使用,仍然保留mmio属性,方便再次插入设备时候优先分配这部分资源。 上述方法通过简单的硬件线路设计和bios程序设计,能在non-acpi环境下有效地支持pcie设备热插拔功能,弥补了non-acpi环境下功能的缺失,满足操作人员的需求。而且硬件线路设计简单,不会增加主板的成本,也不会增加开发调试时间。 本发明所涉及的英文缩写的技术术语的解释: bios(basicinputoutputsystem):基本输入输出系统,主要用于计算机开机过程中各种硬件设备的初始化和检测。 pch(platformcontrollerhub):intel公司的集成南桥。 pcie(pci-express):一种高速串行总线接口技术标准。 gpio(generalpurposeinputoutput):通用输入/输出。 acpi(advancedconfigurationandpowermanagementinterface):高级配置与电源管理接口,操作系统应用程序管理所有电源管理接口,non-acpi环境,即不支持acpi标准的环境。 usb(universalserialbus):通用串行总线。 sata(serialadvancedtechnologyattachment):串行ata接口规。 dos(diskoperatingsystem):磁盘操作系统。 smi(systemmanagementinterrupt):系统管理中断。 mmio(memorymappingi/o):内存映射i/o。 tolm(topoflowmemory):低内存顶端。 mtrr(memorytyperangeregisters):内存类型范围寄存器。 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

本发明属于计算机技术领域,尤其涉及一种通过bios实现pcie设备热插拔功能的方法及主板。 背景技术: 在主板领域,目前主流的外围设备包括usb接口设备、sata接口设备、pcie接口设备等,无论在主板启动过程还是在各种不同类型系统下面,usb和sata接口设备都能随意进行热插入和热拔出,实现即插即用的功能,用户操作非常方便。但是市面上主流的主板,都没有设计pcie设备热插拔的功能,要插拔更换pcie设备,必须在主板关机状态下进行。现在的技术,通过硬件设计、bios程序设计和操作系统支持,已经能实现pcie设备的热插拔功能。硬件上,需要增加热插拔控制器、电源指示灯、提示按钮等,要设计卡槽电源切换逻辑电路、板卡重置逻辑电路;固件bios要提供软件支持;操作系统要提供支持pcie设备热插拔所需要的功能组件,包括用户操作界面软件、热插拔服务程序、标准热插拔系统驱动、设备驱动,整个功能实现的过程硬件成本增加,并且实现起来也很复杂,所以主流主板都没有去实现pcie设备热插拔功能。 目前主流主板没有去实现pcie设备热插拔功能,可以通过硬件、bios、操作系统的配合,是能实现这个功能的,但是即使实现这个功能,热插拔的操作也只能在acpi操作系统下来完成,开机过程bios运行阶段不能进行热插拔操作,non-acpi系统(例如dos系统)不能进行热插拔操作,一方面,这些non-acpi环境下,pcie设备热插拔功能是缺失的,不能满足操作需求,另外一方面,操作人员可能会误以为所有环境都支持pcie设备热插拔功能,在进入了acpi操作系统前进行热插拔操作,导致误操作。 技术实现要素: 针对以上技术问题,本发明公开了一种通过bios实现pcie设备热插拔功能的方法及主板,能在non-acpi环境下有效地支持pcie设备热插拔功能,弥补了non-acpi环境下功能的缺失,满足操作人员的需求;而且硬件线路设计简单,不会增加主板的成本,也不会增加开发调试时间. 对此,本发明采用的技术方案为: 一种通过bios实现pcie设备热插拔功能的方法,主板包括pch和与其连接的bios基本输入输出模块;pch包括gpio1、gpio2、gpio3、gpio4、gpio5、gpio6和gpio7,所述gpio1、gpio2和gpio3分别与pcie插槽电连接;所述gpio1通过电阻r1与3.3v辅助电源连接,所述gpio1同时通过电阻r2接地;所述gpio2通过电阻r1与3.3v电源连接,所述gpio2同时通过电阻r2接地;所述gpio3通过电阻r1与12v电源连接,所述gpio3同时通过电阻r2接地;gpio4与pcie插槽的热插拔检测信号prsnt1#电连接;gpio5与热插拔检测信号prsnt2#电连接,gpio6连接发光二极管后通过电阻r接地,gpio7通过电阻r连接3.3v电源,并通过按键接地。 作为本发明的进一步改进,所述bios基本输入输出模块设定gpio1、gpio2、gpio3、gpio6、gpio7为gpio输出功能;所述bios基本输入输出模块设定gpio4和gpio5为gpio输入功能。 作为本发明的进一步改进,在pcie设备热插入阶段,所述bios基本输入输出模块采用以下步骤进行控制: 步骤s101,运行bios程序,进行gpio初始化,将gpio1、gpio2、gpio3和gpio6设置为gpio输出功能,输出低电平,pcie插槽电源关闭,发光二极管熄灭; 步骤s102,将gpio4、gpio5、gpio7设置为输入功能,打开gpio4、gpio7触发smi中断功能,然后bios程序进入non-acpi环境; 包括gpio初始化之后bios运行过程、dos系统等。 步骤s103,在non-acpi环境下,若有pcie设备插入pcie插槽,则将gpio5拉低,不触发中断程序,将gpio4拉低,触发smi中断程序; 步骤s104,中断程序首先检查gpio5是否是低电平,如果不是,则不处理,说明设备接触不良或者其他原因导致的gpio拉低;如果gpio5是低电平,说明gpio4、gpio5都被拉低,有设备插入插槽且接触良好;smi中断程序将gpio6设置为方波输出,发光二极管闪烁,提醒操作人员不能拔出设备; 步骤s105,然后将gpio1、gpio2、gpio3设置为高电平输出,打开pcie插槽的3.3v辅助电源、3.3v电源和12v电源,然后读取插槽设备的父级桥,为设备分配bus号资源,等待pcie设备和父级桥linktraining结束;linktraining结束后,为pcie设备分配内存资源、io资源,为设备分配中断。 作为本发明的进一步改进,步骤s105中,linktraining结束后,检查mmio资源当中是否有足够资源分配给pcie设备,如果有资源,根据基地址计算,为pcie设备分配内存资源、io资源,为设备分配中断;如果没有资源,首先修改tolm低内存顶端寄存器,将值减小,增加mmio的大小,然后设置mmiorule寄存器来说明mmio的大小,修改mtrr(内存类型范围寄存器)寄存器,设置新增的mmio为不可缓冲类型,然后更新e820表,说明当前所有内存的类型使用情况,然后再分配内存、io和中断资源,分配完资源后,打开内存、io资源的开关,让资源处于可使用状态。 作为本发明的进一步改进,还包括步骤s106,将gpio6设置为高电平输出,让发光二极管常亮,表明设备可以正常工作了。 作为本发明的进一步改进,在pcie设备热拔出阶段,所述bios基本输入输出模块采用以下步骤进行控制: 步骤s201,初始化gpio1、gpio2、gpio3和gpio6设置为输出低电平,发光二极管熄灭;然后设置gpio4、gpio5和gpio7为输入功能,打开gpio4、gpio7触发smi中断功能,然后bios程序进入non-acpi环境;包括gpio初始化之后bios运行过程、dos系统等。 步骤s202,gpio7一直输入高电平,如果操作人员有拔出pcie设备的需求,首先按下按键,使gpio7产生一个低电平,触发smi中断程序; 步骤s204,bios程序通过设备的命令寄存器禁止内存和io空间,再在父级桥里面禁止与pcie设备的链接,将gpio1、gpio2、gpio3设置为输出低电平,关闭pcie插槽的电源,释放掉pcie设备所需要的内存、io和中断资源。 这里释放掉的内存资源并没有给系统使用,仍然保留mmio属性,方便再次插入设备时候优先分配这部分资源。 作为本发明的进一步改进,还包括步骤s203,smi中断程序启动中,先将gpio6设置为输出方波,使发光二极管闪烁,提醒操作人员不能拔出设备。 作为本发明的进一步改进,还包括步骤s205,将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。 作为本发明的进一步改进,所述gpio4、gpio5、gpio6与3.3v电源连接。 本发明还公开了一种bios阶段实现pcie设备热插拔的主板,其采用如上任意一项通过bios实现pcie设备热插拔功能的方法。 与现有技术相比,本发明的有益效果为: 采用本发明的技术方案,实现了在non-acpi环境中pcie设备热插拔的功能,弥补这种环境下功能的缺失,而硬件成本基本没有增加。通过单个gpio和发光二极管连接,完成与操作人员的交流,避免误操作。在内存资源方面,无需要预先预留资源,插入设备后,再资源分配给设备,增加了内存资源的利用率。资源分配过程中,不会对其他设备进行资源重新分配,中断其他设备的使用,最大限度降低插拔设备对系统的影响,侦测设备热插入时,采用双在位pin角侦测,无需按钮提示。 附图说明 图1是本发明一种实施例的硬件连接结构示意图。 图2是本发明一种实施例的pcie设备热插入时的方法的流程图。 图3是本发明一种实施例的pcie设备热拔出时的方法的流程图。 具体实施方式 下面对本发明的较优的实施例作进一步的详细说明。 一种通过bios实现pcie设备热插拔功能的方法,其包括硬件电路设计部分和bios程序设计部分。 硬件电路设计部分如下: 如图1所示,硬件上,主要是pch的gpio和pcie插槽之间的线路设计。pch的gpio1、gpio2和gpio3都设置为gpio输出功能,gpio1通过r1和r2电阻将3.3v辅助电源(3.3vaux)连接到pcie插槽上,gpio2通过电阻r1和r2将3.3v电源连接到pcie插槽上,gpio3通过电阻r1和r2将12v电源连接到pcie插槽上,gpio4和gpio5设置为gpio输入功能,gpio4连接到热插拔检测信号prsnt1#上面,gpio5连接到热插拔检测信号prsnt2#上面,gpio6设置为gpio输出功能,连接发光二极管,通过电阻r接地,gpio7设置为gpio输入功能,3.3v电源连接电阻r,电阻r既连接gpio7,也通过按键接地。 以下为pcie设备热插入操作。 操作人员将pcie设备热插入pcie插槽内,prsnt1#和prsnt2#信号会被同时拉低,低电平信号通过gpio4和gpio5输入到pch,产生smi中断,运行bios中断程序,bios程序将光电二极管设置为闪烁状态,提醒操作人员,此时不要拔出pcie设备,然后bios将gpio1、gpio2和gpio3设置为高电平输出,12v电源、3.3v电源和3.3v辅助电源给pcie插槽供电,等待bios对设备进行初始化完成,初始化完成后,bios将发光二极管设置为常亮状态,提醒操作人员,pcie设备已经初始化完成,可以进行正常工作了。这里我们采用prsnt1#和prsnt2#两个信号同时被拉低来判断设备的插入状态,防止pcie设备接触不良或者其他误操作,导致单个信号被拉低,误报设备接入状态。 以下为pcie设备热移除操作。 操作人员按下按键,会产生一个低电平信号,通过gpio7输入到pch,产生一个smi中断,运行bios中断程序,bios程序将光电二极管设置为闪烁状态,提醒操作人员,此时不要拔出pcie设备,直到bios程序完成相关设置,并将gpio123设置为输出低电平,关闭插槽的电源,释放掉设备所需要的内存、io和中断资源,最后将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。 bios程序设计部分如下: pcie设备热插入程序设计: 如图2所示,bios程序开始运行,首先进行gpio初始化,将gpio1236设置为gpio输出功能,输出低电平,pcie插槽电源关闭,发光二极管熄灭,将gpio457设置为输入功能,打开gpio47触发smi中断功能,然后bios程序进入non-acpi环境,包括gpio初始化之后bios运行过程、dos系统等。在non-acpi环境下,若有pcie设备插入插槽,会将gpio5拉低,但不会触发中断程序,会将gpio4拉低,触发smi中断程序。中断程序首先检查gpio5是否是低电平,如果不是,则不处理,说明设备接触不良或者其他原因导致的gpio拉低,如果是低电平,说明gpio45都被拉低,有设备插入插槽且接触良好。中断程序将gpio6设置为方波输出,让发光二极管闪烁,提醒操作人员不能拔出设备,然后将gpio123设置为高电平输出,打开pcie插槽的3.3v辅助电源、3.3v电源和12v电源,然后读取插槽设备的父级桥,为设备分配bus号资源,等待pcie设备和父级桥linktraining结束,training结束后,检查mmio资源当中是否有足够资源分配给pcie设备,如果有资源,根据基地址计算,为设备分配内存资源、io资源,为设备分配中断,如果没有资源,首先修改tolm(低内存顶端寄存器),将值减小,增加mmio的大小,然后设置mmiorule寄存器来说明mmio的大小,修改mtrr(内存类型范围寄存器)寄存器,设置新增的mmio为不可缓冲类型,然后更新e820表,说明当前所有内存的类型使用情况,然后再分配内存、io和中断资源,分配完资源后,打开内存、io资源的开关,让资源处于可使用状态。最后,将gpio6设置为高电平输出,让发光二极管常亮,表明设备可以正常工作了。 pcie设备热拔出程序设计: 同热插入程序一样,如图3所示,首先要初始化gpio1236设置为输出低点平,发光二极管熄灭,然后设置gpio457为输入功能,打开gpio47触发smi中断功能,然后bios程序进入non-acpi环境,包括gpio初始化之后bios运行过程、dos系统等。gpio7一直输入高电平,如果操作人员有拔出pcie设备的需求,首先按下提示按钮,会使gpio7产生一个低电平,将触发smi中断程序。中断程序中,首先将gpio6设置为输出方波,使发光二极管闪烁,提醒操作人员不能拔出设备,然后程序通过设备的命令寄存器禁止内存和io空间,再在父级桥里面禁止与设备的链接,将gpio123设置为输出低电平,关闭插槽的电源,释放掉设备所需要的内存、io和中断资源,最后将gpio6设置为低电平,让发光二极管熄灭,表明此时可以将设备安全移除了。这里释放掉的内存资源并没有给系统使用,仍然保留mmio属性,方便再次插入设备时候优先分配这部分资源。 上述方法通过简单的硬件线路设计和bios程序设计,能在non-acpi环境下有效地支持pcie设备热插拔功能,弥补了non-acpi环境下功能的缺失,满足操作人员的需求。而且硬件线路设计简单,不会增加主板的成本,也不会增加开发调试时间。 本发明所涉及的英文缩写的技术术语的解释: bios(basicinputoutputsystem):基本输入输出系统,主要用于计算机开机过程中各种硬件设备的初始化和检测。 pch(platformcontrollerhub):intel公司的集成南桥。 pcie(pci-express):一种高速串行总线接口技术标准。 gpio(generalpurposeinputoutput):通用输入/输出。 acpi(advancedconfigurationandpowermanagementinterface):高级配置与电源管理接口,操作系统应用程序管理所有电源管理接口,non-acpi环境,即不支持acpi标准的环境。 usb(universalserialbus):通用串行总线。 sata(serialadvancedtechnologyattachment):串行ata接口规。 dos(diskoperatingsystem):磁盘操作系统。 smi(systemmanagementinterrupt):系统管理中断。 mmio(memorymappingi/o):内存映射i/o。 tolm(topoflowmemory):低内存顶端。 mtrr(memorytyperangeregisters):内存类型范围寄存器。 以上内容是结合具体的优选实施方式对本发明所作的进一步详细说明,不能认定本发明的具体实施只局限于这些说明。对于本发明所属技术领域的普通技术人员来说,在不脱离本发明构思的前提下,还可以做出若干简单推演或替换,都应当视为属于本发明的保护范围。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。

文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/45753.html