半导体集成电路可靠性测试的内容分享 随着半导体集成电路制造技术的快速进步和发展,以硅基单片数字为标志的超大规模集成电路体积不断缩减,电路结构以及制造工艺愈加繁杂。其可靠性受到工艺误差以及相关因素的影响也开始加重。可靠性工程必须运用当前的现代科学技术,对产品功能进行系统考量,运用专门性的技术手段,降低产品故障率,最终确保系统运行良好。在集成电路的晶圆级可靠性测试中,使用非常普遍的测试类别主要是热载流注入测试、电迁移测试等等其他一些相关的测试项目。 栅氧化层测试技术与数据处理方法 在彻造集成电路的过程中,栅氧化层起到相当关键的作用,随着不断扩大的集成电路规模,其厚度也不断增加,同时对着不断减小的器件体积提厚度也在不断减小。因为栅氧化层的关键地位,其可靠性问题也得到了极大的,在遇到的问题中较为常见的是栅氧化层的介质穿击和缺陷密度等问题。针对栅氧化层开展的可靠性测试一般是在同一个时间结点以联系介质为对象进行斜坡电压测试和穿击测试。 1、斜坡电压测试 在可靠性测试中,斜坡电压测试是把线性斜坡电压添加到栅极上,直至电压击穿氧化层。不同于斜坡电压测试,斜坡电流测试是在栅极上通过一定指数斜坡电流的添加,直至把氧化层击穿。这两种测试方法都是对栅氧化层缺陷密度进行测量的。比如,在一般情况下,对斜坡电压的测试,是在一定电压标准范围内开展的,如果电压击穿氧化层时的电压比设定的电压标准要小,就可以认为氧化层中具有缺陷,并进一步可以确认册氧化层是无效的。在JESD35标准中,在Poisson分布基础上的成品率公式可以计算得出相应的缺陷密度:Y=e-DoA,其中,成品率用Y来表示,也即是有效样品与总测试样品的比率,受测样品面积用A表示,缺陷密度用Do表示。对成本经过斜坡电流和电压的大量测试之后,通过计算可以得出成品率数值,并利用测试样本面积对缺陷密度进行计算。一旦缺陷密度与设置标准不符,就认定测试失败。 2、介质击穿的实验 时间相关介质击穿也既为介质击穿实验。其测试步骤为:把比栅氧化层小的本征加到栅极之上,对然不能导致本征击穿,但是氧化层在电应力的事假过程中有一定的缺陷出现,在这种情况下,击穿现象会在一段时间之后出现。在评定集成电路可靠性测试的过程中,棚氧介质在相同时间下的击穿是其主要限制因素,一般而言,氧化硅电场超限,由于过高的电流导致电荷累积反应才会造成击穿现象的出现。在目前,氧化层的击穿主要分为两个阶段:构建磨损和击穿。在构建磨损阶段,在电应力运作之下的二氧化硅界面会不断累积其中的缺陷,当量变引起质量时,有一些缺陷数会率先到达临界值,进入击穿阶段,并基于电热的双重反应,迅速击穿氧化层。所以棚氧化层击穿测试的时间和周期是由第一个阶段的持续时间决定的。 热载流子注入技术与数据处理 1、热载流子注入测试 在集成电路可靠性测试内,晶圆级别检测的主要作用是进行特载流子注入检测。利用变焦费米能级与实际量进行热载流子检测。在集成电路构件内,利用过源电压遗漏出现的载流子漏电极限,主要因为在较大电场强度遗漏四周,载流子流入较大电场范围下,高能能量子就会转到热载流子。同时,利用电子的相互撞击让热载流子产生的电子空穴使电力更深度的产生。 2、数据处理 集成构建内,根据有关要求对热载流子的数据处理方法与全部检测阶段进行了明确规定。例如:1.8V为MOS管的工作电压,stress电压区间在2–3V。通常状况下分析,结合时间变化量数值将专项幂函数。通常情况下,热载流子检测后,需要根据预定的参数进行电性数值变化量计算,进而得出预定时间与参数。

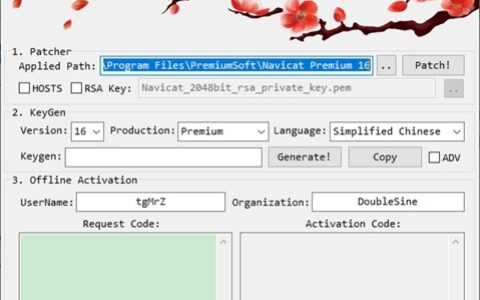

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/24443.html