计算机组成原理总结-3.2.存储系统(字位扩展)

本章的主要内容是对存储器容量的扩充,SRAM、DRAM和ROM都可以进行容量扩展。那么我们为什么要进行容量扩展呢?其中主要原因是因为单个存储芯片的容量有限,而实际的存储器是由多个芯片扩展而成。

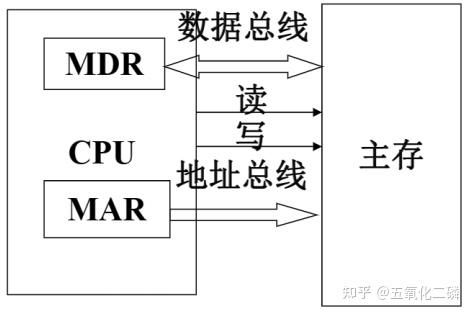

存储器(存储芯片)与CPU连接,其中主要是通过数据、地址、控制三总线连接。存储芯片与CPU是多对一的关系,并不是一一对应连接。

我们在扩展过程中,主要存储芯片与CPU的外部引脚连接。存储器容量的主要扩充方式有:位扩展、字扩展和字位扩展

# 1.存储芯片与CPU的引脚:

存储芯片的外部引脚有:

数据总线:位数与存储单元字长相同,用于传送数据信息

地址总线:位数与存储单元个数为2^n关系,用于选择存储单元

读写信号/WE:决定当前对芯片的访问类型

片选信号/CS:决定当前芯片是否正在被访问

CPU与存储器连接的外部引脚:

数据总线:位数与机器字长相同,用于传送数据信息

地址总线:位数与系统中可访问单元个数为2^n的关系,用于选择访问单元

读写信号/WE:决定当前CPU的访问类型

访存允许信号/MREQ:决定是否允许CPU访问存储器

# 2.位扩展

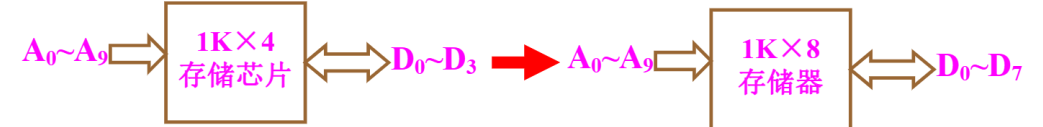

位扩展正如其名字,扩展它的位数,存储单元数不变,每个单元的位数(字长)增加

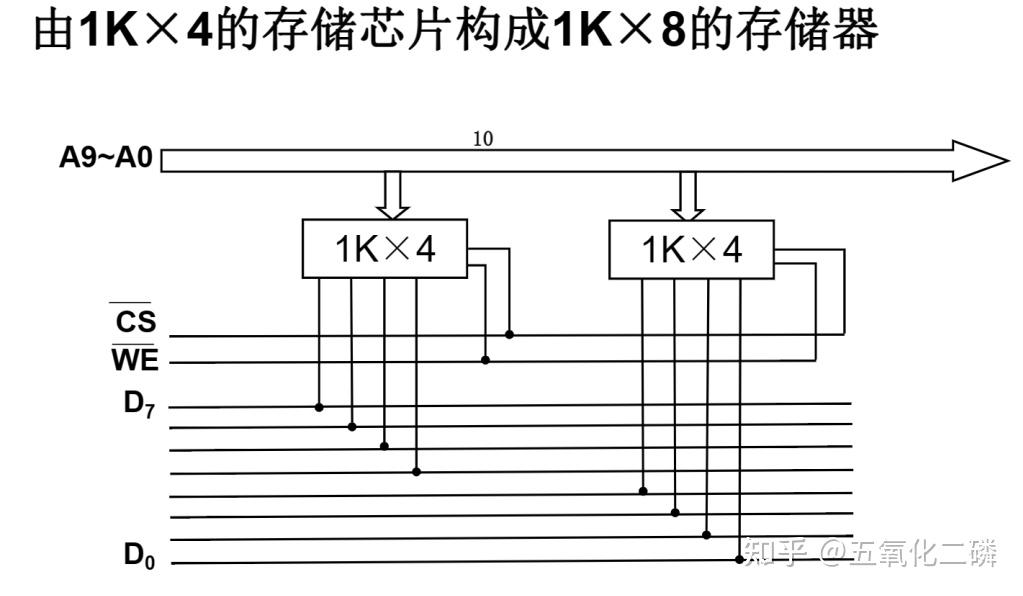

例如:由1K*4的存储芯片构成1K*8的存储器

存储芯片与CPU引脚的连接中,地址线不变,数据线分别与CPU数据线的不同位连接,各芯片片选及读写信号直接与CPU的访存及读写信号连接

注:CPU是对各位扩展芯片的同一单元同时访问

下面是扩展方式的细节,其中地址没有发生变化,位扩展增加。

# 3.字扩展

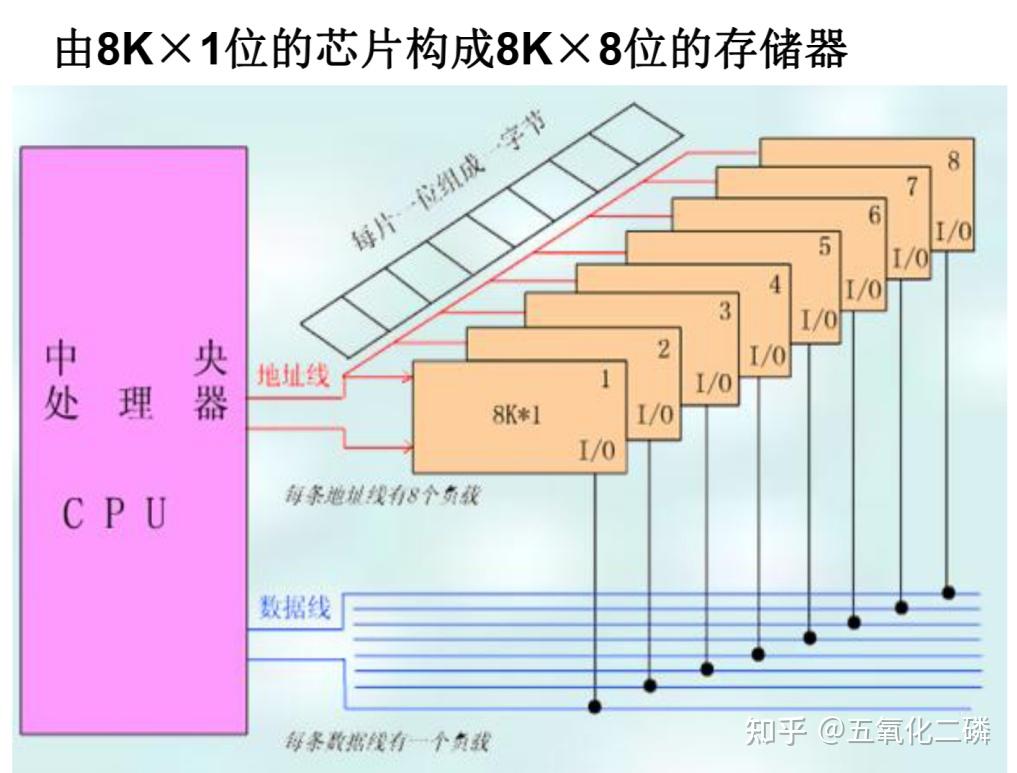

字扩展是每个单元的位数不变,总的单元个数增加,刚好与位扩展相反。

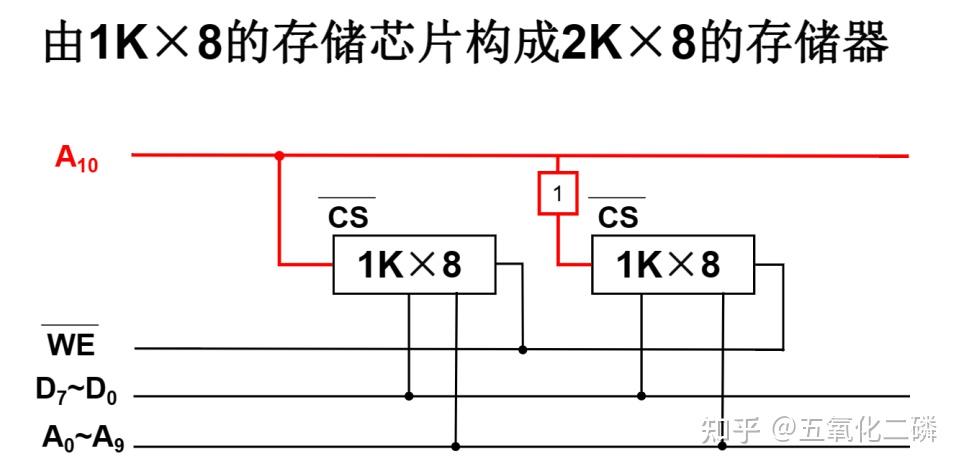

例如:用1K*8的存储芯片构成2K*8的存储器

存储芯片与CPU的引脚连接中,各芯片的地址线与CPU的低位地址线直接连接,数据线中各芯片的数据线直接与CPU的数据线连接,各芯片的读写信号直接与CPU的读写信号连接,各芯片的片选信号由CPU的高位地址和访存信号产生。

注:CPU对该存储器的访问是对某一字扩展芯片的一个单元的访问

低位的地址线与各芯片的地址线并联,多余的高位地址线用来产生相应的片选信号

下面我们用16K*8的芯片构成64K*8的存储器:

为什么地址线是14根呢?因为存储单元为16K=16*2^10=2^14

数据线便是存储字长

我们需要4个存储芯片来构成存储器的地址分配:

第一片:00 00 0000 0000 0000 00 11 1111 1111 1111,即0000H-3FFFH

第二片:01 00 0000 0000 0000 01 11 1111 1111 1111,即4000H-7FFFH

第三片:10 00 0000 0000 0000 10 11 1111 1111 1111,即8000H-BFFFH

第四片:11 00 0000 0000 0000 11 11 1111 1111 1111,即C000H-FFFFH

# 4.字位扩展

将字扩展和位扩展结合起来,也就是单元位数和总的单元个数都增加,便是字位扩展。

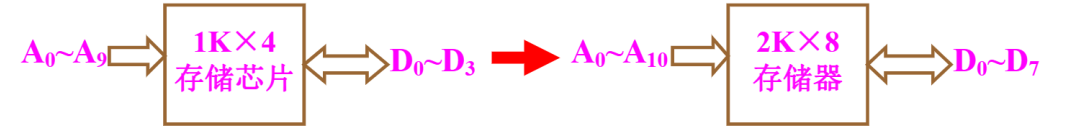

例如:用1K*4的存储芯片构成2K*8的存储器

扩展方法:

先进行位扩展,形成满足位要求的存储芯片组;

再使用存储芯片组进行字扩展

也就是先变宽,再变长

例如:用L*K的芯片构成M*N的存储系统,所需要的芯片数为__

答:MN/LK

下面我们用几个具体的例子对上述问题进行一个解释,请各位小伙伴先思考再看答案哦。

例:用2M*8的SRAM芯片构成一个16M*8的存储器

(1)需要几块芯片?如何进行扩展?

(2)数据线怎么连?

(3)地址线怎么连?

(4)控制线怎么连?

做题思路:

1.审题时首先确定所需扩展的类型,选择合适的存储芯片,扩展原则是:尽量做简单的扩展

(位扩展—字扩展—字位扩展)

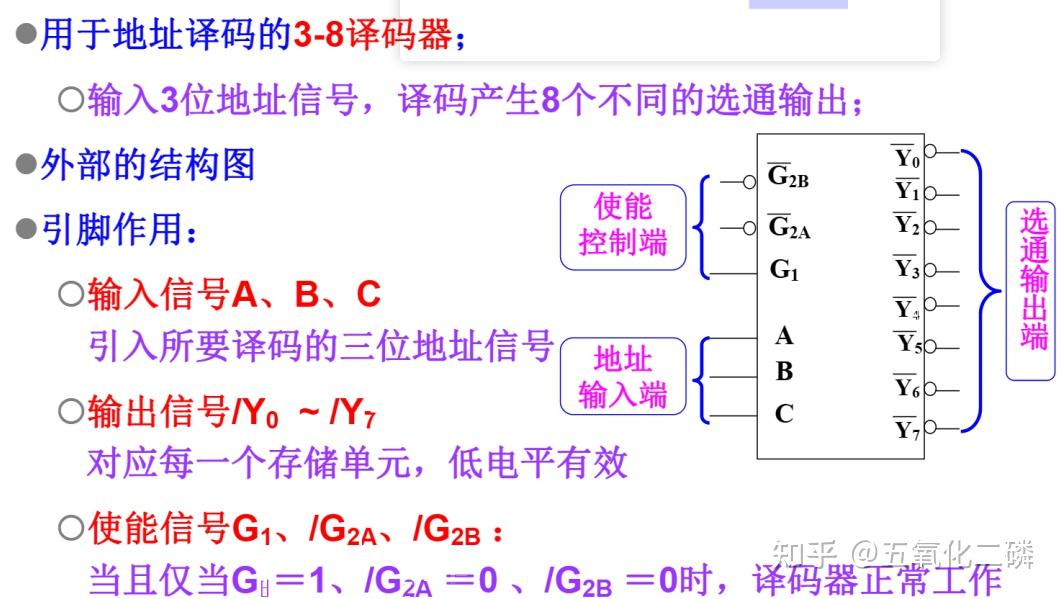

2.分析存储芯片和CPU引脚的特性(地址范围、地址线数据、容量要求等)确定引脚连接,尤其在进行字扩展时,特别注意片选信号的产生,通过38译码器或者24译码器进行选择。

答:

(1)8片2M*8的SRAM芯片进行字扩展

(2)各芯片的数据线均直接与CPU的8位数据总线连接

(3)各芯片的地址线均直接与CPU的最低21位地址线连接

(4)读写信号直接连接,剩余高3位地址线和/MREQ和译码产生各芯片的片选信号/CS连接

至于74LS138译码器,我们在数字逻辑中已经掌握,这里便不再阐述(没有学过的小伙伴也不要着急,可以在网上搜一下简单教程)

这是38译码器的一些功能特性

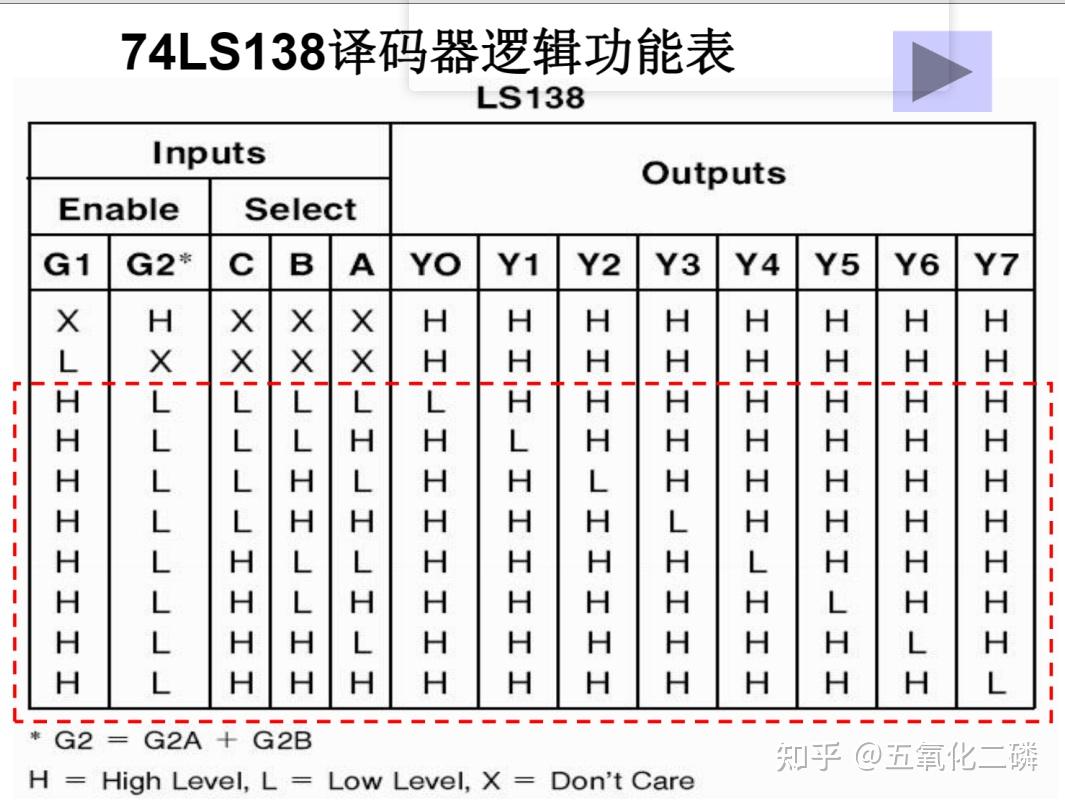

这是38译码器的逻辑功能表,大家可以自行查询。

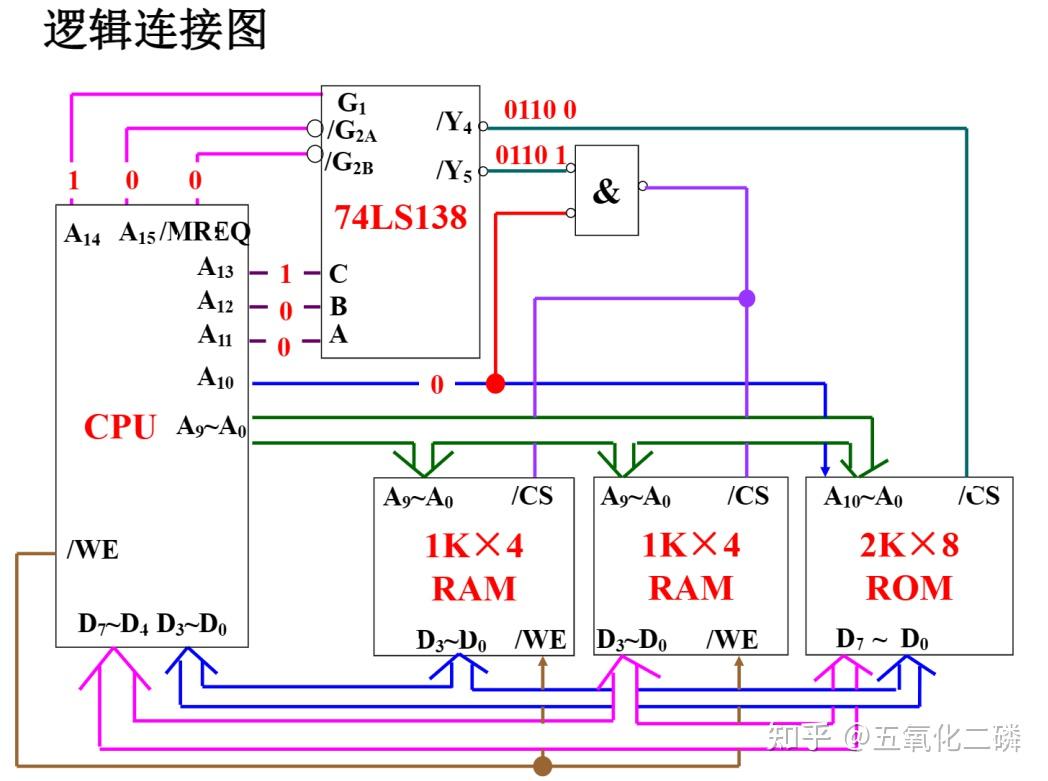

例子:我们可以用一个更加复杂的案例来将上述知识点进行综合。

我们首先需要对存储器地址段进行分析:

6000H:0110 0000 0000 0000

67FFH:0110 0111 1111 1111

上边是系统程序区,我们不难发现存储大小为2^11=2K,则为2K*8位

6800H:0110 1000 0000 0000

6BFFH:0110 1011 1111 1111

上边是用户程序区,存储大小为2^10=1K,则为1K*8位

存储芯片我们可以选择:

系统程序区:1片2K*8 ROM

用户程序区:2片1K*4 RAM,做位扩展,

最后将系统程序区和用户程序区做一个字扩展

2K*8 ROM:

地址线:A0 – A10

数据线:D0 – D7

控制线:/CS(A15 – A11 (0110 0))

1K*4 RAM:

地址线:A0 – A9

数据线:D0 – D3

控制线:/CS, /WE(A15 – A10 (0110 10))

CPU:

地址线:A0 – A15

数据线:D0 – D7

控制线:/WE, /MREQ(A15 – A12 (0110))

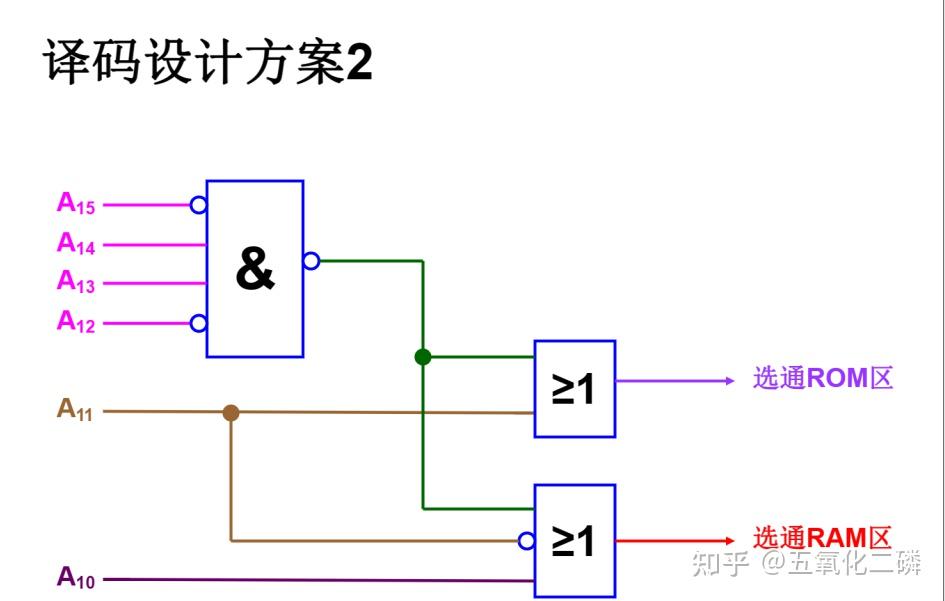

应当使用A15-A11作为地址译码信号,产生各存储芯片的/CS

存储器设计的连接要点:

地址线的连接:用CPU的低位地址线与芯片地址线直接连接

数据线的连接:用CPU的对应位数据线与芯片的数据线直接连接

读写控制信号的连接:用CPU的读写控制信号直接与存储芯片直接连接

片选线连接:一般用CPU的高位地址线和CPU的访存允许控制信号/MREQ,经过译码器姨妈后产生各芯片的片选信号,这也是最关键的地方

上边的总结可能不是很全,之后会定期更新补充,如果有错误的地方还请大家指正!

看到这里的同学,记得点赞收藏加哦~

以后的内容会更加精彩!

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/95235.html