【百年教育职业培训中心】EDA技术与Verilog-章节资料考试资料-杭州电子科技大学 报名本机构合作学校,赠送复习资料,复习课程,确保录取。并且可以申请学校奖学金500元~1500元不等! 答案:微信搜索【渝粤教育】公众号 技术与Verilog-杭州电子科技大学[火 单元测验-第1章 1、【单选题】用逻辑门描述一个全加器,是属于那个设计层次: A、晶体管级 B、物理级 C、门级 D、系统级 2、【单选题】module cnt32( input clk, output reg[31:0] q);always @(posedge clk) q = q + 1’b1;endmodule上述HDL程序是用什么语言写的? A、 C++ B、Java C、Verilog D、 VHDL 3、【单选题】ModelSim是那种EDA工具: A、 综合器 B、下载器 C、仿真器 D、适配器 4、【单选题】Verilog RTL代码经过综合后生成: A、门级网表 B、二进制指令序列 C、行为及代码 D、PCB 5、【单选题】EDA发展历程,下列中那个次序是对的? A、电子CAD→电子CAE→EDA B、ESDA→电子CAD→电子CAE C、CPLD→简单PLD→FPGA D、电子CAE→机械CAD→EDA 6、【单选题】“接近真实器件运行特性的仿真,仿真文件中己包含了器件硬件特性参数,因而,仿真精度高。”这句说的是那种仿真: A、时序仿真 B、功能仿真 C、硬件仿真 D、软件仿真 7、【多选题】Verilog可以完全完成下列哪些设计层次的描述 A、电子系统级 B、RTL级 C、门级 D、版图级物理级 8、【多选题】下列哪些是可以借助计算机上的EDA软件来完成的: A、逻辑化简 B、综合 C、适配 D、自动布局布线 E、焊接 F、设计分割 G、办公自动化 9、【多选题】常见的HDL语言有: A、Python B、 Java C、SystemVerilog D、Verilog E、VHDL 10、【多选题】下列设计流程次序说明中,那些是正确的: A、设计输入在综合前面 B、适配早于综合 C、仿真在设计输入前面 D、 硬件测试在下载后面 11、【多选题】在FPGA设计流程中,下列哪些是常用EDA工具: A、设计输入器 B、仿真器 C、综合器 D、下载器(软件端) E、适配器 12、【多选题】Quartus具有哪些类型EDA工具的功能: A、综合器 B、下载器 C、仿真器 D、适配器 13、【多选题】IP是EDA技术中不可或缺的一部分,下列哪些是常见处理器IP A、 PCIe B、ARM Cortex-M33 C、MIPS D、NiosII E、RISC-V RV32I F、IEEE 1284 14、【多选题】SOPC包含: A、 CPU Core B、Interfaces & Peripherals C、Memory D、Software 15、【判断题】Verilog可以描述门级网表 A、正确 B、错误 16、【判断题】EDA的中文含义是电子设计自动化 A、正确 B、错误 17、【判断题】EDA是英文Electronics Design Automation的缩写 A、正确 B、错误 18、【判断题】HDL是Hardware Description Language的缩写 A、正确 B、错误 19、【判断题】Verilog可以描述门级网表 A、正确 B、错误 20、【判断题】Verilgo程序编写设计流程中的第一步:HDL文本输入 A、正确 B、错误 21、【判断题】整个综合过程就是将设计者在EDA平台上编辑输入的HDL文本、原理图或状态图形描述,依据给定的硬件结构组件和约束控制条件进行编译、优化、转换和综合,最终获得门级电路甚至更底层的电路描述网表文件。 A、正确 B、错误 22、【判断题】EDA工具不是一种软件,而是一个机械工具 A、正确 B、错误 23、【判断题】在EDA技术术语中,IP是Internet Protocol(网际互连协议)的缩写 A、正确 B、错误 24、【判断题】硬IP是HDL源码形式提供的,很容易进行设计修改。 A、正确 B、错误 25、【判断题】HDL语言已经成熟,近十年来,没有出现新的HDL语言 A、正确 B、错误 26、【判断题】C语言综合已经渐渐成为可能,已经出现可以使用的C综合工具 A、正确 B、错误 27、【判断题】Verilog综合的最后输出是x86的二进制机器吗指令序列 A、正确 B、错误 28、【判断题】Verilog语法类似于C语言 A、正确 B、错误 29、【判断题】支持RISC-V处理器RV32I指令集的CPU Verilog源代码可以认为是IP A、正确 B、错误 30、【判断题】SOC是SYSTEM ON A CHIP的缩写 A、正确 B、错误 单元测验-第2章 1、【单选题】以下哪个可编程器件是基于与阵列可编程或阵列不可编程的原理: A、PLA B、FPGA C、PROM D、PAL 2、【单选题】下列对FPGA结构与工作原理的描述错误的是: A、 基于SRAM的FPGA器件,在每次掉电后会丢失里面已经下载的设计; B、在Intel的器件中,CYCLONE IV系列属FPGA结构; C、 FPGA是基于查找表结构的可编程逻辑器件; D、 FPGA全称为复杂可编程逻辑门器件。 3、【单选题】以下关于CPLD的描述正确的是: A、可编程逻辑器件 B、掉电程序会丢失 C、需要使用配置芯片 D、基于查找表 4、【单选题】下列关于FPGA可编程原理的说法,那个是正确的_ ____。 A、基于LUT结构 B、基于与阵列可编程 C、基于或阵列可编程 D、基于乘积项逻辑可编程 5、【多选题】MAX3000A主要包括了哪几个主要部分? A、逻辑阵列块 B、宏单元 C、扩展乘积项 D、可编程连接阵列 E、I/O控制块 6、【多选题】下面哪些器件属于复杂PLD: A、PLA B、FPGA C、PROM D、CPLD 7、【多选题】从结构上看,PLD器件能够分为以下几类结构: A、基于查找表结构 B、基于与阵列可编程 C、基于或阵列可编程 D、基于乘积项逻辑可编程 8、【多选题】以下可编程器件原理基于与或阵列的有: A、PLA B、FPGA C、PROM D、GAL 9、【多选题】以下关于FPGA的描述正确的是: A、可编程逻辑器件 B、掉电程序会丢失 C、需要使用配置芯片 D、基于查找表 10、【多选题】在JTAG边界扫描测试,以下关于边界扫描I/O引脚功能的描述正确的是: A、TDI测试数据输入 B、TDO测试数据输出 C、TEN测试使能 D、TCK测试时钟输入 11、【多选题】JTAG接口有哪些功能: A、软硬件测试 B、 编程下载 C、在线逻辑分析 D、仿真 12、【多选题】FPGA配置方式包括: A、JTAG B、PROM C、PAL D、PS E、AS 13、【判断题】目前大多数CPLD采用了Flash工艺。 A、正确 B、错误 14、【判断题】JTAG是IEEE定义的边界扫描测试规范。 A、正确 B、错误 15、【判断题】基于SRAM的FPGA具有掉电易失性,对该类器件的编程一般称为配置。 A、正确 B、错误 16、【判断题】简单PLD器件都是基于与或阵列。 A、正确 B、错误 17、【判断题】CPLD编程和FPGA配置可以使用专用的编程设备,也可以使用下载电缆。 A、正确 B、错误 18、【填空题】PLD的中文全称是什么? A、 19、【填空题】什么是OLMC? A、 20、【填空题】CPLD的中文全称是什么? A、 21、【填空题】FPGA的中文全称是什么? A、 作业-第3章 单元测验-第3章 1、【单选题】任一可综合的最基本的模块都必须以什么关键词为开头: A、assign B、always C、module D、endmodule 2、【单选题】下列哪个数字最大: A、 4’b1101 B、8’h16 C、8’d18 D、1001 3、【单选题】Y=a;是: A、连续赋值语句 B、阻塞式赋值 C、非阻塞式赋值 D、条件语句 4、【单选题】module EXAPL(R);parameter S=4;output [2*S:1] R;integer A;reg [2*S:1] R;always@(A) beginR=A;endendmoduleR经过A赋值后是多少位的: A、32 B、16 C、8 D、4 5、【单选题】output signed [7:0] y;input signed [7:0] a;assign y=(a2);若a=,则输出y等于: A、00 B、 C、 D、 6、【单选题】下面哪一个不是标识符: A、模块名 B、信号名 C、关键词 D、端口名 7、【单选题】下列哪一个是正确的: A、(3==5)=1 B、(3’bx10===4’b0x10)=0 C、(4’b0z10!==4’b0z10)=1 D、(8!=9)=0 8、【单选题】A=4’b1011, B=4’b1000,则下列正确的是: A、(A>B)=1 B、(A<B)=1 C、(A>15)=1 D、 (B<11)=0 9、【单选题】若底层的模块语句和参数表述为module SUB #(parameter S1=5, parameter S2=8, parameter S3=1) (A,B,C);在上层的例化语句中的表述为SUB #(.S1(7), .S2(3), .S3(9)) U1(.A(AP), .B(BP), .C(CP)); 则例化后,S2给定的值为: A、8 B、3 C、9 D、7 10、【多选题】下面那些是Verilog的关键字 A、input B、a C、module D、y 11、【多选题】下列哪些是Verilog中的循环语句关键词: A、for B、parameter C、while D、repeat 12、【判断题】位置关联法,关联表述的信号位置可以不固定: A、正确 B、错误 13、【判断题】对于BCD码加法器的设计,如果低位BCD码的和大于等于9,则使和加上6,且有进位: A、正确 B、错误 14、【判断题】assign引导的连续赋值语句属于并行赋值语句吗 A、正确 B、错误 15、【判断题】在过程语句always@引导的顺序语句中, 被赋值信号不一定是reg型变量 A、正确 B、错误 16、【判断题】下列两项的值是一样的:4’d94’b1001 A、正确 B、错误 作业-第4章 单元测验-第4章 1、【单选题】时钟上升沿敏感的关键词是: A、always B、module C、posedge D、negedge 2、【单选题】含清0控制的锁存器module LATCH2(CLK,D,Q,RST);output Q;input CLK,D,RST;assign Q=(!RST)? ____:(CLK?D:Q);endmodule空格处应该填入: A、CLK B、D C、Q D、0 3、【单选题】下列哪一个表述是正确: A、always@(posedge CLK or RST) B、always@(posedge CLK or negedge RST or A) C、always@(posedge CLK or D or Q) D、always@(posedge CLK or negedge RST) 4、【单选题】module CNT4 (CLK,Q); output [3:0] Q; input CLK;reg [3:0] Q ;always @(posedge ____)Q = Q+1 ; endmodule A、CLK B、output C、[3:0] D、Q 5、【单选题】module SHFT1(CLK,LOAD,DIN,QB); output QB; input CLK,LOAD; input[7:0] DIN; reg[7:0] REG8; always @(posedge CLK ) if (LOAD) REG8=DIN ; else ____=REG8[7:1]; assign QB = REG8[0] ; endmodule空格处应该填入: A、LOAD B、DIN C、QB D、REG8[6:0] 6、【单选题】含同步复位控制的D触发器module DFF2(input CLK, input D, input RST, output reg Q);always@(posedge CLK)Q=____?0:D;endmodule空格处应该填入: A、CLK B、RST C、Q D、D 7、【单选题】含清0控制的锁存器module LATCH3(CLK,D,Q,RST);output Q;input CLK,D,RST;____ Q;always@(D or CLK or RST)if (!RST) Q=0;else if (CLK) Q=D;endmodule空格处应该填入: A、reg B、input C、RST D、CLK 8、【单选题】module CNT4(CLK,Q); output [3:0] Q; input CLK;reg ____ Q1 ; always @(posedge CLK)Q1 = Q1+1 ;assign Q = Q1; endmodule空格处应该填入: A、reg B、CLK C、Q1 D、[3:0] 9、【单选题】module FDIV0(input CLK, RST,input [3:0] D, output PM, output [3:0] DOUT);reg [3:0] Q1; reg FULL;wire LD;always@(posedge CLK or negedge RST) if (!RST) begin Q1=0; FULL=0; end else if (LD) begin Q1=D; FULL=1; end else begin Q1=Q1+1; FULL=0; endassign LD=(Q1==4’b1111); assign PM=FULL; assign DOUT=Q1;endmodule该模块实现的功能是: A、同步加载计数器 B、异步加载计数器 C、同步清零加载计数器 D、异步清零加载计数器 10、【多选题】下列哪些是正确的: A、如果将某信号定义为边沿敏感时钟信号,则必须在敏感信号列表中给出对应的表述 B、若将某信号定义为对应于时钟的电平敏感的异步控制信号,在always过程结构中必须明示信号的逻辑行为 C、若将某信号定义为对应于时钟的同步控制信号,则绝不可以以任何形式出现在敏感信号表中 D、敏感信号列表中可以出现混合信号 11、【多选题】module SHFT1(CLK,LOAD,DIN,QB); output QB; input CLK,LOAD; input[7:0] DIN; reg[7:0] REG8; always @(posedge CLK ) if (LOAD) REG8=DIN ; else REG8[6:0]=REG8[7:1]; assign QB = REG8[0] ; endmodule该程序实现的功能为: A、右移移位寄存器 B、左移移位寄存器 C、含同步并行预置功能 D、含异步并行预置功能 12、【多选题】module SHIF4(DIN,CLK,RST,DOUT);input CLK,DIN,RST; output DOUT;reg [3:0] SHFT;always@(posedge CLK or posedge RST)if (RST) SHFT=4’B0;else begin SHFT=(SHFT1);SHFT[3]=DIN;endassign DOUT=SHFT[0];endmodule该程序实现的功能是: A、左移移位寄存器 B、右移移位寄存器 C、同步清零 D、异步清零 13、【判断题】异步复位是指复位信号依赖于时钟信号 A、正确 B、错误 14、【判断题】同步复位是指复位信号独立于时钟信号 A、正确 B、错误 15、【判断题】对于锁存器,当时钟CLK为高电平时,输出Q才随D输入的数据而改变;而当CLK为低电平时将保存其在高电平时锁入的数据。 A、正确 B、错误 16、【判断题】拥有单一主控时钟的时序电路属于异步时序电路 A、正确 B、错误 17、【判断题】对于实用加法计数器,同步加载信号LOAD独立于时钟 A、正确 B、错误 18、【判断题】Vn是向左移动n位 A、正确 B、错误 19、【判断题】对于同步加载计数器,加载信号LD依赖于时钟信号。 A、正确 B、错误 20、【判断题】对于含清零控制的锁存器,异步清零信号依赖于时钟信号。 A、正确 B、错误 21、【判断题】在always过程语句中,若定义某变量为异步低电平敏感信号,则在if条件语句中应该对敏感信号表中的信号有匹配的表述 A、正确 B、错误 22、【填空题】module fdiv1(CLK,PM,D,DOUT,RST);input CLK, RST; ____ [3:0] D; output PM; output [3:0] DOUT;____ [3:0] Q1; reg FULL;wire LD;always@(posedge CLK or ____ LD or negedge RST) if (!RST) begin Q1=0; FULL=0; end else if (LD) begin Q1=D; FULL=1; end else begin Q1=Q1+1; FULL=0; endassign ____=(Q1==4’b0000); assign PM=FULL; assign DOUT=Q1;endmodule空格处应该填入:A. LDB. posedgeC. inputD. reg(答案中以空格分隔 比如 D C A B) A、 单元测验-第5章 1、【单选题】编译时出现了以下错误提示:Error (10170): Verilog HDL syntax error at dec4_16x.v(5) near text 3; expecting an identifier代码中的第5行为“output reg[15:0] 3yn”这里代码的错误可能是什么? A、变量类型定义错误 B、赋值方式错误 C、标识符定义不合规范 D、语句结尾漏了“:” 2、【单选题】编辑矢量波形文件进行仿真时,需要编辑的是 A、所有输入信号 B、所有输出信号 C、全部信号 D、任选部分信号 3、【单选题】从代码always@(posedge CLK or negedge RST)可以看出: A、RST是同步信号,高电平有效 B、RST是异步信号,低电平有效 C、 RST是同步信号,下降沿有效 D、RST是异步信号,下降沿电平有效 4、【单选题】编译时出现了以下错误提示:Error (10170): Verilog HDL syntax error at dec4_16x.v(5) near text 3; expecting an identifier代码中的第5行为“output reg[15:0] 3yn”这里代码的错误可能是什么? A、变量类型定义错误 B、 赋值方式错误 C、标识符定义不合规范 D、语句结尾漏了“:” 5、【单选题】若欲将仿真信号的数据显示格式设置为16进制,应选择属性为: A、Octal B、Hexadecimal C、Unsigned Decimal D、Fractional 6、【单选题】错误提示:Error (12007): Top-level design entity CNT4b is undefined可能是以下哪种错误; A、变量类型定义错误 B、变量CNT4b未定义 C、未设置顶层实体 D、顶层实体模块未定义 7、【单选题】下列代码含义为( ),“input clk /*synthesis chip_pin= “G21”” A、定义变量clk B、设置时钟变量 C、将时钟信号的引脚锁定到G21 D、同步clk引脚到G21 8、【单选题】下列代码含义为( ),(*synthesis,keep*) wire i; A、定义变量i为net类型 B、规定变量i为测试端口,需要保留 C、综合优化变量i D、为变量i定义引脚锁定 9、【多选题】在使用LPM定制ROM时调用的数据文件的格式有: A、 verilog B、mif C、Hex D、vhdl 10、【多选题】QuartusII支持哪些设计输入方式: A、文本文件 B、原理图文件 C、状态机文件 D、矢量波形文件 11、【多选题】引脚锁定可以用下列哪些方法实现 A、利用引脚属性定义,在verilog代码中直接表述实现引脚锁定。 B、在quartusII中打开pin planer直接锁定 C、通过tcl脚本 D、通过导入引脚锁定文件 12、【多选题】下列属于全程编译的处理操作是: A、输入文件的排错 B、数据网表文件的提取 C、逻辑综合和适配 D、输出仿真结果 13、【多选题】按照仿真的电路描述级别的不同,HDL仿真器可以完成: A、门级仿真 B、行为级仿真 C、RTL级仿真 D、系统级仿真 14、【多选题】下列属于FPGA的编程下载文件的有 A、.sof文件 B、.qpf文件 C、.jic文件 D、.pof文件 15、【多选题】确定采样深度,需要考虑的有 A、待测信号的采样要求 B、总的信号数量 C、存储器资源 D、待测信号的变化频率 16、【多选题】在使用LPM定制ROM时调用的数据文件的格式有: A、verilog B、mif C、Hex D、vhdl 17、【多选题】下列那种技术是基于JTAG技术构建的( ) A、SignalTap II B、ModelSim门级仿真 C、Synplify综合器综合技术 D、In-System Source and Probe E、FPGA在线配置技术 F、In-System Memory Content Editor 18、【判断题】一个工程中可以包括多个设计文件。 A、正确 B、错误 19、【判断题】一个工程中只能有一个顶层文件,顶层文件不可更改 A、正确 B、错误 20、【判断题】仿真的主要目的是要了解设计结果是否满足原设计的要求。 A、正确 B、错误 21、【判断题】电路设计完成后,为了实现硬件下载,需要完成下列步骤:①安装下载器驱动②引脚锁定③编译④编程下载 A、正确 B、错误 22、【判断题】引脚锁定与具体的目标芯片型号无关。 A、正确 B、错误 23、【判断题】为了使FPGA的下载文件掉电之后不丢失,可以将编程文件烧到FPGA的配置芯片里保存。FPGA器件每次上电时,作为控制器从配置器件EPCS主动发出读取数据信号,从而把EPCS的数据读入FPGA中,实现对FPGA的编程。 A、正确 B、错误 24、【判断题】采用SignalTapII进行电路分析的时候,采样深度越大越好 A、正确 B、错误 25、【判断题】待测信号中的每一个信号的采样深度都是一样的。 A、正确 B、错误 26、【判断题】原理图输入和文本输入不能混合在一起使用。 A、正确 B、错误 27、【判断题】如果想在仿真中了解模块内部的某个信号的变化,可以对该信号定义keep属性。 A、正确 B、错误 作业-实验1报告 单元测验-实验1 1、【单选题】下列代码实现的功能为:t = a ~^ k; A、t=ak B、t=a同或B C、t=a异或b D、t左移ak位 2、【单选题】根据以下代码,当c=0时,x的值将等于( ),if(c) x = k;else x = 1’bz; A、高电平 B、低电平 C、高阻 D、未知 作业-第6章 单元测验-第6章 1、【单选题】always @(A,B) beginM1 = A ; M2 = BM1; Q = M1|M2; end 当A和B同时从0变为1后,M1,M2与Q分别为多少: A、0, 0, 0 B、1, 1, 1 C、1, 0, 0 D、1, 1, 0 2、【单选题】beginY1 = #5 A^B;Y2 = #4 A|B;Y3 = #8 AB;end以上语句共耗时多少个时间单位: A、5 B、4 C、17 D、8 3、【单选题】module andd(A,B,Q); output Q ; input A,B; reg Q; always @(A,B ) if (A==0) if (B==0) Q=0; else Q=1;endmodule其中,else Q=1;与哪句语句对应: A、always @(A,B ) B、if (A==0) C、if (B==0) Q=0; D、endmodule 4、【单选题】module andd(A,B,Q); output Q; input A,B; reg Q; always @(A,B ) if (A==0) begin if(B==0) Q=0; end else Q=1;endmodule其中,else Q=1;与哪句语句对应: A、always @(A,B ) B、if (A==0) C、if (B==0) Q=0; D、endmodule 5、【判断题】对于阻塞式赋值,执行过程分为(1)计算出“驱动表达式”的值;(2)向目标变量进行赋值操作;(3)完成赋值,这三个步骤不是一步完成的。 A、正确 B、错误 6、【判断题】Y1 = A^D;Y2 = #6 A E | C;这两句语句的执行过程是,在第一条语句“Y1 = A^D;”被执行后,要延时6个时间单位才能执行第二条语句。 A、正确 B、错误 7、【判断题】不完整的条件语句的描述,是Verilog描述时序电路的途径之一。 A、正确 B、错误 8、【判断题】Verilog默认,else与最近的没有else的if相关联。 A、正确 B、错误 9、【判断题】module triBUS4( IN3,IN2,IN1,IN0,ENA,DOUT); input[3:0] IN3,IN2,IN1,IN0 ; input[1:0] ENA; output[3:0] DOUT; reg[3:0]DOUT; always @(ENA, IN0) if (ENA==2’b00) DOUT=IN0; else DOUT=4’hz; always @(ENA, IN1) if (ENA==2’b01) DOUT=IN1; else DOUT=4’hz; always @(ENA, IN2) if (ENA==2’b10) DOUT=IN2; else DOUT=4’hz; always @(ENA, IN3) if (ENA==2’b11) DOUT=IN3; else DOUT=4’hz;endmodule该模块实现的是双向端口电路: A、正确 B、错误 10、【判断题】高阻态Z可以在电路模块中被信号所传递。 A、正确 B、错误 11、【判断题】双向端口在完成输入功能时,可以不使原来呈输出模式的端口呈高阻态。 A、正确 B、错误 12、【填空题】module BI4B(CTRL,DIN,Q,DOUT); input CTRL; input[3:0] DIN; ____ [3:0] Q; output[3:0] DOUT; reg [3:0] DOUT,Q ; always @(Q,DIN,CTRL) if (!____) begin DOUT=Q; Q=4’HZ; end elsebegin ____=DIN; DOUT=____; endendmodule空格处应该填入:A. CTRLB. 4’HZC. QD. inout(答案以空格区分, 如 A B C D) A、 作业-实验2报告 单元测验-实验2 1、【单选题】将256个正弦信号数据写入rom模块后,应设计一个几位的二进制计数器,来实现存储器的寻址? A、7 B、8 C、9 D、256 广东理工学院成人高考招生简章 广州城建职业学院成人高等教育招生简章 广东科学技术职业学院招生简章 广东科学技术职业学院招生简章 广东生态工程职业学院成人高考招生专业 清远职业技术学院成人高等教育招生专业简介 电子科技大学中山学院成人高等教育招生简章 广州涉外经济职业技术学院 韶关学院成人高考招生简章 广东财经大学成人高等教育招生简介 广东理工学院成人高考招生简章 广东第二师范学院成人高考招生简章 广东南方职业学院成人高考招生简章 广东亚视演艺职业学院成人高考招生简章

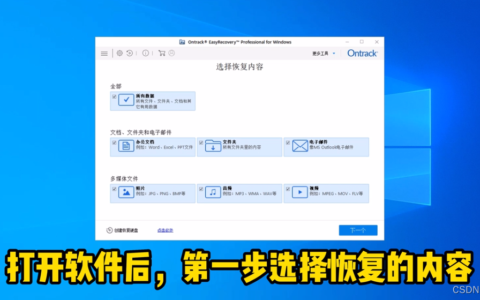

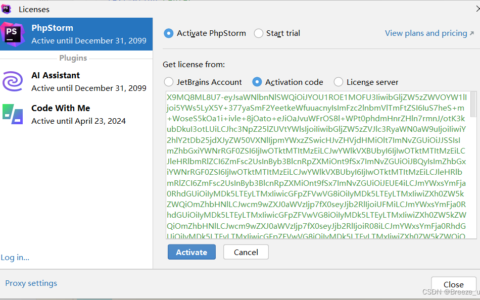

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/90712.html