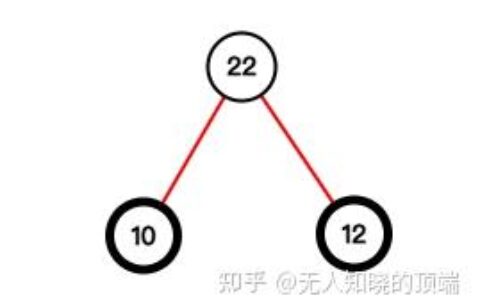

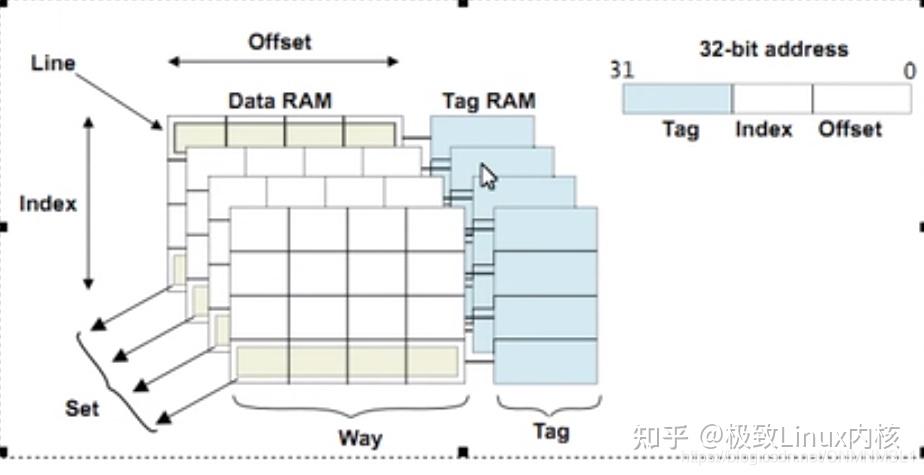

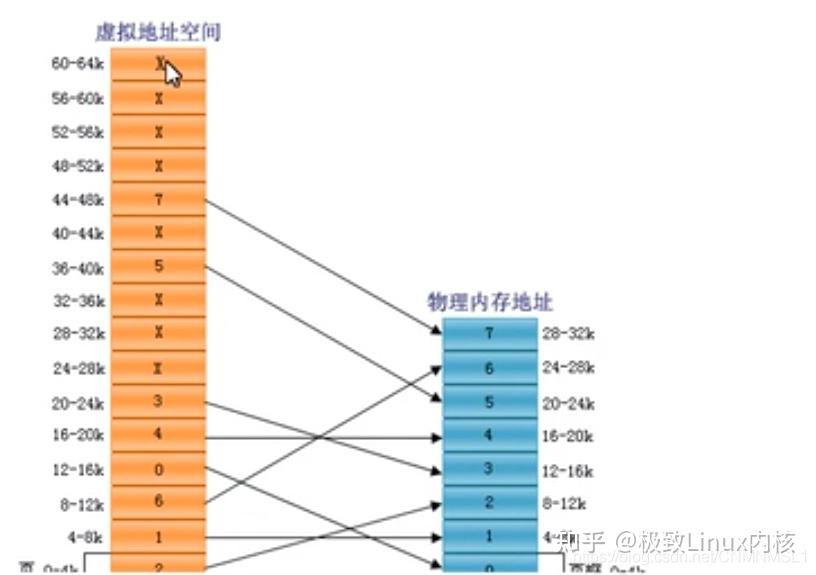

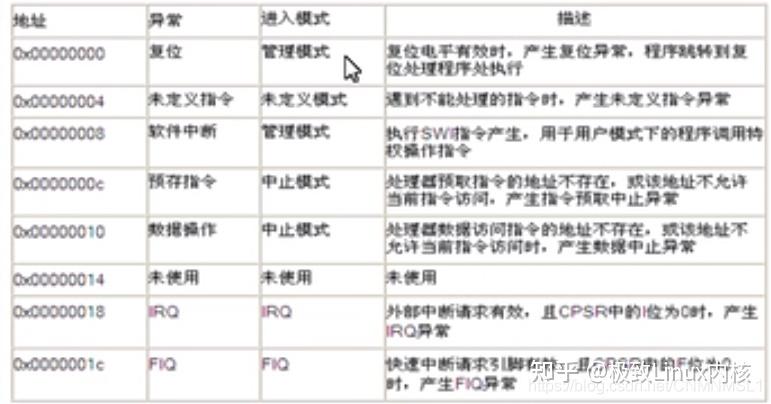

详细概括Linux内核中ARM硬件原理(图例解析) cpu核心 NEON/SIMD(单指令多数据流) 一个指令取出多个数据给CPU(原来是一个指令取出一个数据交给CPU在用下个指令去取) NEON技术可加速多媒体和信号处理算法(如视频编码/解码,2D/3D图形等多媒体)性能会提升很多倍 cache(缓存机制) 系统外围 RTC实时时钟(real time clock) PLL锁相回路或锁相环。用来统一正合时脉讯号,使内存能正确地存取信号。(一般不去控制它) PWM 脉冲宽度调制,做蜂鸣器或者稳压等 watchdog Timer 看门狗,由于电磁脉冲干扰,程序达不到预期成果,导致程序死锁等。一旦接收不到程序来的信号就会把程序reset,重新执行 DMA(direct memory access ) 直接内存访问。内存和外部设备进行数据迁移的时候不需要去访问CPU keypad 按钮 ADC模数转换器 连接 USB/OTG UART 通用异步收发接口。是一种通用串行数据总线,用于异步通信(并行入,串行出) I2C基层电路总线(串行) SPI 串行外围接口 用在EEPROM FLASH 实时时钟,AD转换器,数字信号处理器和数字信号解码器之间 Modem IF 通讯的调制解调器 GPIO 通用输入输出引脚 Audio IF 音频 storage IF 存储器的interface 多媒体 camera IF /MIPI CSI coder/decoder 2D/3D graphic engine TV out/HDMI JPEG CODEC LCD更多Linux内核源码高阶知识请加开发交流Q群篇【】,进群免费相关资料,免费观看公开课技术分享,入群不亏,快来加入我们吧~前100名进群领取,额外赠送一份价值699的内核资料包(含视频教程、电子书、实战项目及代码)

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/89219.html