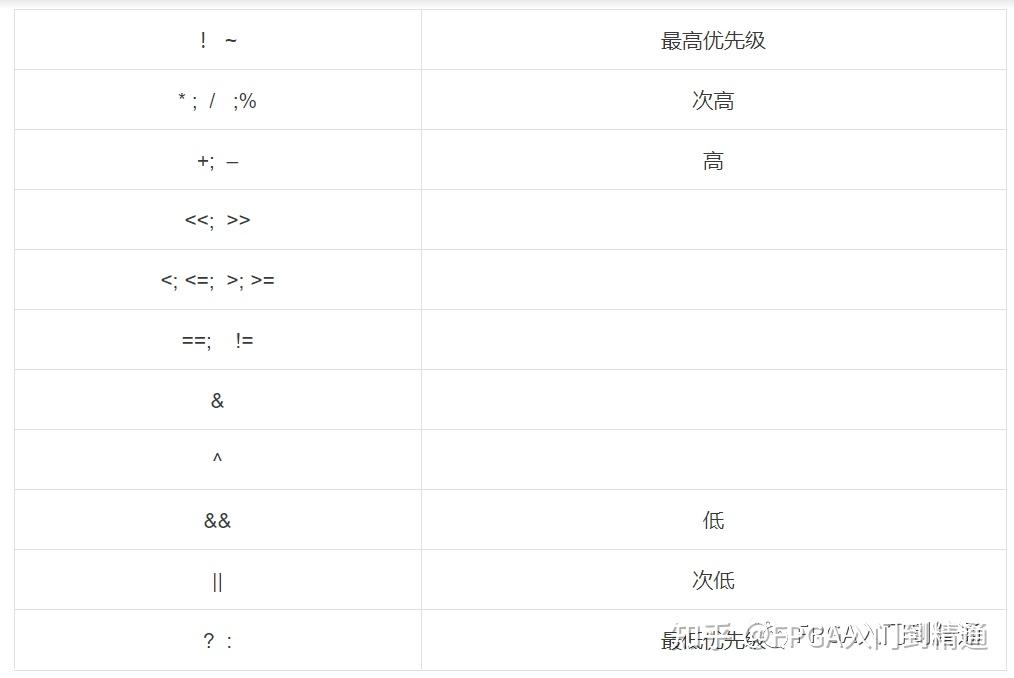

Verilog常用运算符及表达式 本文详细介绍了Verilog常用的运算符和表达式,特别是分享了处理“计算位宽溢出”和“负数”的可行方式,帮助读者更加轻松地理解和掌握Verilog语言的运算符。 一、常见运算符以及表达式 算数运算符:加(+)、减(-)、乘(*)、除(/)、取余(%)赋值运算符:阻塞赋值(=)、非阻塞赋值(<=);关系运算符:大于(>)、小于(<)、等于(==)、不等于(!=)、大于等于(>=)、小于等于(<=)逻辑运算符:与(&&)、或(||)、非(!);条件运算符:(?:);位运算符 : 取反(~)、或(|)、异或(^)、与(&);移位运算符:左移(<<)、右移(>>);拼接运算符:位拼接({}),复制{n{b}}; 二、详细介绍 1、算数运算符 加(+)、减(-)、乘(*)、除(/)、取余(%) 2、赋值运算符 阻塞赋值(=)常用于组合逻辑,例如assign语句和always@(*)语句块。 非阻塞赋值(<=)常用于时序逻辑,例如always@(posedge clk)语句块。 3、关系运算符 大于(>)、小于(<)、等于(==) 不等于(!=)、大于等于(>=)、小于等于(<=) 4、逻辑运算符 (1)与(&&) 逻辑与:a&&b,a和b同时为真时才为真,否则为假 (2)或(||) 逻辑或:a||b,a和b同时为假时才为假,否则为真 (3)非(!) a为真时,!a为假 5、条件运算符 条件表达式的值为真或假,如果为真,返回值1,否则返回值2。它主要用于简化if-else语句的书写和提高代码的可读性。 assign a = (b) ? ‘b1 : ‘b0; 如果b为真,那么a = ‘b1,否则a = ‘b0。 6、位运算符 (1)与(&) 对两个数的二进制形式进行“与”运算,只有两个相应位的值都为1时,结果才为1。 (2)或(|) 对两个数的二进制形式进行“或”运算,只要有一个相应位的值为1,结果就为1。 (3)异或(^) 对两个数的二进制形式进行“异或”运算,当两个相应位的值不同时,结果为1,否则为0。 (4)取反(~) 对一个数的二进制形式进行取反操作,即0变为1,1变为0。 7、移位运算符 在Verilog中有两种移位运算符:<< (左移位运算符) 和 >>(右移位运算符)。其使用方法如下:a>>n或a<<n,a是操作数,n表示移动几位,这两种移位运算都用0填补移出的空位。 8、拼接运算符 位拼接运算符可以把两个或多个信号的某些位拼接起来进行运算操作,或者把单个信号复制多份。其使用方法如下: 9、运算符优先级

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/89051.html