bissc协议详解_bissc协议详解如何解码基于FPGA的BISS-C协议编码器的解码实现1 概要本文以实际工程为背景,介绍了基于FPGA的BISS-C协议编码器的解码实现,并通过板级验证了解码的正确性。2 功能描述通过FPGA解析编码器发送的BISS-C数据帧格式

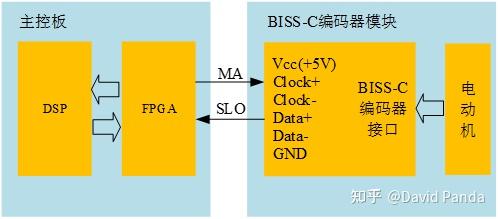

基于FPGA的BISS-C协议编码器的解码实现 1 概要 本文以实际工程为背景,介绍了基于FPGA的BISS-C协议编码器的解码实现,并通过板级验证了解码的正确性。 2 功能描述 通过FPGA解析编码器发送的BISS-C数据帧格式。具体实现:按下key_touch电容按键,解析一帧编码器的数据,解析完成后,led灯的状态发生翻转。 3 硬件资源 下面是采用 点对点通信方式的硬件连接电路(单端模式),包括两大部分,其一是主控板部分,其中的DSP部分并没有在本文中体现,其二是BISS-C编码器模块,其中的电动机部分没有再本文中体现。

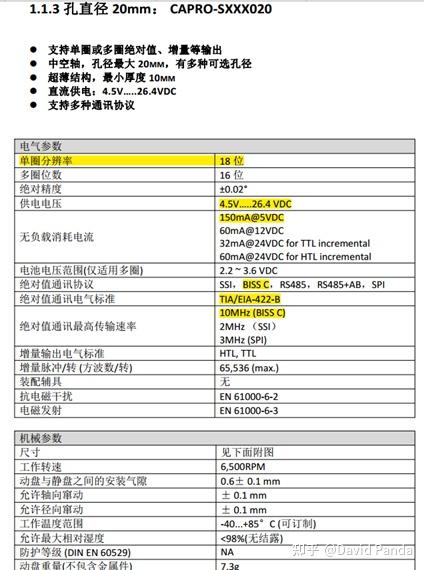

图1 点对点通信方式的硬件连接电路(单端模式) 3.1 FPGA FPGA芯片:EP4CE10F17C8(野火征途pro开发板) 3.2 编码器 编码器:biss_c协议编码器,单圈18位,报警位2位。单端工作模式。资料见参考资料。

图1 点对点通信方式的硬件连接电路(单端模式) 3.1 FPGA FPGA芯片:EP4CE10F17C8(野火征途pro开发板) 3.2 编码器 编码器:biss_c协议编码器,单圈18位,报警位2位。单端工作模式。资料见参考资料。

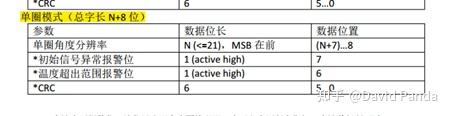

4 程序设计 4.1 整体说明

4 程序设计 4.1 整体说明

图2 BISS-C帧解析整体框图

图2 BISS-C帧解析整体框图

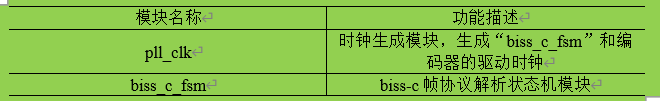

表1 BISS-C帧解析模块简介 代码实现: 4.2 pll_clk模块

表1 BISS-C帧解析模块简介 代码实现: 4.2 pll_clk模块

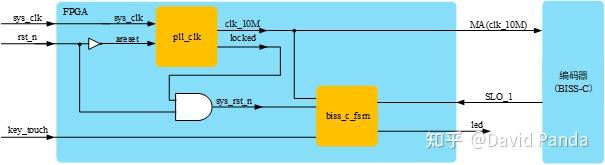

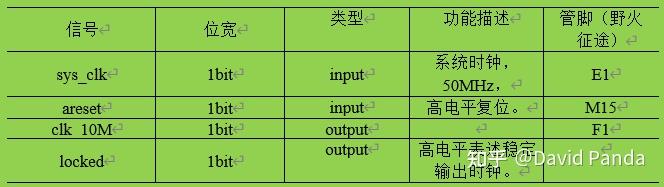

图3 pll_clk模块框图 pll_clk模块为“biss_c_fsm”模块提供10MHz的工作时钟,同时也是编码器帧解析的工作时钟。输出的时钟稳定信号locked和rst_n相与后,的sys_rst_n作为“biss_c_fsm”模块的复位信号。pll_clk的输入模块是系统时钟(50MHz),复位rst_n。

图3 pll_clk模块框图 pll_clk模块为“biss_c_fsm”模块提供10MHz的工作时钟,同时也是编码器帧解析的工作时钟。输出的时钟稳定信号locked和rst_n相与后,的sys_rst_n作为“biss_c_fsm”模块的复位信号。pll_clk的输入模块是系统时钟(50MHz),复位rst_n。

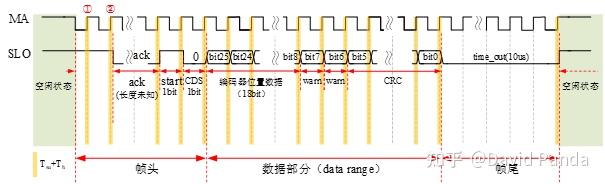

表2 pll_clk模块输入输出信号描述 4.3 biss_c_fsm模块 biss_c_fsm模块完成具体的解析编码器发出的符合BISS-C协议的数据帧。 4.3.1 模块框图

表2 pll_clk模块输入输出信号描述 4.3 biss_c_fsm模块 biss_c_fsm模块完成具体的解析编码器发出的符合BISS-C协议的数据帧。 4.3.1 模块框图

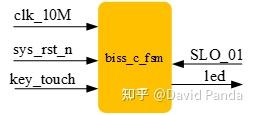

图4 biss_c_fsm模块框图

图4 biss_c_fsm模块框图

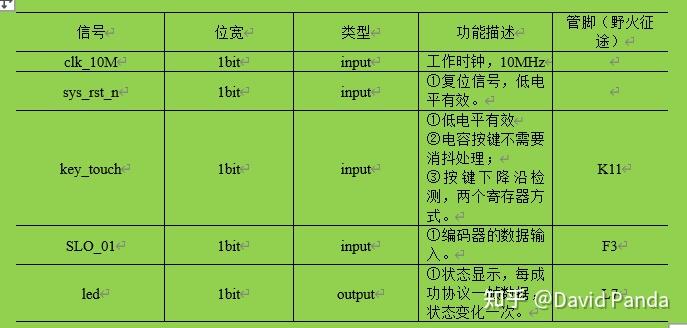

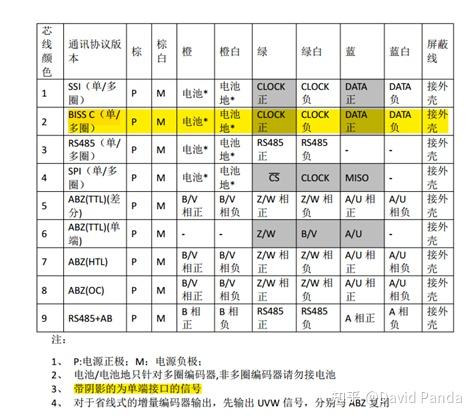

表3 biss_c_fsm模块输入输出信号描述 4.3.2 BISS-C协议时序 点对点模式中,BISS-C通信帧时序如下图所示。当空闲时,主接口MA时钟线发送高电平,SLO信号线反馈保持高电平,表明从机准备进行数据通信。通信开始时,主接口发送时钟信号向从接口申请数据通信。时钟信号MA第一个上升沿同步从接口,第二个上升沿,编码器将SLO信号线拉低(通过示波器测试,BISS-C协议编码器在时钟的下降沿附件变数,变数后维持一个周期。因此对于fpga而言,可以在上升沿处采集数据;为便于绘制波形图,采用极端情况,即认为编码器在时钟上升沿的时间窗口后变数,这是符合实际的。编码器将SLO信号线拉低发生在第二个上升沿时间窗口后)生成所谓的“ack”表示对MA信号的响应,“ack”维持低电平的时间是未知的,在“ack”期间,MA持续输出脉冲。实际上,由于通信线延迟(line delay),MA时钟信号和SLO信号会产生一定的延迟,所以BISS-C协议规定每个数据交换周期开始后都要检测线延迟。ack保持低电平直到检测完成,SLO发送表示start位的1bit高电平,随后发送1bit的CDS(control data slave)标志位。之后的若干位是数据位,以所使用的编码器为例,数据位共计26位,包括18位的“编码器采集的位置信息”,2位报警位(初始信号异常、温度超出范围),6位的CRC校验位。其中CRC(6bit)多项式为x6+x1+1,即校验码为“”。CRC会取反且先发送MSB(most significance bit),CRC校验数据范围为18位的“编码器采集的位置信息”和2位报警位(初始信号异常、温度超出范围)。其中报警位高电平有效。数据部分发送完成后,MA置高,SLO信号线拉低进入“time out”(超时)阶段。超时时间,以所使用的的编码器为例,当MA为10MHz时钟时,time out约为43us;当MA为5MHz时钟时,time out约为47us。“time out”(超时)阶段结束后,SLO信号线置高,进入空闲阶段,等待响应下一帧数据。

表3 biss_c_fsm模块输入输出信号描述 4.3.2 BISS-C协议时序 点对点模式中,BISS-C通信帧时序如下图所示。当空闲时,主接口MA时钟线发送高电平,SLO信号线反馈保持高电平,表明从机准备进行数据通信。通信开始时,主接口发送时钟信号向从接口申请数据通信。时钟信号MA第一个上升沿同步从接口,第二个上升沿,编码器将SLO信号线拉低(通过示波器测试,BISS-C协议编码器在时钟的下降沿附件变数,变数后维持一个周期。因此对于fpga而言,可以在上升沿处采集数据;为便于绘制波形图,采用极端情况,即认为编码器在时钟上升沿的时间窗口后变数,这是符合实际的。编码器将SLO信号线拉低发生在第二个上升沿时间窗口后)生成所谓的“ack”表示对MA信号的响应,“ack”维持低电平的时间是未知的,在“ack”期间,MA持续输出脉冲。实际上,由于通信线延迟(line delay),MA时钟信号和SLO信号会产生一定的延迟,所以BISS-C协议规定每个数据交换周期开始后都要检测线延迟。ack保持低电平直到检测完成,SLO发送表示start位的1bit高电平,随后发送1bit的CDS(control data slave)标志位。之后的若干位是数据位,以所使用的编码器为例,数据位共计26位,包括18位的“编码器采集的位置信息”,2位报警位(初始信号异常、温度超出范围),6位的CRC校验位。其中CRC(6bit)多项式为x6+x1+1,即校验码为“”。CRC会取反且先发送MSB(most significance bit),CRC校验数据范围为18位的“编码器采集的位置信息”和2位报警位(初始信号异常、温度超出范围)。其中报警位高电平有效。数据部分发送完成后,MA置高,SLO信号线拉低进入“time out”(超时)阶段。超时时间,以所使用的的编码器为例,当MA为10MHz时钟时,time out约为43us;当MA为5MHz时钟时,time out约为47us。“time out”(超时)阶段结束后,SLO信号线置高,进入空闲阶段,等待响应下一帧数据。

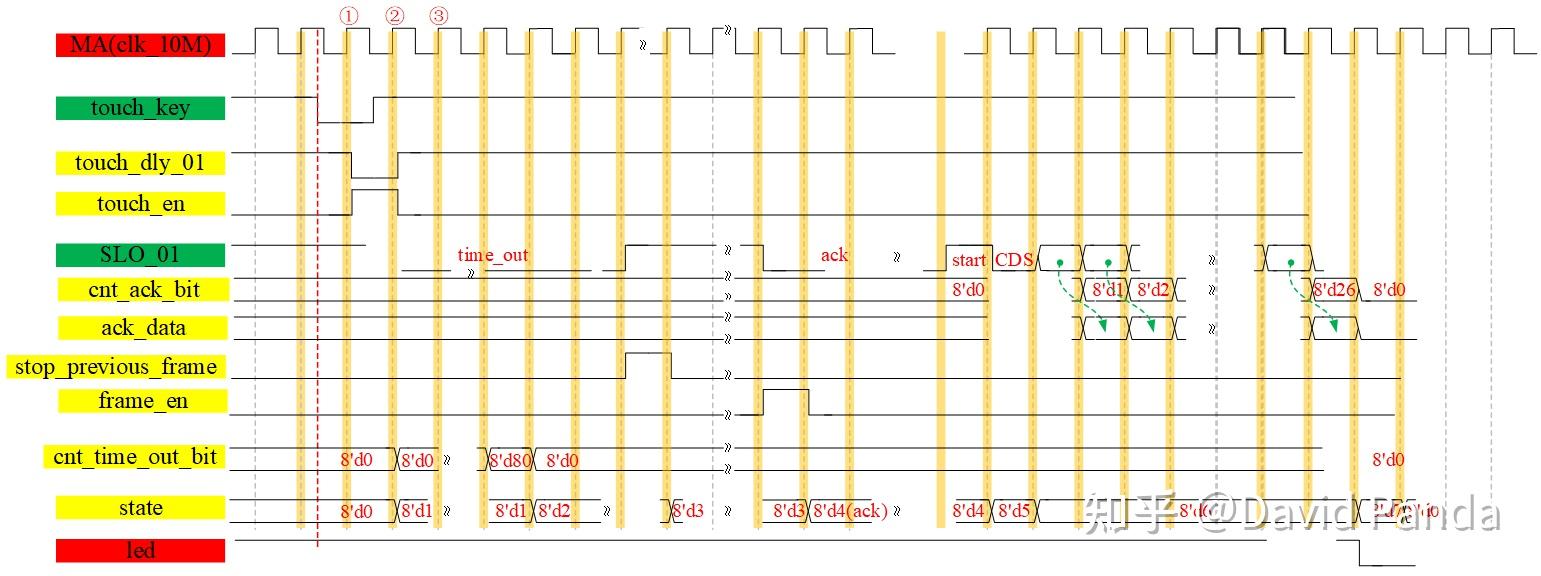

图5 BISS-C通信帧的时序 4.3.3 波形图绘制 下图是BISS-C帧解析的具体实现波形图。结合BISS-C协议时序采用状态机来实对biss-c数据帧的解析。

图5 BISS-C通信帧的时序 4.3.3 波形图绘制 下图是BISS-C帧解析的具体实现波形图。结合BISS-C协议时序采用状态机来实对biss-c数据帧的解析。

图6 BISS-C帧解析的整体波形图 下面结合波形图对具体实现的状态机进行描述。对于状态机的设计,其重点是设计状态转移图。下图是自己定义的状态转移图的规范标准。每个矩形的框表示一个状态,有转移关系的状态之间(包括自己指向自己)都有一个指向的箭头,表示状态跳转的过程,箭头上有标注的一组数字,“/”左边表示的是状态的输入,“/”右边表达的是状态的输出,各个状态之间的功能、状态转移的条件、输入/输出都能够在状态转移图中清晰的表达出来。

图6 BISS-C帧解析的整体波形图 下面结合波形图对具体实现的状态机进行描述。对于状态机的设计,其重点是设计状态转移图。下图是自己定义的状态转移图的规范标准。每个矩形的框表示一个状态,有转移关系的状态之间(包括自己指向自己)都有一个指向的箭头,表示状态跳转的过程,箭头上有标注的一组数字,“/”左边表示的是状态的输入,“/”右边表达的是状态的输出,各个状态之间的功能、状态转移的条件、输入/输出都能够在状态转移图中清晰的表达出来。

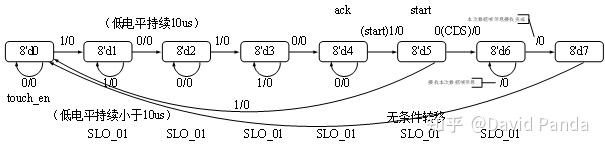

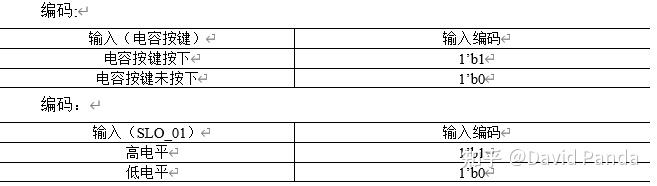

图7 biss_c_fsm的状态转移图 结出来就是一个完整的状态转移图需要包括以下三个要素: (1)输入:根据输入可以确定是否需要进行状态的转移、输出,是影响状态机系统执行过程的重要驱动力。 (2)输出:状态机系统最终要执行的动作,取决于当前时刻的状态和输入。 (3)状态:是状态机系统执行的一个稳定的过程,根据当前时刻的输入和状态确定下一时刻所处的状态(状态的转移)。 接下来套用上面的总结分析本例的状态转移图是如何绘制的。首先要将实际的问题抽象成需要的素,就是要找到状态转移图所需要的输入、输出、状态分别对应实际问题的哪些部分,分析结果如下: 输入:电容按键按下/电容按键没有按下;SLO_01输入为高电平/ SLO_01输入为低电平。

图7 biss_c_fsm的状态转移图 结出来就是一个完整的状态转移图需要包括以下三个要素: (1)输入:根据输入可以确定是否需要进行状态的转移、输出,是影响状态机系统执行过程的重要驱动力。 (2)输出:状态机系统最终要执行的动作,取决于当前时刻的状态和输入。 (3)状态:是状态机系统执行的一个稳定的过程,根据当前时刻的输入和状态确定下一时刻所处的状态(状态的转移)。 接下来套用上面的总结分析本例的状态转移图是如何绘制的。首先要将实际的问题抽象成需要的素,就是要找到状态转移图所需要的输入、输出、状态分别对应实际问题的哪些部分,分析结果如下: 输入:电容按键按下/电容按键没有按下;SLO_01输入为高电平/ SLO_01输入为低电平。

输出:led的状态翻转/led灯的状态没有翻转

输出:led的状态翻转/led灯的状态没有翻转

状态: 结合BISS-C协议的帧时序及输入,可以将整个帧解析过程分为以下8个状态如下表所示。

状态: 结合BISS-C协议的帧时序及输入,可以将整个帧解析过程分为以下8个状态如下表所示。

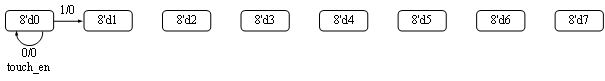

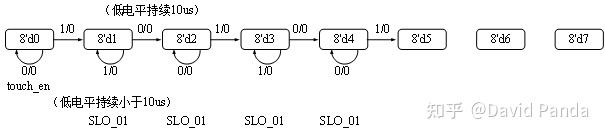

表4 BISS-C帧解析的状态及状态编码 根据这些抽象出来的要素可以绘制状态转移图。首先根据分析的状态数先画出8个状态,如下图所示,每个状态名都和状态相对应(状态编码)。

表4 BISS-C帧解析的状态及状态编码 根据这些抽象出来的要素可以绘制状态转移图。首先根据分析的状态数先画出8个状态,如下图所示,每个状态名都和状态相对应(状态编码)。

图8 biss_c_fsm的状态 从“8’d0”的状态开始分析。有两种情况,一种是电容按键未按下,维持原来状态“8’d0”;另一种情况是电容按键按下,在上升沿的时间窗口后跳转到状态“8’d1”。

图8 biss_c_fsm的状态 从“8’d0”的状态开始分析。有两种情况,一种是电容按键未按下,维持原来状态“8’d0”;另一种情况是电容按键按下,在上升沿的时间窗口后跳转到状态“8’d1”。

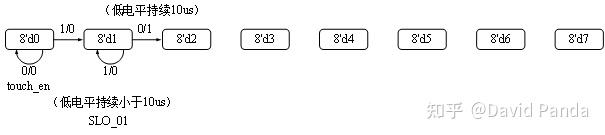

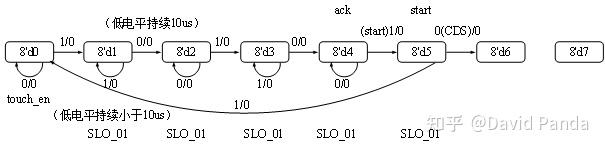

图9 “8’d0”的状态转移图 接着分析状态“8’d1”的状态跳转情况。有两种情况,一种是未知状态,即没有检测到上一数据帧(SLO_01)的结束标志之10us的连续低电平,维持原状态8’d1;另一种情况是检测上一数据帧的结束标志之10us的连续低电平,结束未知状态,跳转到8’d2。

图9 “8’d0”的状态转移图 接着分析状态“8’d1”的状态跳转情况。有两种情况,一种是未知状态,即没有检测到上一数据帧(SLO_01)的结束标志之10us的连续低电平,维持原状态8’d1;另一种情况是检测上一数据帧的结束标志之10us的连续低电平,结束未知状态,跳转到8’d2。

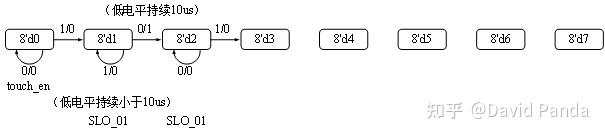

图10 “8’d1”的状态转移图 接着分析状态“8’d2”的状态跳转情况。有两种情况,一种是time_out状态,即SLO_01仍然为低电平的状态,维持状态“8’d2”;另一种是SLO_01变为1,即在“8’d2”的状态下,输入SLO_01为高电平,此时(上升沿的时间窗口之后)状态跳转到“8’d3”。

图10 “8’d1”的状态转移图 接着分析状态“8’d2”的状态跳转情况。有两种情况,一种是time_out状态,即SLO_01仍然为低电平的状态,维持状态“8’d2”;另一种是SLO_01变为1,即在“8’d2”的状态下,输入SLO_01为高电平,此时(上升沿的时间窗口之后)状态跳转到“8’d3”。

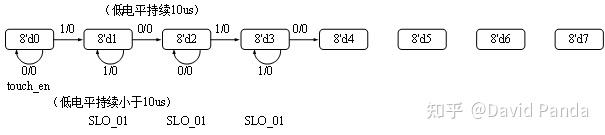

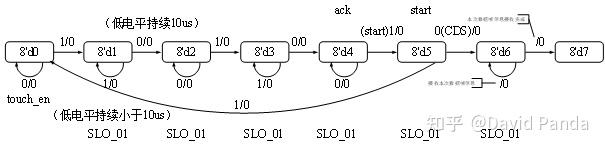

图11 “8’d2”的状态转移图 接着分析状态“8’d3”(空闲状态)的状态跳转情况。有两种情况,一种是SLO维持高电平,即状态“8’d3”(空闲状态)。另一种情况是输入SLO_01拉低电平,即在 “8’d3” 状态下,输入SLO_01为低电平,此时状态跳转到“8’d4”。

图11 “8’d2”的状态转移图 接着分析状态“8’d3”(空闲状态)的状态跳转情况。有两种情况,一种是SLO维持高电平,即状态“8’d3”(空闲状态)。另一种情况是输入SLO_01拉低电平,即在 “8’d3” 状态下,输入SLO_01为低电平,此时状态跳转到“8’d4”。

图12 “8’d3”的状态转移图 接着分析状态“8’d4”(ack状态)的状态跳转情况。有两种情况,一种是SLO继续维持低电平,即维持原“8’d4”状态(ack状态);另一种情况是SLO变为高电平,即在“8’d4”的状态下,输入SLO为高电平,此时状态跳转到“8’d5”。

图12 “8’d3”的状态转移图 接着分析状态“8’d4”(ack状态)的状态跳转情况。有两种情况,一种是SLO继续维持低电平,即维持原“8’d4”状态(ack状态);另一种情况是SLO变为高电平,即在“8’d4”的状态下,输入SLO为高电平,此时状态跳转到“8’d5”。

图13 状态“8’d4”的状态跳转图 接着分析状态“8’d5”的状态跳转情况。有两种情况,一种是SLO继续维持高电平,这与帧协议的1bit的start(1’b1)相矛盾,表示帧解析失败,回到初始状态“8’d0”;另一种情况是SLO变为低电平,即在状态“8’d5”下,输入SLO为低电平,此时状态跳转到“8’d6”。

图13 状态“8’d4”的状态跳转图 接着分析状态“8’d5”的状态跳转情况。有两种情况,一种是SLO继续维持高电平,这与帧协议的1bit的start(1’b1)相矛盾,表示帧解析失败,回到初始状态“8’d0”;另一种情况是SLO变为低电平,即在状态“8’d5”下,输入SLO为低电平,此时状态跳转到“8’d6”。

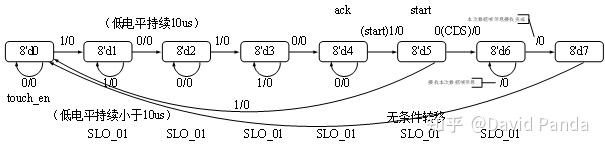

图14 状态“8’d5”的状态跳转图 接着分析状态“8’d6”(接收编码器的ack_data)的状态跳转情况。有两种情况,一种是接收编码器的ack_data,此时处于“8’d6”状态;另一种是已近接收完编码器的ack_data,跳转到状态“8’d7”。

图14 状态“8’d5”的状态跳转图 接着分析状态“8’d6”(接收编码器的ack_data)的状态跳转情况。有两种情况,一种是接收编码器的ack_data,此时处于“8’d6”状态;另一种是已近接收完编码器的ack_data,跳转到状态“8’d7”。

图15 状态“8’d6”的状态跳转图 接着分析状态“8’d7”的状态跳转情况。无条件跳转到“8’d0”状态,进行下一帧的解析。

图15 状态“8’d6”的状态跳转图 接着分析状态“8’d7”的状态跳转情况。无条件跳转到“8’d0”状态,进行下一帧的解析。

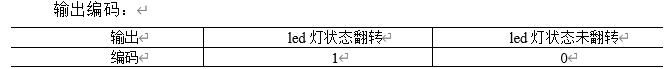

图16 状态“8’d7”的状态跳转图 4.3.4 代码编写 4.3.5 Signal Tap板级验证波形 使用Signal Tap对信号进行抓取,抓取的波形如下图所示。将波形与所绘制的波形图进行对比,各信号波形吻合。另外对解析的数据进行了实际的CRC校验,所得到的的CRC校验码和接收到的一致。证实了接收数据的帧解析数据的正确性。

图16 状态“8’d7”的状态跳转图 4.3.4 代码编写 4.3.5 Signal Tap板级验证波形 使用Signal Tap对信号进行抓取,抓取的波形如下图所示。将波形与所绘制的波形图进行对比,各信号波形吻合。另外对解析的数据进行了实际的CRC校验,所得到的的CRC校验码和接收到的一致。证实了接收数据的帧解析数据的正确性。

图17 biss_c_fsm模块信号抓取局部波形图(一)

图17 biss_c_fsm模块信号抓取局部波形图(一)

图18 biss_c_fsm模块信号抓取局部波形图(二) 参考资料: 资料下载-盈动高科-YINGDONG Co. Ltd.,编码器产品领导品牌,绝对值编码器龙头企业,光电编码器,运动控制,POSITAL,博斯特中国一级代理商,直线编码器,平面运动编码器,绝对值编码器 基于FPGA的BiSS-C…码器接口技术研究及解码实现_王希远_2016(清华) 基于BISS-C协议的绝对值编码器数据采集方法研究_周光泽_2020

图18 biss_c_fsm模块信号抓取局部波形图(二) 参考资料: 资料下载-盈动高科-YINGDONG Co. Ltd.,编码器产品领导品牌,绝对值编码器龙头企业,光电编码器,运动控制,POSITAL,博斯特中国一级代理商,直线编码器,平面运动编码器,绝对值编码器 基于FPGA的BiSS-C…码器接口技术研究及解码实现_王希远_2016(清华) 基于BISS-C协议的绝对值编码器数据采集方法研究_周光泽_2020

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。

文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/88971.html