计算机组成原理期末考点总结 第一部分 数据的编码表示 考点一:原码、补码的表示,表示范围 1.1原码、反码、补码的表示 原码就是真值加符号位。 原码变反码:正数不变;负数的符号位不变,其他位取反。 原码变补码:正数不变;负数的符号位不变,其他位取反再加一。或者从右往左第一个1以及右边的0不变,其左边的各位取反,符号位不变。 1.2原码、反码、补码的特殊情况 原码的0有两种,[+0]原=00000,[-0]原=10000(以5位为例) 反码的0也有两种,[+0]反=00000,[-0]反=11111(以5位为例) 补码的0只有一种,[+0]补=[-0]补=00000,其中10000用来表示最负数

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图5 [0,2^{n}-1]](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图11 [-(2^{n-1}-1),2^{n-1}-1]](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图13 [-(1-2^{-(n-1)}),1-2^{-(n-1)}]](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图15 [-2^{n-1},2^{n-1}-1]](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图17 [-1,1-2^{-(n-1)}]](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图59 [X+Y]_补=[X]_补+[Y]_补](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图61 [X-Y]_补=[X]_补+[[Y]_补]_{变补}=[X]_补+[-Y]_补](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图63 [Y]_补](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

![标志寄存器及其标志位的意义_flags寄存器的九个标志位插图65 [-Y]_补](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

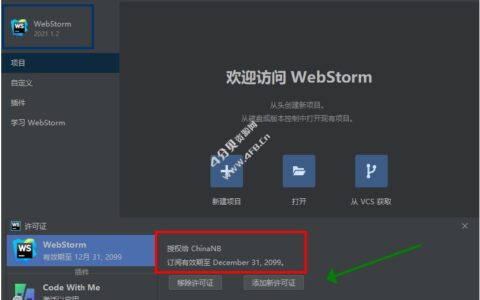

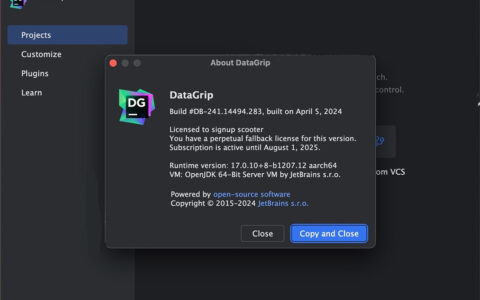

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/84770.html