8 序列检测_移位寄存器——Verilog HDL练习 设计目标:使用移位寄存器的方式,来检测序列“10010”。 设计思路: 这次用移位寄存器实现序列检测,超简单。 本质就是串并转换,然后将并行输出和检测序列做一个与运算。 描述语言:Verilog HDL 开发工具:Vivado 2019.2 工程链接:https://github.com/RongyeL/Verilog-HDL-Library/tree/main/8%20seqdet_shift 关键代码: `timescale 1ns / 1ps //================================================================================================== // Filename : seqdet_shift.v // Created On : 2021-04-19 // Version : V 1.0 // Author : Rongye // Description : Use shift register for sequence detection // Modification : // //================================================================================================== module SEQDET_SHIFT( // INPUTS Clk, // posedge active rst_n, // negedge active x, // sequence input // OUTPUTS y // detection “10010” ); input Clk; input rst_n; input x; output y; reg y; reg [4:0] shift_r; // shift register design always @(posedge Clk or negedge rst_n)begin if(!rst_n) shift_r <= 5’d0; else shift_r <= {shift_r[3:0], x}; end // detection output always@(posedge Clk or negedge rst_n)begin if(!rst_n) y <= 1’b0; else if(shift_r == 5’b10010) y <= 1’b1; else y <= 1’b0; end endmodule 仿真结果: 输入序列是“1100_1101_0001_0010_0100” 跟上一期状态机的结果是一样的。 这里放大一下更容易看移位寄存器的输出。 从代码上看就会发现,简单了很多, 只要寄存器的输出5个位为“10010”, 就可以说检测到了,很容易理解。 详情可见testbench文件。

输入序列是“1100_1101_0001_0010_0100” 跟上一期状态机的结果是一样的。 这里放大一下更容易看移位寄存器的输出。 从代码上看就会发现,简单了很多, 只要寄存器的输出5个位为“10010”, 就可以说检测到了,很容易理解。 详情可见testbench文件。

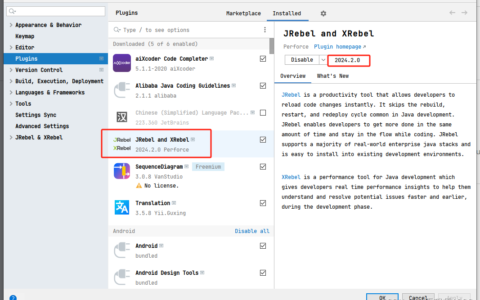

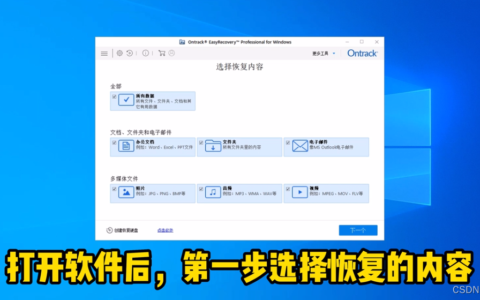

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/81728.html