嵌入式基础知识-存储器 本篇介绍计算机存储硬件的一些基础知识,在嵌入式开发中,也同样适用。 1 计算机存储结构 存储器是计算机中的重要部件,理想的存储器应该是执行快,容量足,价格便宜等。但实际上,目前无法同时满足这些目标,因此计算机通常采用分级存储的方式。

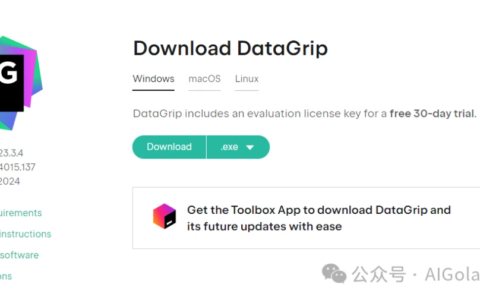

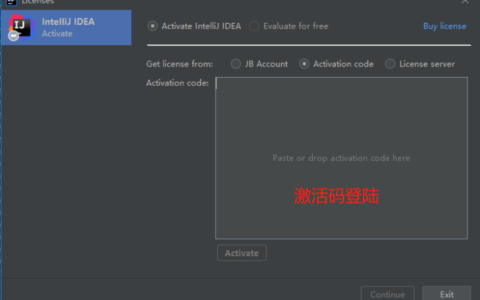

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/80453.html