dds协议原理详解_c++代码示例FPGA——DDS原理及代码实现一、DDS各参数意义* 如图,一个量化的32点的正弦波,也就是说一个ROM里存了32个这样的数据,每次读出一个数据要1ms,分别读出1,2,3…30,31,32,共32个点,读取完整的正弦波需要1ms * 32 = 32ms的时间 该正弦波参数为

FPGA——DDS原理及代码实现 一、DDS各参数意义

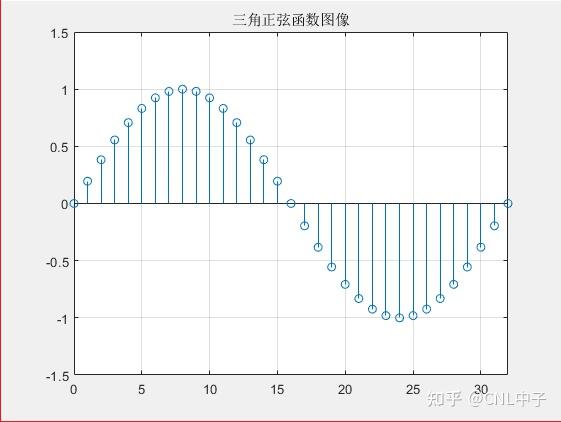

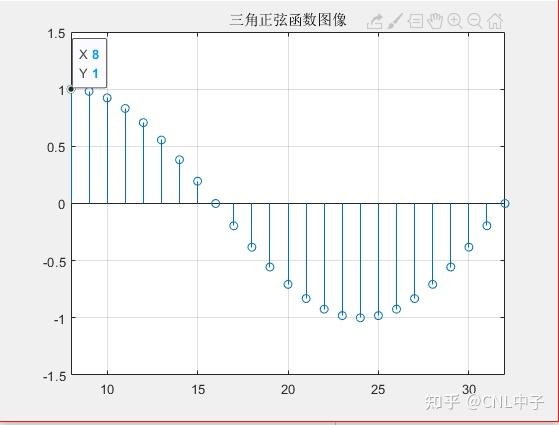

* 如图,一个量化的32点的正弦波,也就是说一个ROM里存了32个这样的数据,每次读出一个数据要1ms,分别读出1,2,3…30,31,32,共32个点,读取完整的正弦波需要1ms * 32 = 32ms的时间 该正弦波参数为 > 周期T = 1ms * 32 = 32ms, > 频率为 f = 1/T = 1/(1ms * (32/1))

* 如图,一个量化的32点的正弦波,也就是说一个ROM里存了32个这样的数据,每次读出一个数据要1ms,分别读出1,2,3…30,31,32,共32个点,读取完整的正弦波需要1ms * 32 = 32ms的时间 该正弦波参数为 > 周期T = 1ms * 32 = 32ms, > 频率为 f = 1/T = 1/(1ms * (32/1))

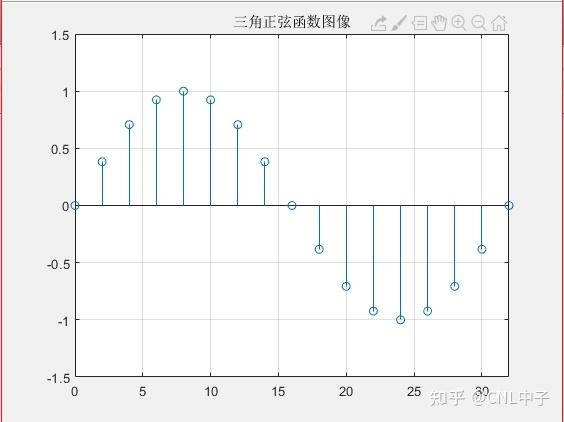

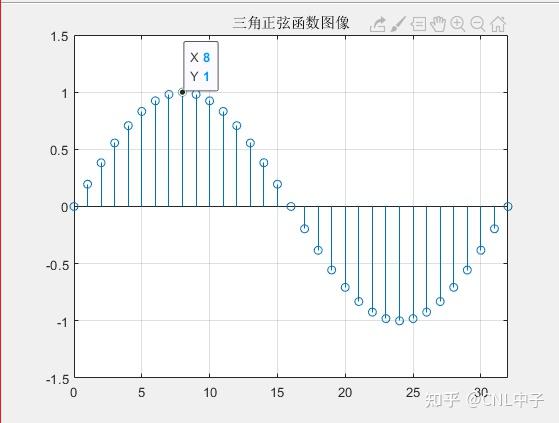

在读出一个数据时间不变(1ms)的情况下,想要让读出的正弦波频率增加一倍,那就要间隔读取,分别读出2,4,6,8,10…28,30,32,此时只需要读16个点 那么读出完整正弦波的参数为 > 周期T = 1ms * 16 = 16ms > 频率f = 1/T = 1/(1ms * 16) = 1/(1ms * (32/2))

在读出一个数据时间不变(1ms)的情况下,想要让读出的正弦波频率增加一倍,那就要间隔读取,分别读出2,4,6,8,10…28,30,32,此时只需要读16个点 那么读出完整正弦波的参数为 > 周期T = 1ms * 16 = 16ms > 频率f = 1/T = 1/(1ms * 16) = 1/(1ms * (32/2))

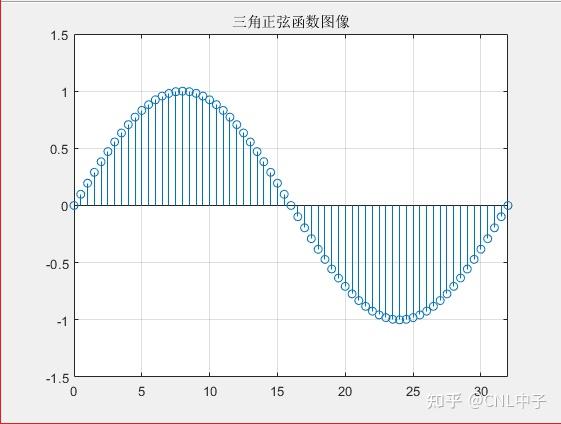

想要读出的正弦波频率减少一倍,那就要插值读取,分别读出0.5,1,1.5,2,2.5,3…30.5,31,31.5,32,此时要读64个点 读出正弦波的参数为 > 周期T = 1ms * 64 = 64ms > 频率f = 1/T = 1/(1ms * 64) = 1/(1ms * (32/0.5))

想要读出的正弦波频率减少一倍,那就要插值读取,分别读出0.5,1,1.5,2,2.5,3…30.5,31,31.5,32,此时要读64个点 读出正弦波的参数为 > 周期T = 1ms * 64 = 64ms > 频率f = 1/T = 1/(1ms * 64) = 1/(1ms * (32/0.5))

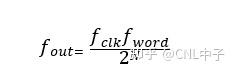

这里,1ms即为Tclk,fclk = 1/Tclk = 1/1ms;32 = 2^5即为N=5,而32除以的数(1,2,0.5)即为频率控制字fword,那么fo = (fclk * fword)/(2^N)

这里,1ms即为Tclk,fclk = 1/Tclk = 1/1ms;32 = 2^5即为N=5,而32除以的数(1,2,0.5)即为频率控制字fword,那么fo = (fclk * fword)/(2^N)

通常,FPGA并不擅长浮点运算,第三种情况,上式的(32/0.5)是很难实现的,因此在正弦波周期一样的情况下,将精度N调高一位,N=6,(2^5 * 2)/(0.5 * 2),此时fword就不用为0.5,而是1相位控制字pword的参数解释,如果从x轴为8的数据开始取,那么相当于正弦波相移了90°,pword = 8,这就是相位控制字

通常,FPGA并不擅长浮点运算,第三种情况,上式的(32/0.5)是很难实现的,因此在正弦波周期一样的情况下,将精度N调高一位,N=6,(2^5 * 2)/(0.5 * 2),此时fword就不用为0.5,而是1相位控制字pword的参数解释,如果从x轴为8的数据开始取,那么相当于正弦波相移了90°,pword = 8,这就是相位控制字

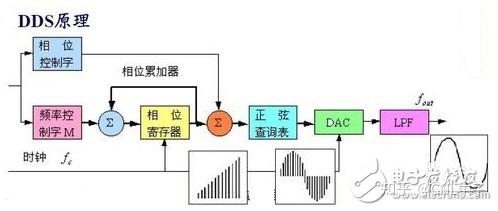

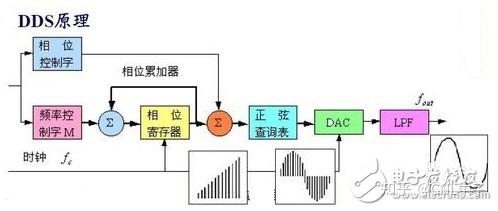

二、DDS的verilog代码实现 如何写代码?照着DDS结构图书写即可对于相位调制器代码的解释 为什么地址是由相位控制字加频率控制字高12位得到的? 1、本次实验使用的rom是宽度为14,深度为2^12 = 4096的数据,所以相位控制字根据rom的深度选择了12位宽 2、为什么ROM宽度是14,深度不取2^14?FPGA资源不够,没有这么多的寄存器存取这么多的数据 3、地址 = 相位 + 频率更迭,而相位宽度为12位,频率的宽度比相位多,所以频率控制字取高几位是由相位控制字的宽度决定的 4、取频率控制字高12位是如何完成频率变换的? 举例: 2^1 = 2’b10 2^2 = 3’b100 2^3 = 4’b1000 …… 2^19 = 20’b1000_0000_0000_0000_0000 2^20 = 21’b1_0000_0000_0000_0000_0000 2^21 = 22’b10_0000_0000_0000_0000_0000 f = 1/T,N = 32 频率控制字为:2^20 fword_acc[31:0] + 2^20 相当于 (fword_acc[31:20] + 1)此时就是按照地址+1的速度寻址,假如Fclk = 50MHz(系统时钟),Tclk = 20ns,输出波形的周期就为:To = 20ns * 4096 频率控制字为:2^19 fword_acc[31:0] + (2^19 + 2^19) 相当于 (fword_acc[31:20] + 1),也就是要加两次频率控制字,才能实现一次地址+1,Tclk = 20ns,输出完整波形就要输出2次*4096个数据,输出的波形周期为:To = 20ns * (2 * 4096) 频率控制字为:2^21 fword_acc[31:0] + (2^21) 相当于 (fword_add[31:20] + 2’b10),加一次频率控制字,实现一次地址+2,Tclk = 20ns,因为是跳过一位地址取的数据,所以数据量减半,输出完整波形只需要输出4096/2个数据,输出的波形周期为:To = 20ns * (4096/2)

二、DDS的verilog代码实现 如何写代码?照着DDS结构图书写即可对于相位调制器代码的解释 为什么地址是由相位控制字加频率控制字高12位得到的? 1、本次实验使用的rom是宽度为14,深度为2^12 = 4096的数据,所以相位控制字根据rom的深度选择了12位宽 2、为什么ROM宽度是14,深度不取2^14?FPGA资源不够,没有这么多的寄存器存取这么多的数据 3、地址 = 相位 + 频率更迭,而相位宽度为12位,频率的宽度比相位多,所以频率控制字取高几位是由相位控制字的宽度决定的 4、取频率控制字高12位是如何完成频率变换的? 举例: 2^1 = 2’b10 2^2 = 3’b100 2^3 = 4’b1000 …… 2^19 = 20’b1000_0000_0000_0000_0000 2^20 = 21’b1_0000_0000_0000_0000_0000 2^21 = 22’b10_0000_0000_0000_0000_0000 f = 1/T,N = 32 频率控制字为:2^20 fword_acc[31:0] + 2^20 相当于 (fword_acc[31:20] + 1)此时就是按照地址+1的速度寻址,假如Fclk = 50MHz(系统时钟),Tclk = 20ns,输出波形的周期就为:To = 20ns * 4096 频率控制字为:2^19 fword_acc[31:0] + (2^19 + 2^19) 相当于 (fword_acc[31:20] + 1),也就是要加两次频率控制字,才能实现一次地址+1,Tclk = 20ns,输出完整波形就要输出2次*4096个数据,输出的波形周期为:To = 20ns * (2 * 4096) 频率控制字为:2^21 fword_acc[31:0] + (2^21) 相当于 (fword_add[31:20] + 2’b10),加一次频率控制字,实现一次地址+2,Tclk = 20ns,因为是跳过一位地址取的数据,所以数据量减半,输出完整波形只需要输出4096/2个数据,输出的波形周期为:To = 20ns * (4096/2)

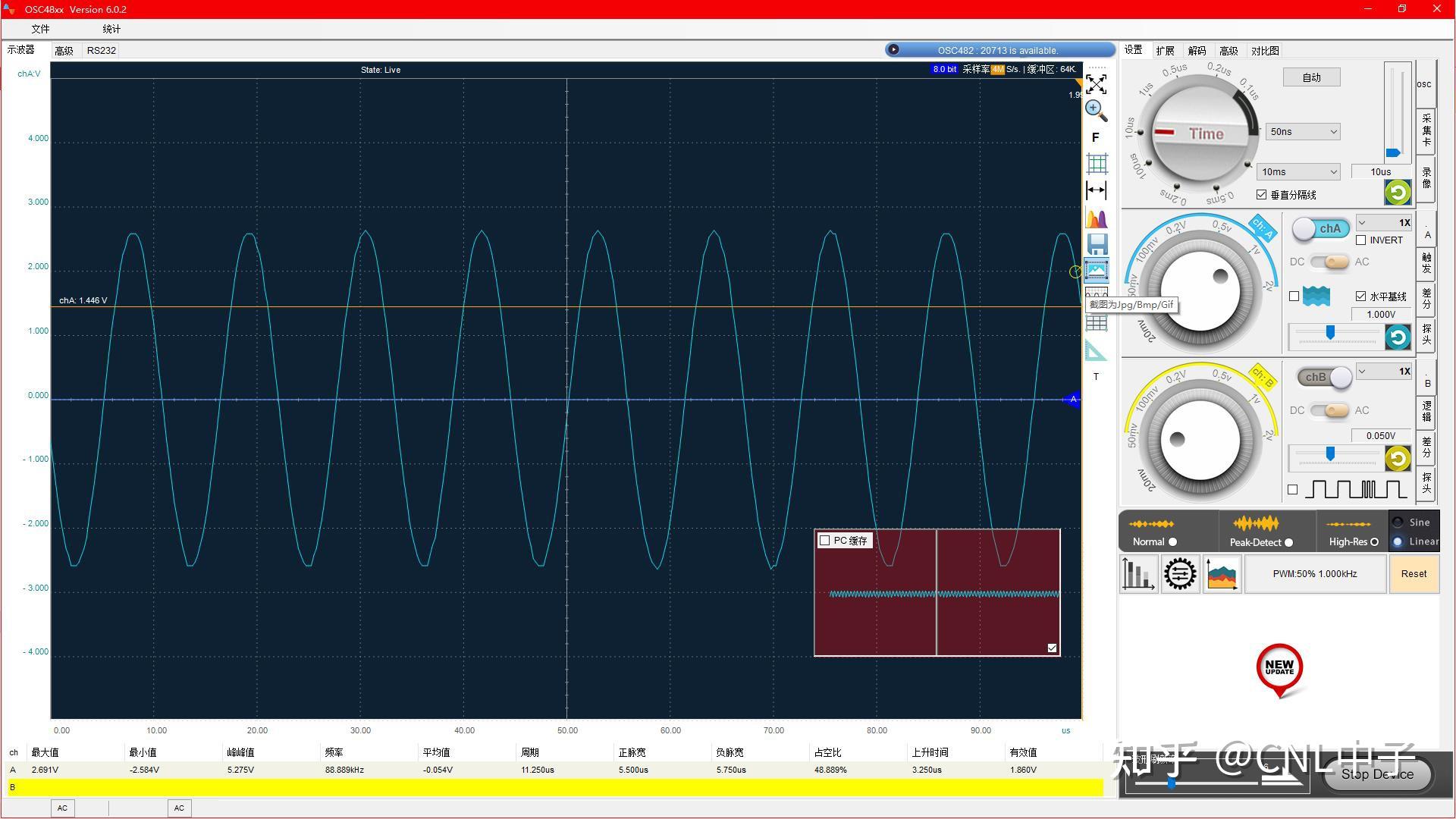

四、仿真文件 五、多种波形的实现 注: ( :- ) 12 ,向下取12位 data_out共有14位 取高12位,相当于左移两位,乘以4,每个输入的值放大4倍 四、matlab代码 五、部分效果

四、仿真文件 五、多种波形的实现 注: ( :- ) 12 ,向下取12位 data_out共有14位 取高12位,相当于左移两位,乘以4,每个输入的值放大4倍 四、matlab代码 五、部分效果

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。

文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/70246.html