arm内核的主要部件_arm体系结构支持哪些处理器模式ARM V8 SPEC A1.1 ARM V8 架构的简介第一节:ARM 架构基本概念第二节:ARM架构提供的数据类型第三节:高级SIMD和浮点第四节:ARM的memory model引言前言平时做ARM

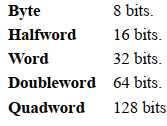

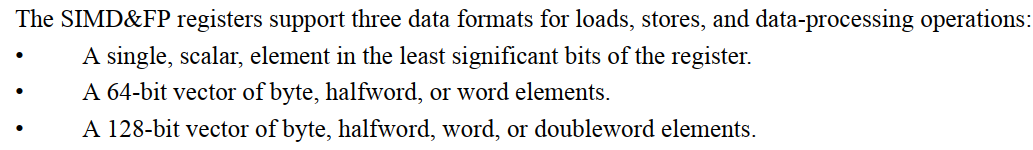

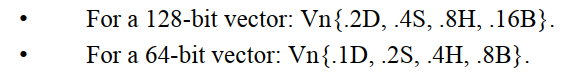

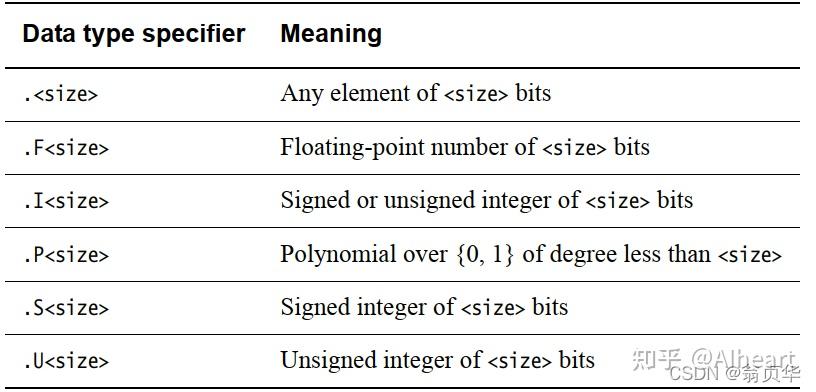

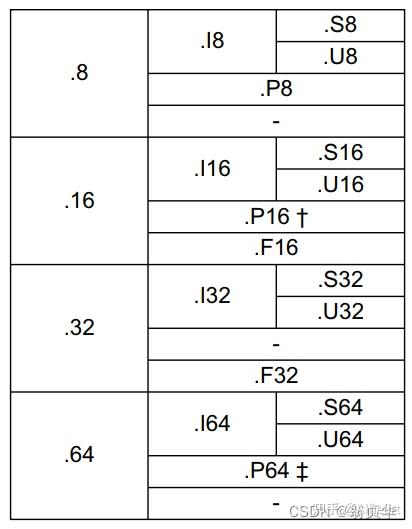

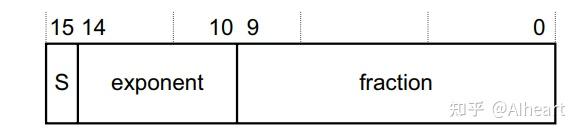

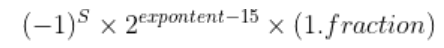

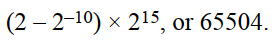

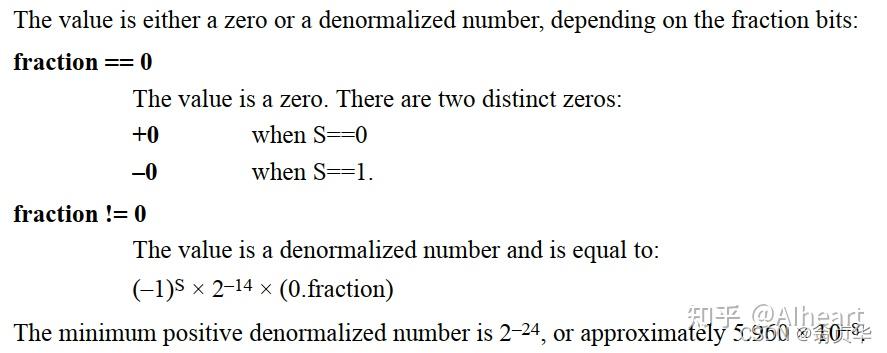

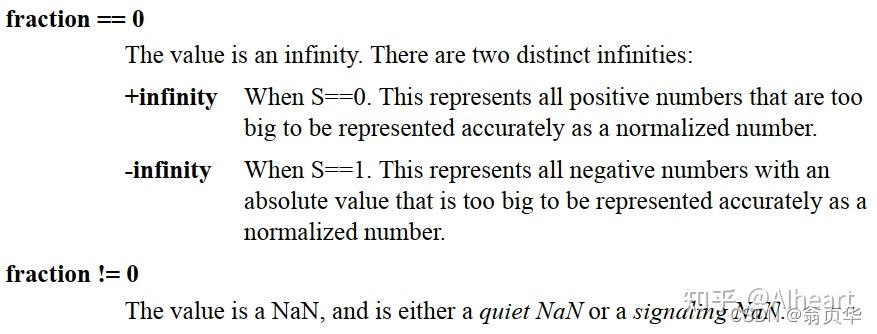

ARM V8 SPEC A1.1 ARM V8 架构的简介 第一节:ARM 架构基本概念 第二节:ARM架构提供的数据类型 第三节:高级SIMD和浮点 第四节:ARM的memory model引言 前言 平时做ARM cpu性能分析,国内ARM相关的新资料很少,所以在学习的过程中,将自己的理解记录下,供ARM新人参考 第一节:ARM架构基本概念 arm reference 是对processing element简称(PE)行为的定义, PE可以理解为处理单,重点是行为的定义,而不是具体设计的定义或者限制,此外也对软件开发者使用ARM PE进行了说明。 此外ARM还有用于debug的架构,trace(追踪)架构,后面章节介绍.由于ARM架构具有:1,统一的寄存器文件;2.load,store的架构,数据的运算仅在寄存器上进行;3,简单的地址模式,所有的地址来源于寄存器的内容和指令的filed.所以arm架构属于精简指令集。此外架构还定义了PE和memory的交互行为,其中包括了cache, memory translation。【关键名字释义】 AArch64: 64-bit execution state; 地址保存在64-bit registers;31 个通用寄存器,X30是程序链接寄存器,提供了64 bit的PC, SP,以及异常链接寄存器,提供了32个128bit的SIMD向量和浮点寄存器;定义了ARM8的异常模型;支持64bit的虚拟地址;定义了一些PSTATE的寄存器来存储PE state;定义了不同级别的系统寄存器;仅支持一个指令集:A64AArch32: 32-bit execution state; 地址保存在32-bit registers;13个32bit 的通用寄存器;32个64bit的SMID寄存器和浮点寄存器;…etc;支持两个指令集:A32和T32(32和16bit混用的指令编码)ARM: Application profile(VMSA); Real-time profile(PMSA); Microcontroller profile;Excution state:执行环境,包括:支持的寄存器位宽,支持的指令集,其中最重要的部分包括:异常模型,VMSA,程序员的模型,其中很重要的一种环境是是执行在AArch64还是32,对于AArch64:system register: 提供了控制和info;系统寄存器主要包含以下三个部分:1.系统通用控制寄存器;2.debug寄存器;3;时钟寄存器;4.pmr,性能监测寄存器;5.活动检测寄存器;6,trace 寄存器;7,GIC(General interrupt control)系统寄存器ARM V8 debug :ARM V8支持self-host debug(PE自己产生debug exception) 以及 external debug(debug event 自己产生debug state, PE是被外部控制下产生debug expection;这两者的使用场景不同,前者一般使用在应用后期维护中,后者使用在开发阶段。 第二节:ARM架构支持的数据类型

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们 举报,一经查实,本站将立刻删除。

文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/63860.html