Untitled Document 目前,在计算机系统中使用的随机存储器的存储容量一般都比较大,那么,如何从大量的存储单中选择我们需要的一个存储单呢? 对于小容量存储器,如寄存器堆等,可以采用一维的线选择法。对n位地址直接用译码器译出2n条选择线,分别选择2n个存储单。当存储器的容量比较大时,线选择法的代价很高。 例如,对于一个64MB的存储器,有26位地址,如果采用线选择法,译码器的输出要有226=67 108 864条选择线,这是很难实现的。 图4.5是采用二维的重合选择法的4M′4位DRAM内部结构图,它把22位(222=4M)地址线分为行地址和列地址两部分分别进行译码,只有行地址和列地址重合的存储单才被选中。 采用重合选择法,译码器的规模大大减小了。 假设一个存储器的地址码为n位,存储器的容量为2n,如果采用线选择法,译码器的规模为2n,如果改用重合选择法,则译码器的规模减小到两个2n/2+1,减小了2n/2-1倍。例如,对于图4.4所示的4M′4位DRAM存储器,译码器的规模减小了1000多倍。 在DRAM中,为了减少存储器芯片的引腿数目(对VLSI,这是一个非常重要的问题),通常采用如下两个办法:(1)地址线复用 把地址线分为两个相等的部分,分别称为行地址和列地址,分两次从相同的引腿送入芯片中。 图4.5 4Mx4位DRAM结构图 对于4M′4位的DRAM,共有22位地址,但是,存储器芯片的地址引腿数只有11条,22位地址要在行地址选择 (row address select)和列地址选择 (column address select)的控制下,分两次送使用相同的11条地址线送入到存储器芯片中。 另外,图4.5中的 为读写控制, 为”1″表示读,为”0″表示写。 为片选,用来扩充存储器的容量,具体方法将在下一节中介绍。 (2)尽量减少数据线 例如,一个存储器有m(m>1)条数据线和n条地址线,则这个存储器的容量为m′22n bit。如果把数据线减少到1条,仍然保持数据线与地址线的总和为m+n条不变,则存储容量从m′22n增加到22n+2(m-1) bit,增加了22(m-1)/m倍。 对于一个1M′8位的DRAM存储器,如果把数据线减少到1条,把原来的7条数据线改作地址线,则地址线由原来的10条增加到17条,这个DRAM存储器的容量将增加到16G′1位,增加了2048倍。

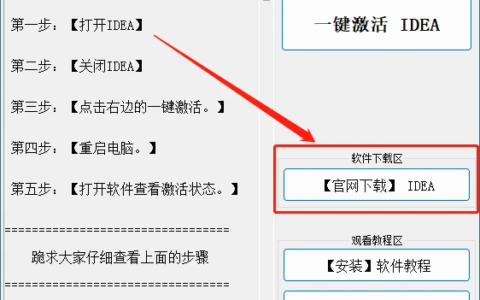

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/59724.html