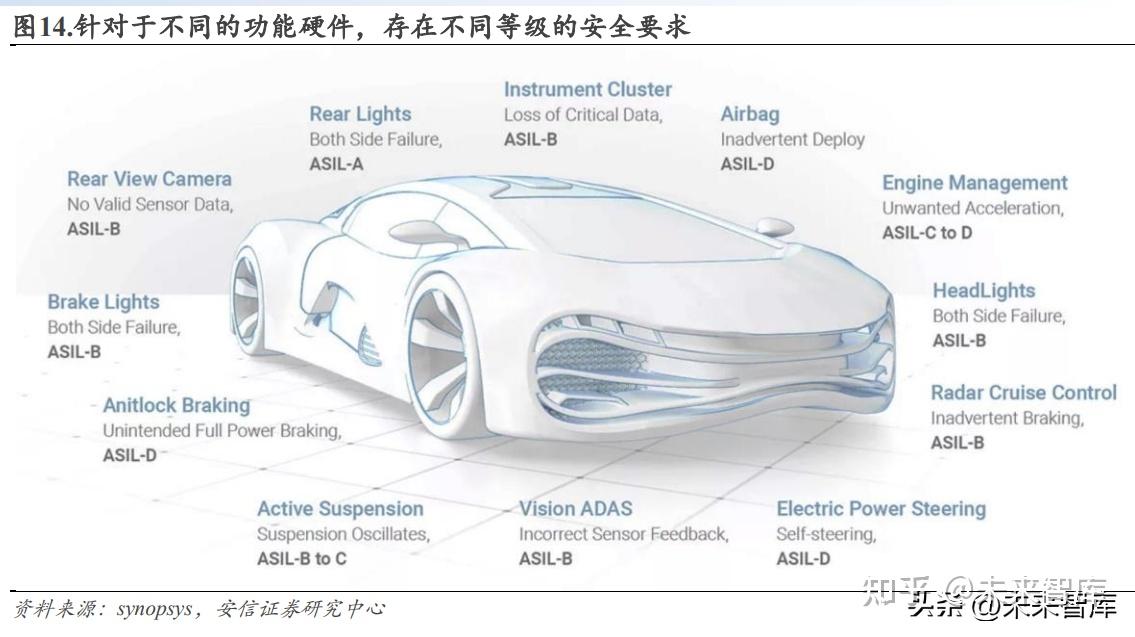

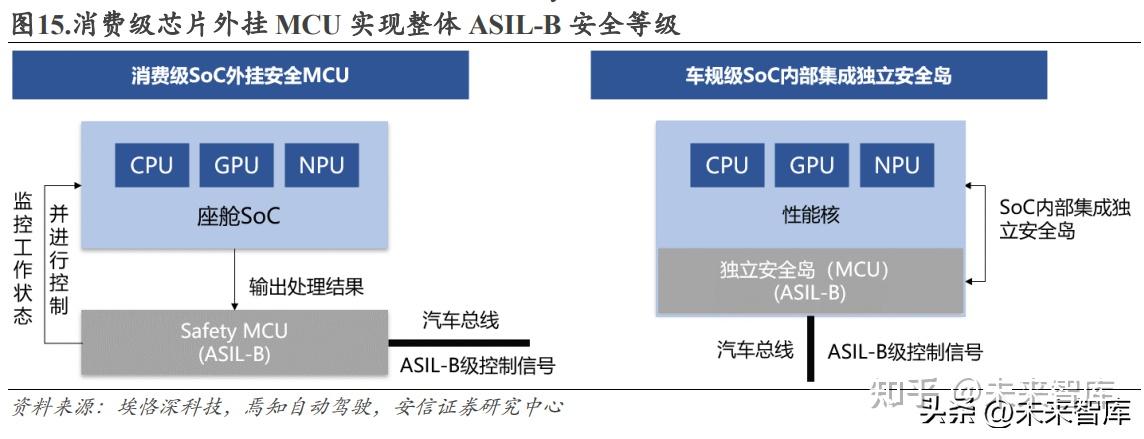

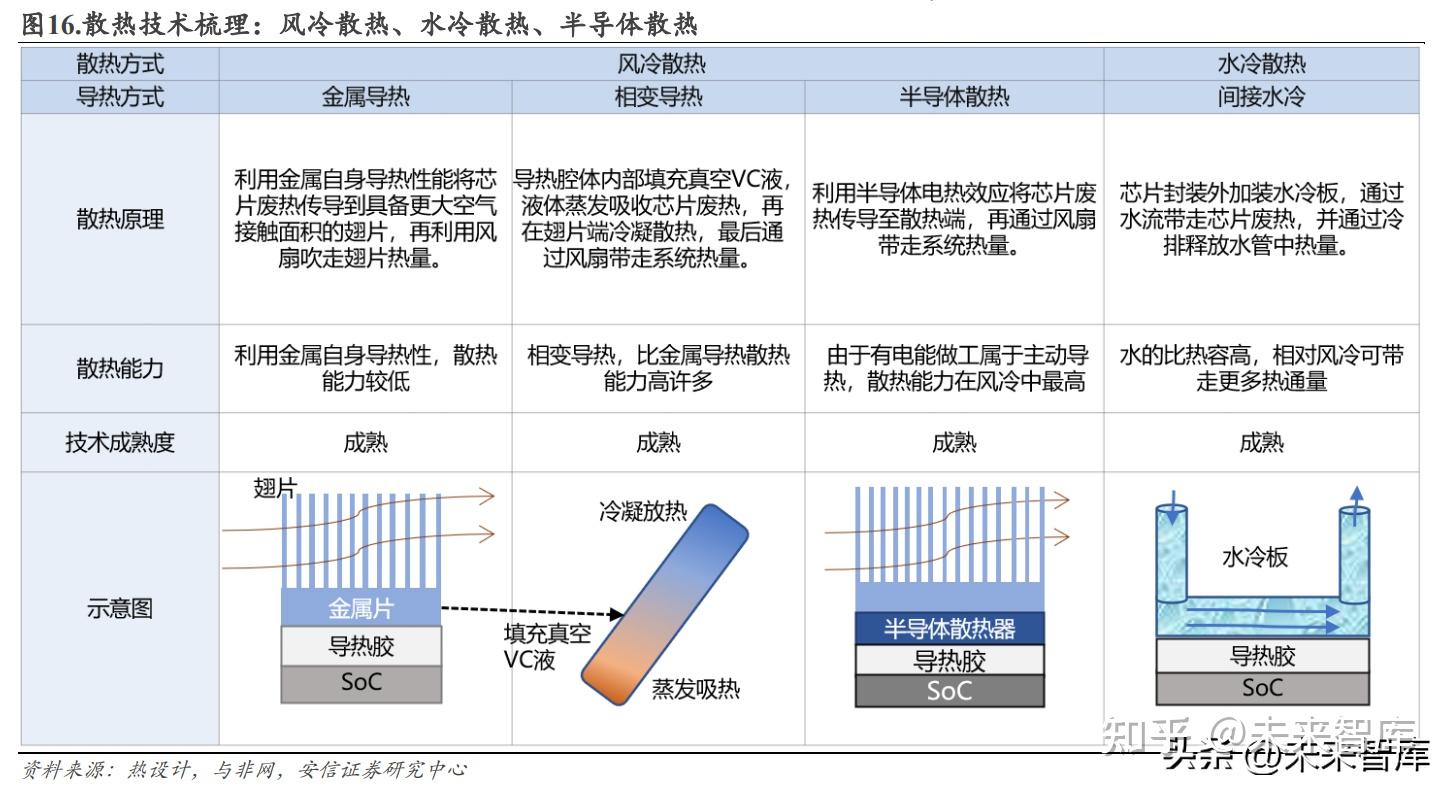

智能汽车2023年度策略:座舱迈入2.0时代,车机域控格局或将再重塑 (报告出品方/作者:安信证券,徐慧雄,李泽) 1.智能座舱迈向2.0时代,成本、功能需求推动车机芯片逐步差异化 1.1.智能座舱1.0时代,消费电子厂商切入、高通在车机领域呈现压倒性优势 头部主机厂 E/E 架构已完成由分布式向域集中式升级,座舱智能化功能的实现集中于域控制 器的主控芯片。早期的车机功能相对简单,仅具备收音机及音频播放等功能,且功能的实现 依赖于相互独立的 MCU,即采用分布式 E/E 架构,功能的升级亦通过叠加 MCU 及相关功能 配件完成。而在域集中式的硬件方案设计下,座舱内多数智能化功能的实现仅依赖于单一的 座舱域控制器主控芯片。 当面向不同安全功能等级的功能时(例如仪表显示屏涉及驾驶安全要求ASIL-B安全等级,而中控屏主要为导航及影音娱乐功能安全等级要求不高),可通过软件虚拟机技术对SoC 资源动态调配或直接在 SoC 内硬件隔离,进而实现单芯片运行多个操作系统,保障驾驶相关功能的实时性、安全性。相对于分布式架构,域集中式的设计,一方面可提高控制芯片及外围电路复用效率,降低整体座舱芯片成本,另一方面可增强不同功能配置之间的通信效率,实现中控对座舱的集中控制,为跨屏互动提供硬件基础,并可实现OTA在线升级功能。 集中式架构下座舱智能化加速升级,推动座舱主控芯片性能要求持续提升。具体体现: (1)车机功能丰富度提升,要求具备更低延时、高性能的 CPU。集中式架构下空调、座椅、 天窗等车身控制功能均集中于车机处理器。同时座舱功能的丰富度也在提升,从传统的 收音机、音频功能升级到导航、影音应用,目前正向更高阶的桌面级游戏应用延伸。作 为座舱 SoC 的“大脑”,CPU 的低延时处理需求在集中式架构下大幅提升。目前,高通座 舱芯片的CPU性能已从8155的105k DMIPS提升至当前8295的220k DMIPS(预估值), 性能实现翻倍增长。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/47312.html

,前端高级工程师进阶学习—前端热修复原理)缩略图 PyCharm2024.1.4激活码(2024年Windows安装PyCharm2024教程[转载](1),前端高级工程师进阶学习—前端热修复原理)](https://sigusoft.com/wp-content/uploads/2024/07/dnNUYAznZo-480x300.png)