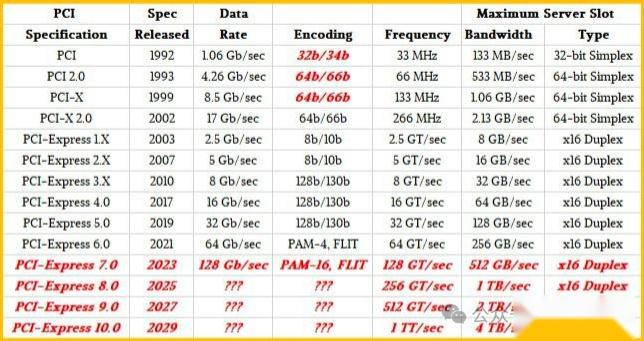

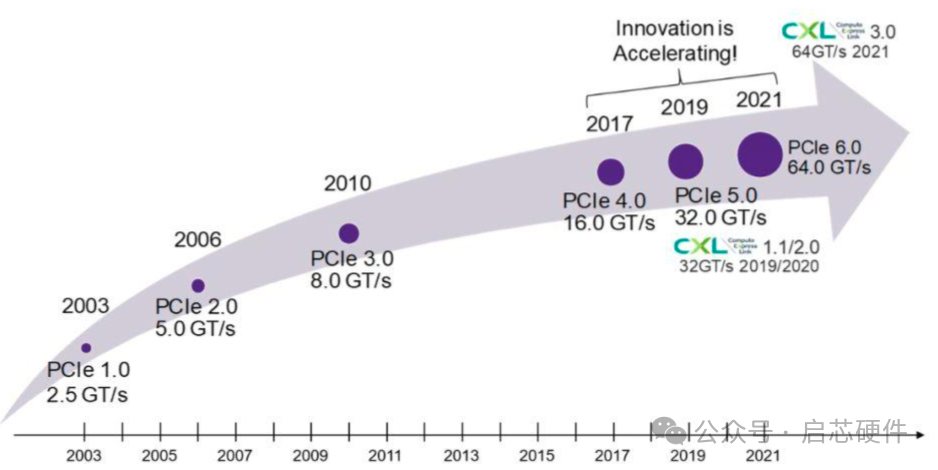

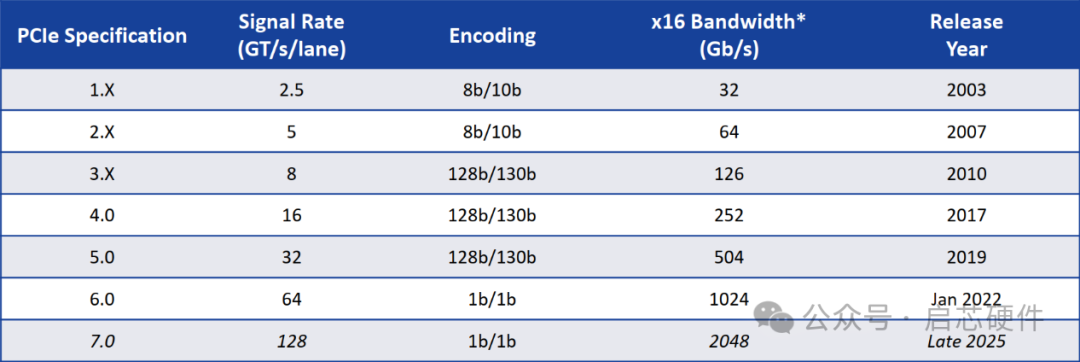

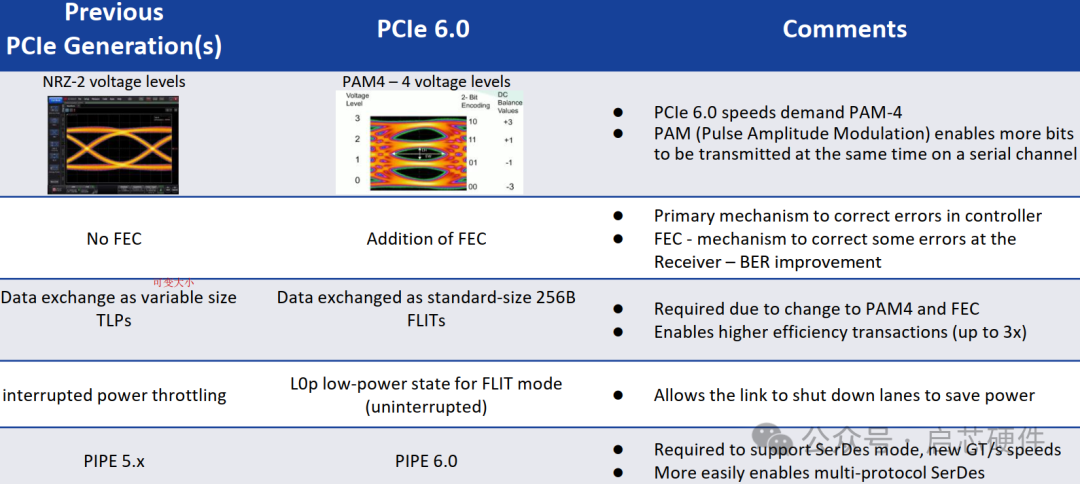

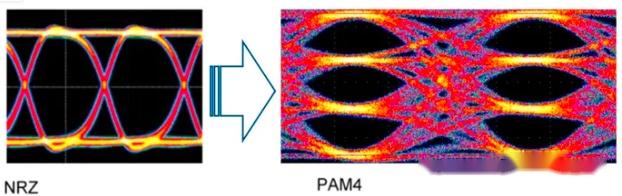

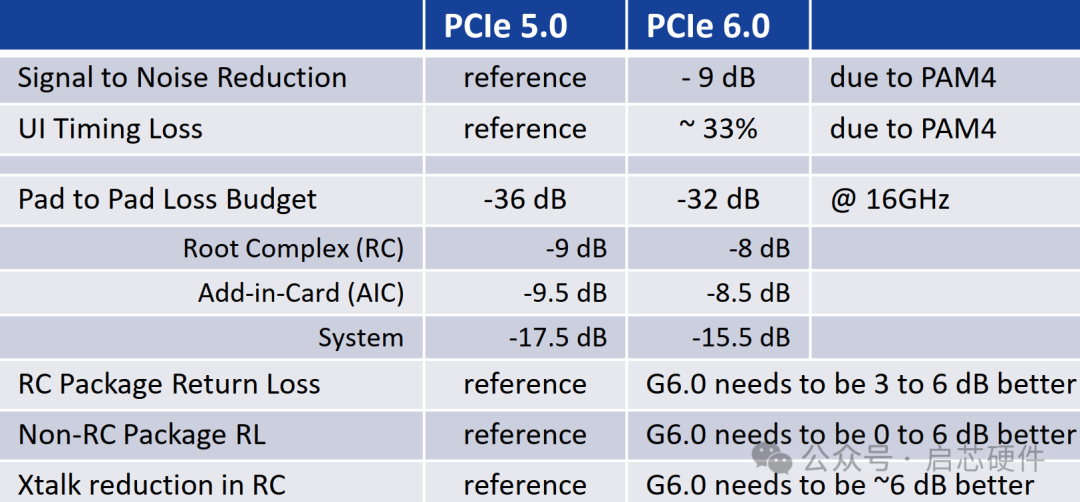

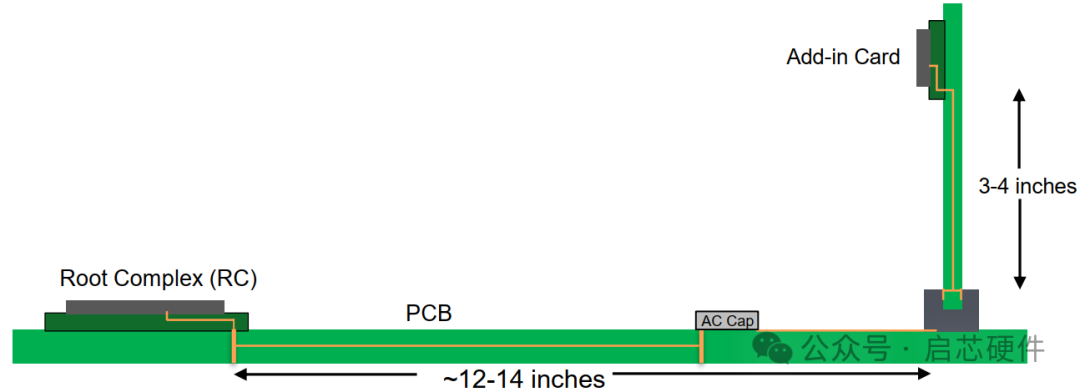

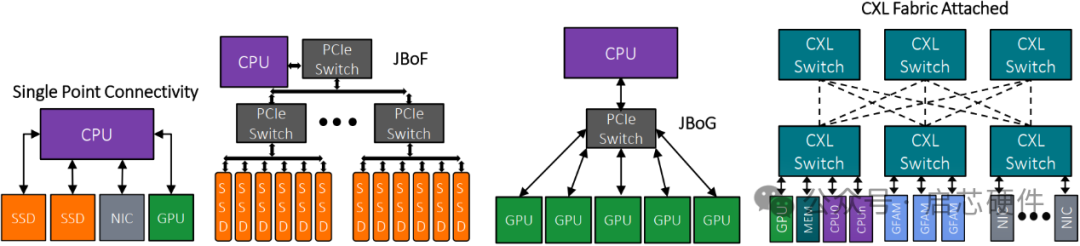

一文了解PCIe 6.0的基础和测试 2022年PCI-SIG组织宣布PCIe 6.0规范标准v1.0版本正式发布,宣告完工。 延续了惯例,带宽速度继续增倍,x16下可达128GB/s(单向),由于PCIe技术允许数据全双工双向流动,因此双向总吞吐量就是256GB/s。 •Definitions/Metrics to Help Frame Server Design Challenges • Disaggregation: dividing components and resources into subsystems • Fabric attached: components attached in a mesh, including across network, allowingaccessibility to a series of servers • GFAM: Global Fabric Attached Memory • IE: Fabric Attached Storage, Fabric Attached Memory • Stranded memory: memory attached to a CPU that is accessed infrequently or not at all • Metrics of interest contributing to server cost • Estimated server memory cost – ~30% – 50% of total server cost • Average utilization of DRAM (40%-50%) If memory pooling could reduce total DRAM by 10%, total server costs could reduce by 4%-5% Typical Applications Using PCIe and CXL Interfaces

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/47180.html