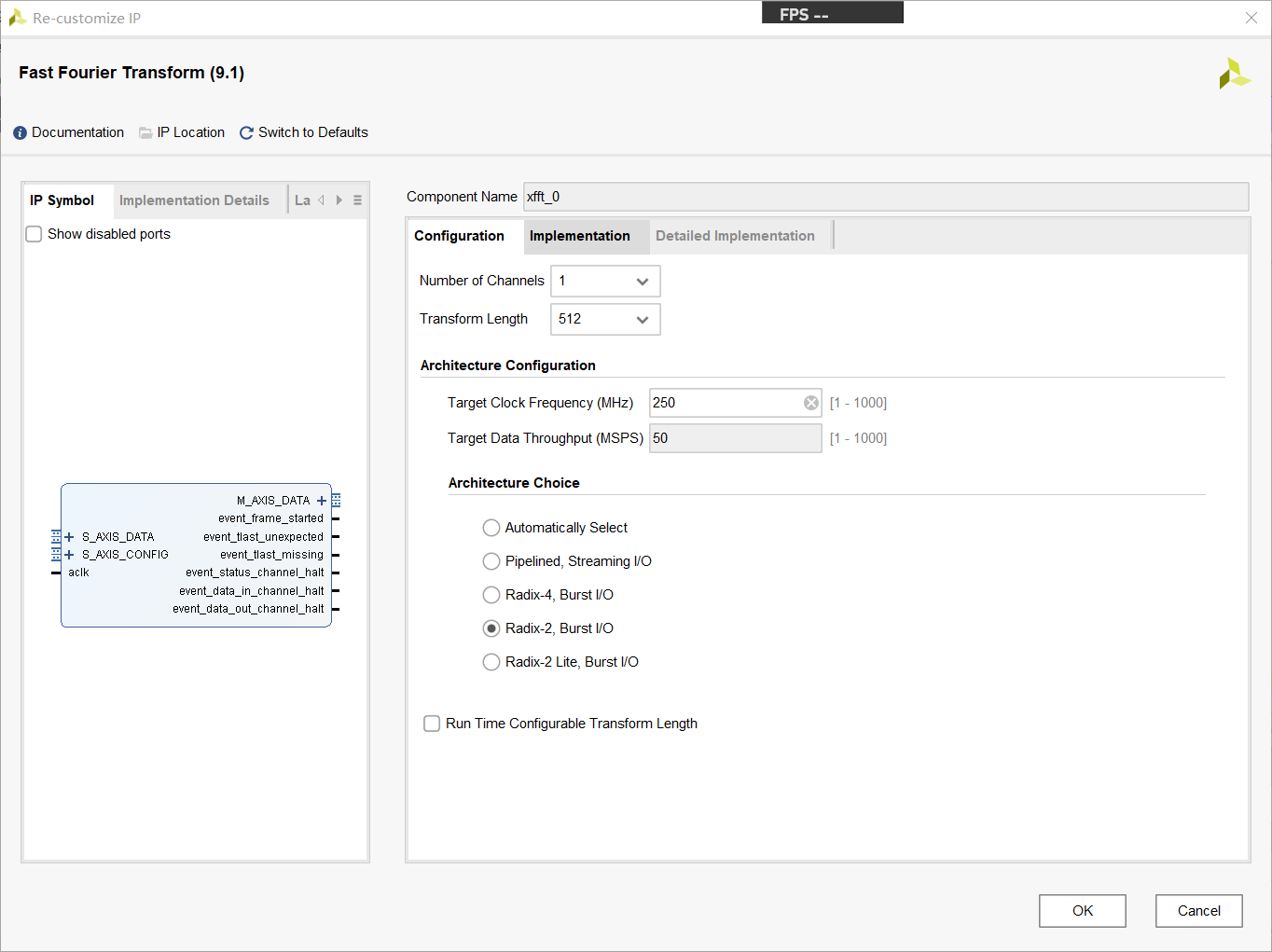

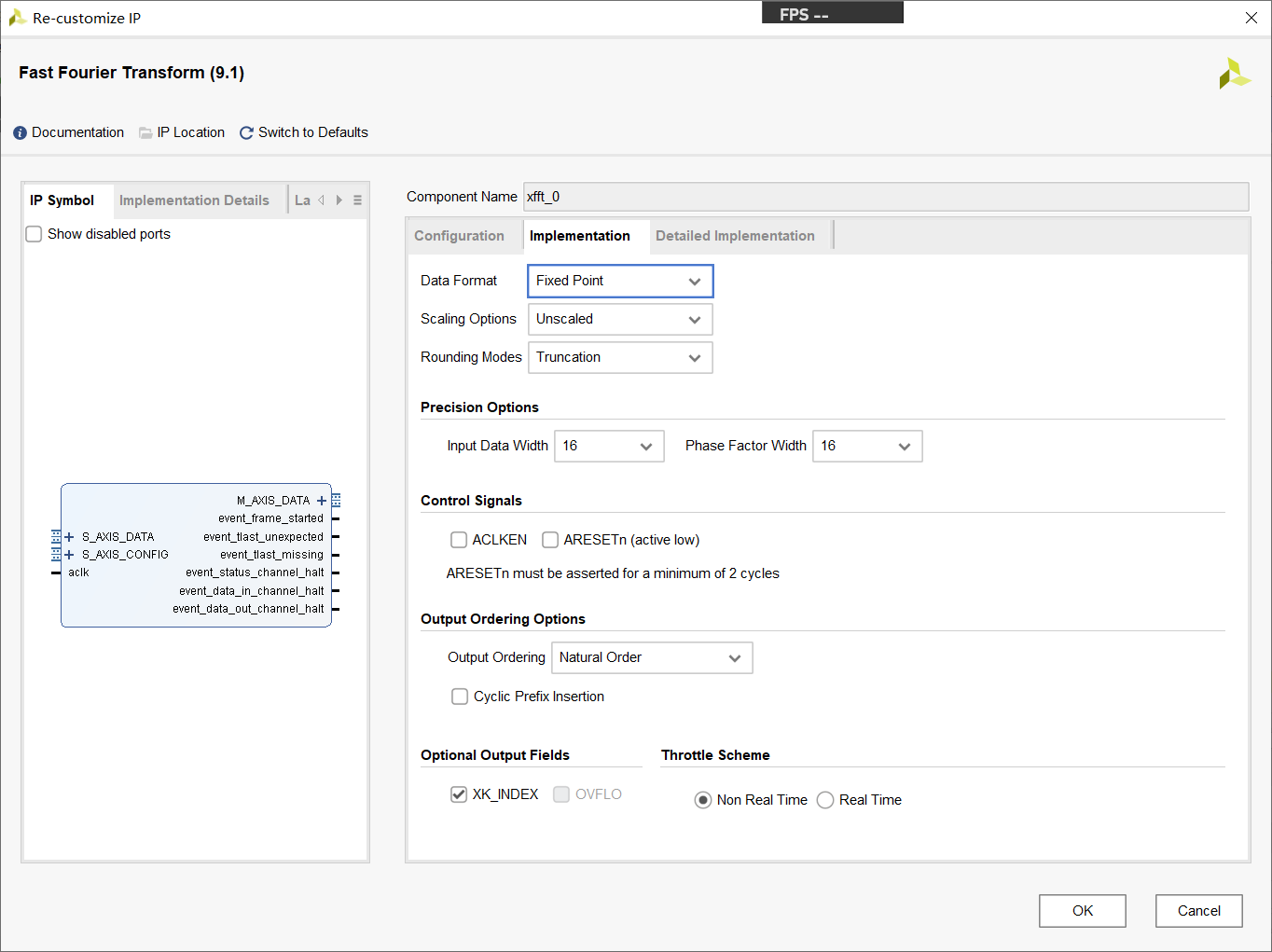

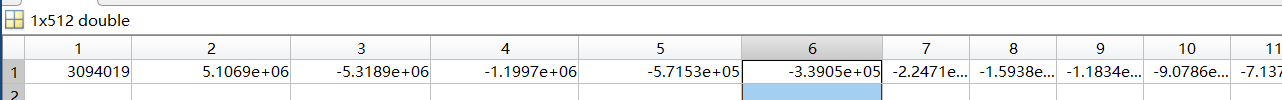

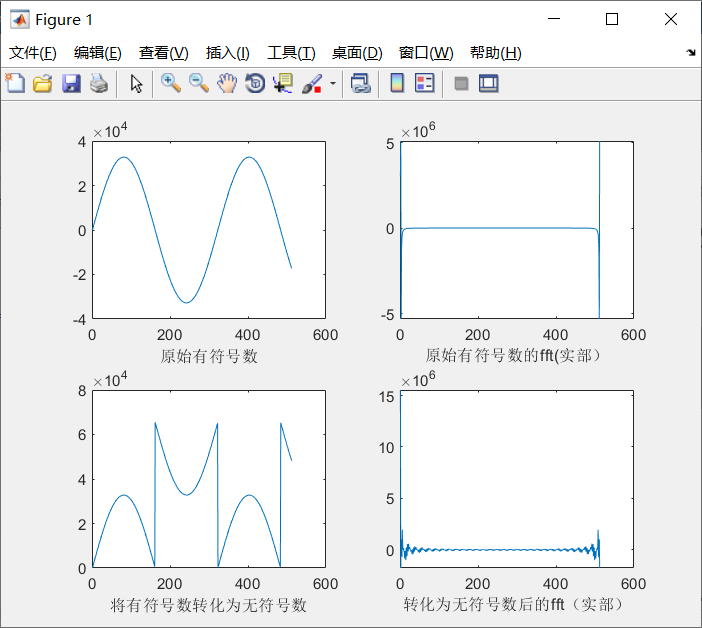

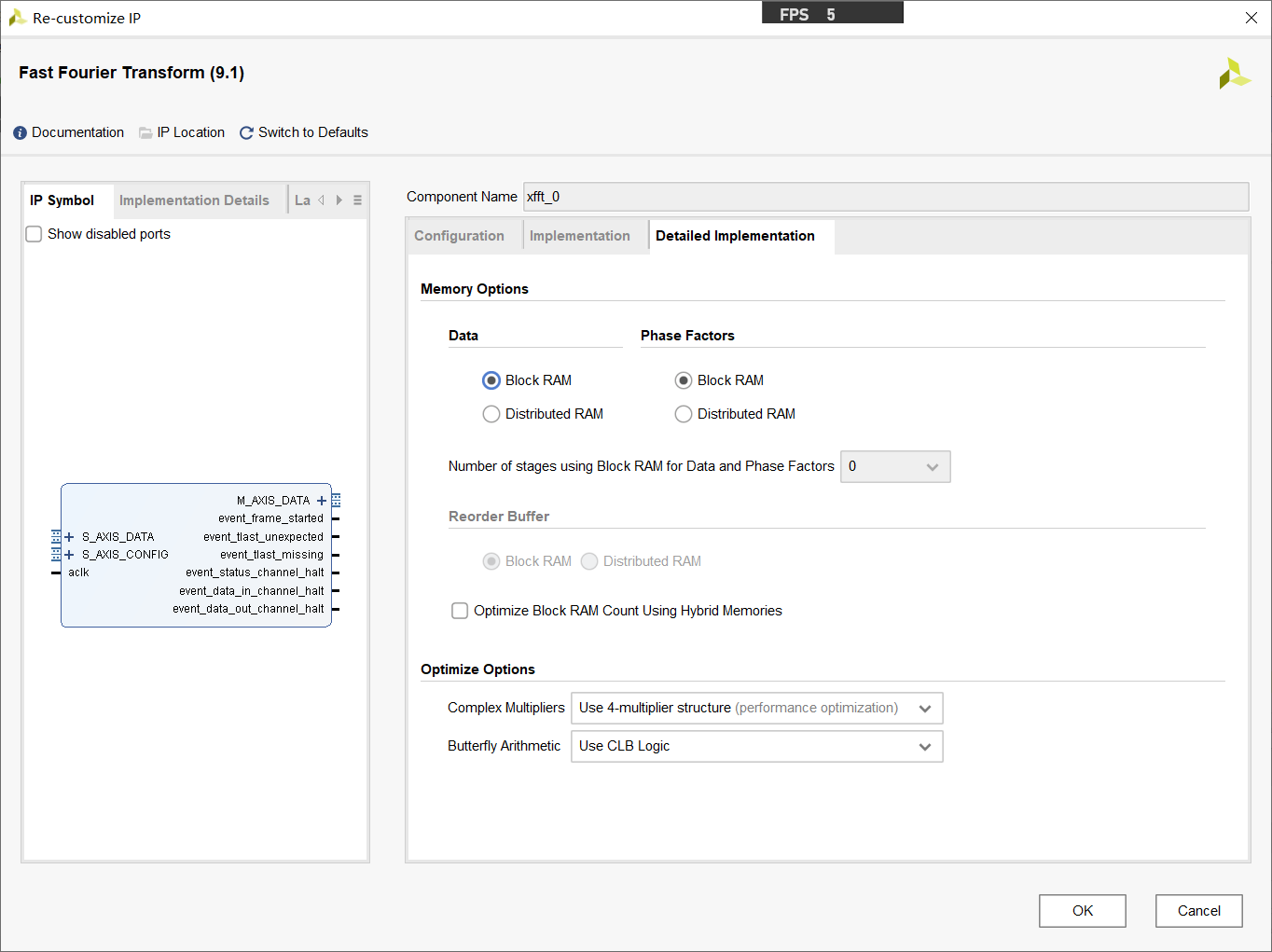

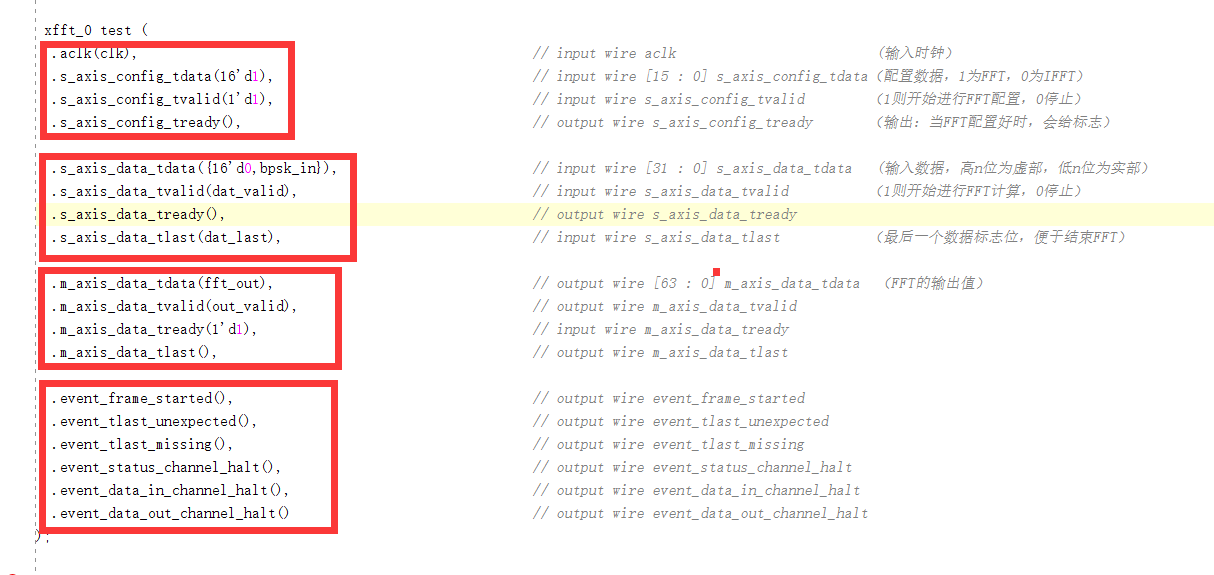

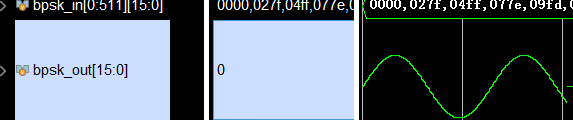

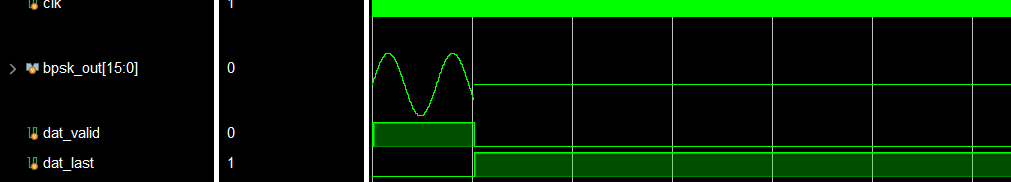

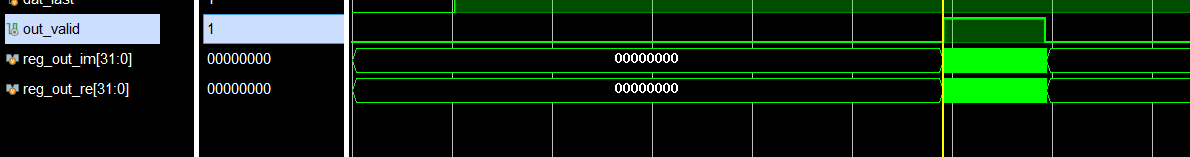

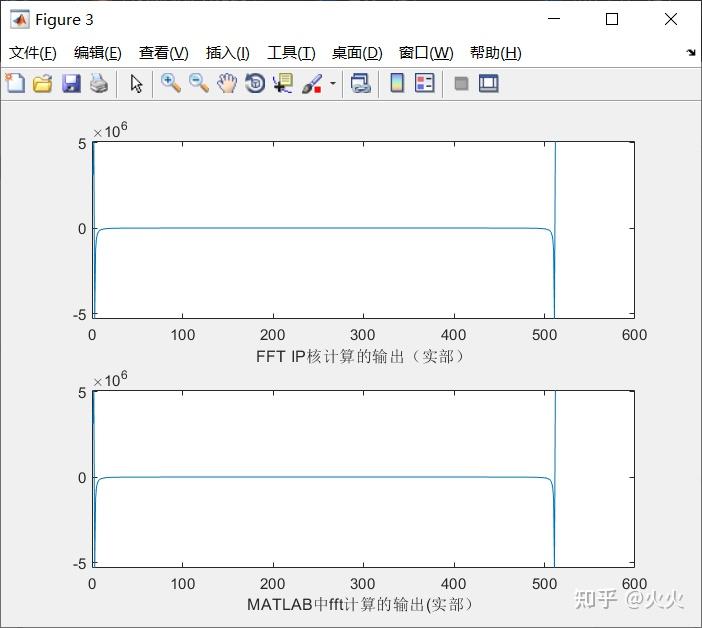

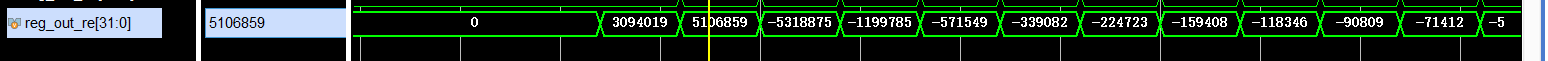

Vivado IP核:FFT实验 本实验的目的是熟练使用vivado中的FFT核,并且为我将来在verilog代码中实现pwelch函数估计功率谱来做铺垫。 实验方法: 第一步:使用matlab产生正弦波,并且导入vivado中作为待FFT处理的信号 需要注意的地方:浮点数运算复杂,因此需要对正弦波进行量化 使用floor函数进行四舍五入取整,考虑到有符号数,只量化为15位,留一位作为符号位。 2. vivado不能直接读取负数,需要将负数转变为对应的有符号数 对于正负数的转化:是在原本15位数据的基础上加上符号位 以3位有符号数据为例,最高位是符号,那么-1就是 111。但如果把111看为无符号数,那么他就是7。 也即,三位符号数中-1就是无符号数中的7(计算过程为-1+2^3) 那么转到16位有符号数来说,也即为原负数加上2的16次方(代码中for循环可以体现)。 3. 如何根据时钟周期,将读取到的数据串行输出? 在testbench文件中读取数据,并且在for循环中依次串行输出 产生正弦波的matlab代码如下:

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/41769.html