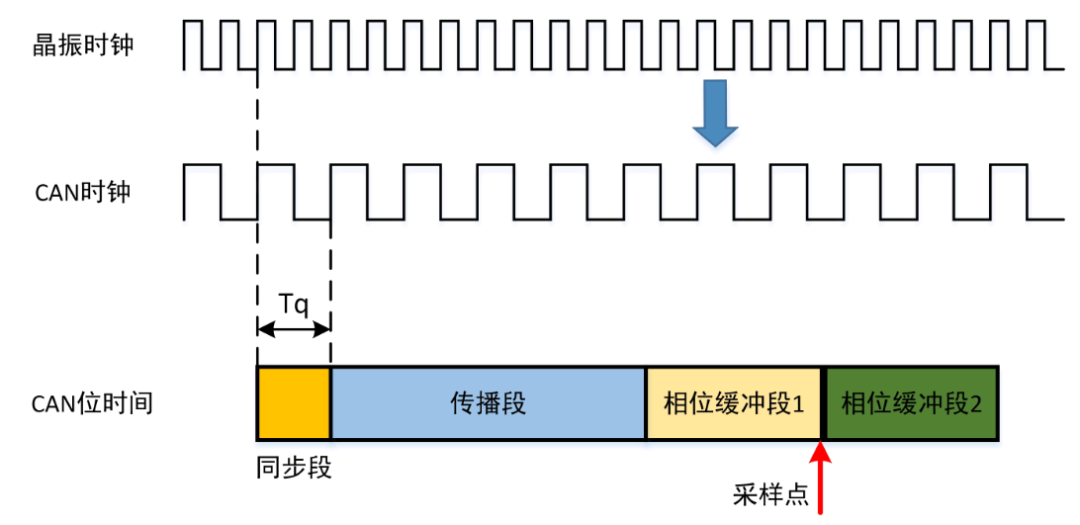

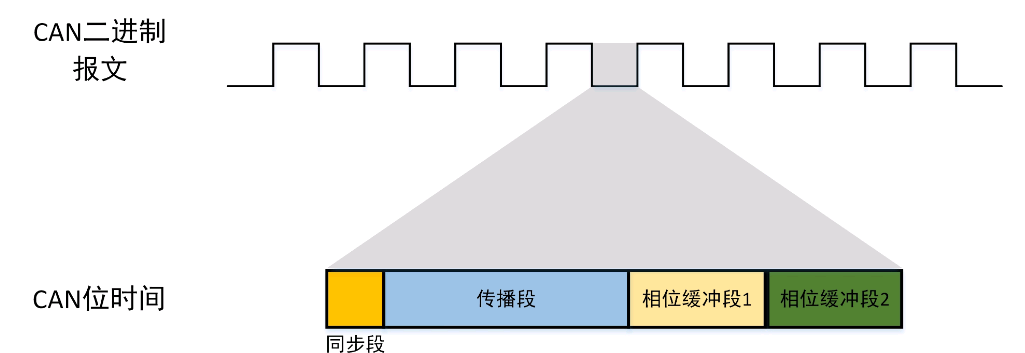

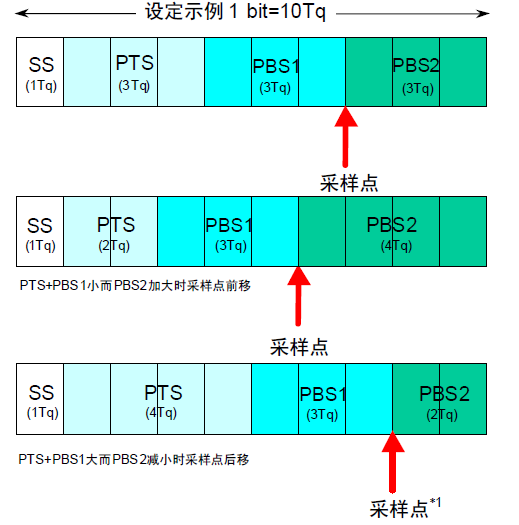

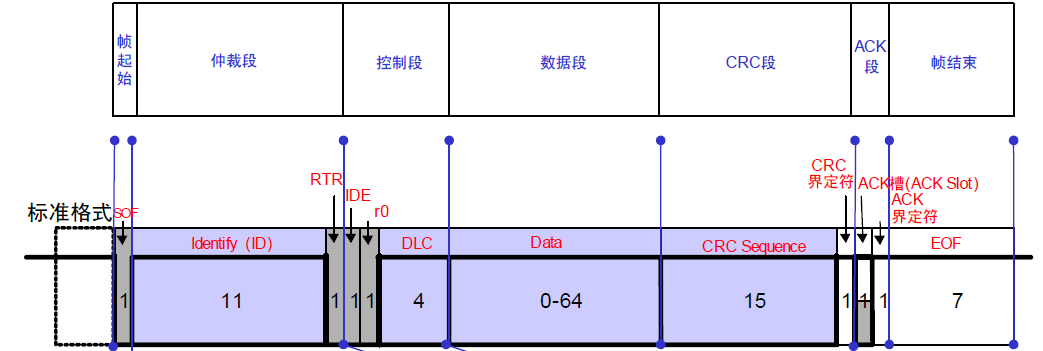

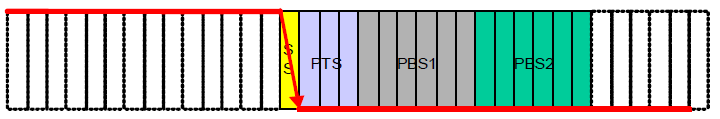

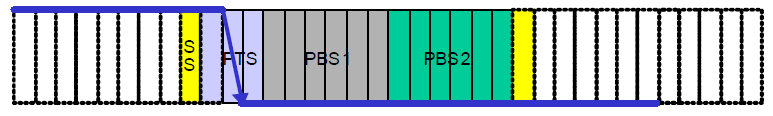

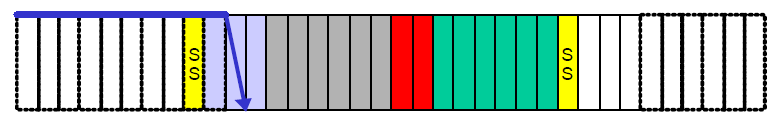

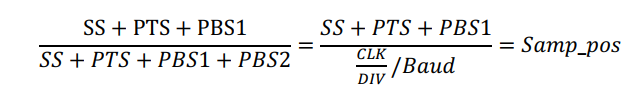

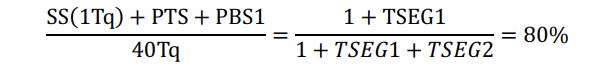

CAN同步机制,你真的了解吗? CAN总线作为异步通信方式,收发双方节点需约定相同的波特率进行通讯,但由于各种因素影响,接收方的数据总会有误差,当误差过大时,整个通讯网络将不能正常通讯。那么,该如何保障CAN节点之间通信同步呢? CAN同步机制 1、CAN时钟 首先了解一下CAN总线系统中的两个时钟:晶振时钟周期和CAN时钟周期。晶振时钟周期:是由单片机振荡器的晶振频率决定的,指的是振荡器每振荡一次所消耗的时间长度,也是整个系统中最小的时间单位。CAN时钟周期:CAN时钟是由系统时钟分频而来的时间长度值,实际上就是一个时间份额Tq。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/39070.html