学习笔记 — 计算机组成原理 0.前序 计算机文化素养课其一 计算机组成原理,简称“计组” 越向往高处的阳光,就越要扎根于无尽的黑暗 了解计算机的底层硬件的逻辑实现,CPU的处理架构,有助于我们更好的使用上层语言进行程序的编写 这篇文章我会对计组这门课程中的知识体系,其中的一些要点进行一个大致的总结归纳,但我毕竟不是专注于计算机硬件/嵌入式方向的开发者,因此对于一些重点不会过分的深究,本文也难免有一些理解不到位,或者谬误的地方 欢迎各路神仙留言指正或是赐教一些我不知道的点 若能不吝赐教,鄙人先谢为敬 1.概述 计算机组成原理:立于硬件之巅 —1.1 计组概述 计算机软件&硬件层级结构图:

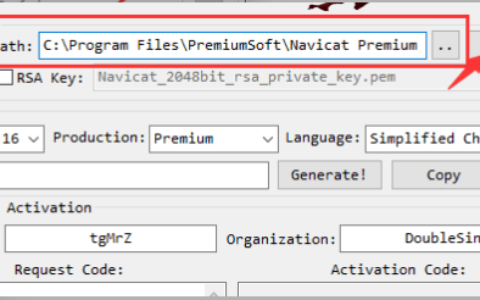

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/37761.html