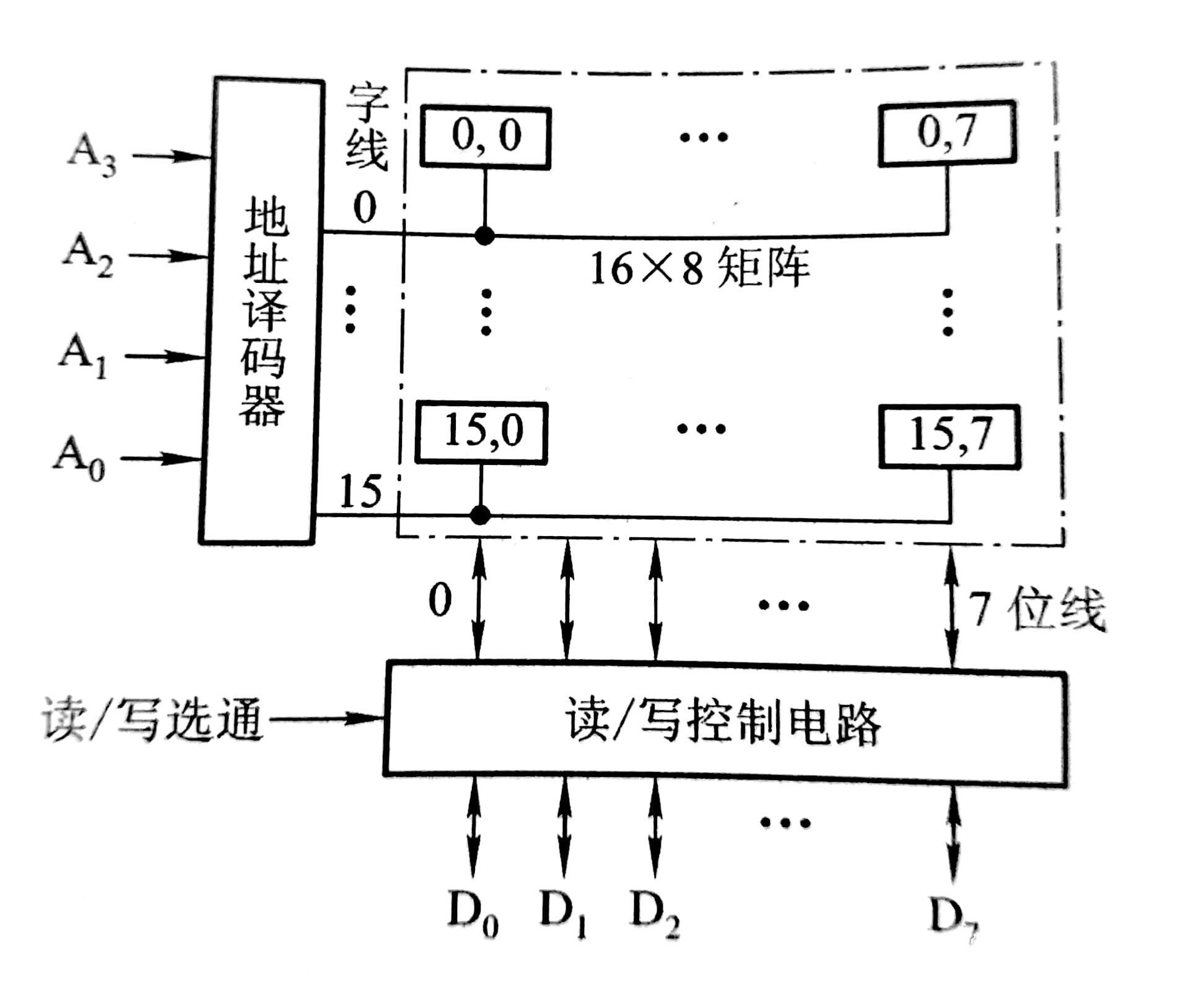

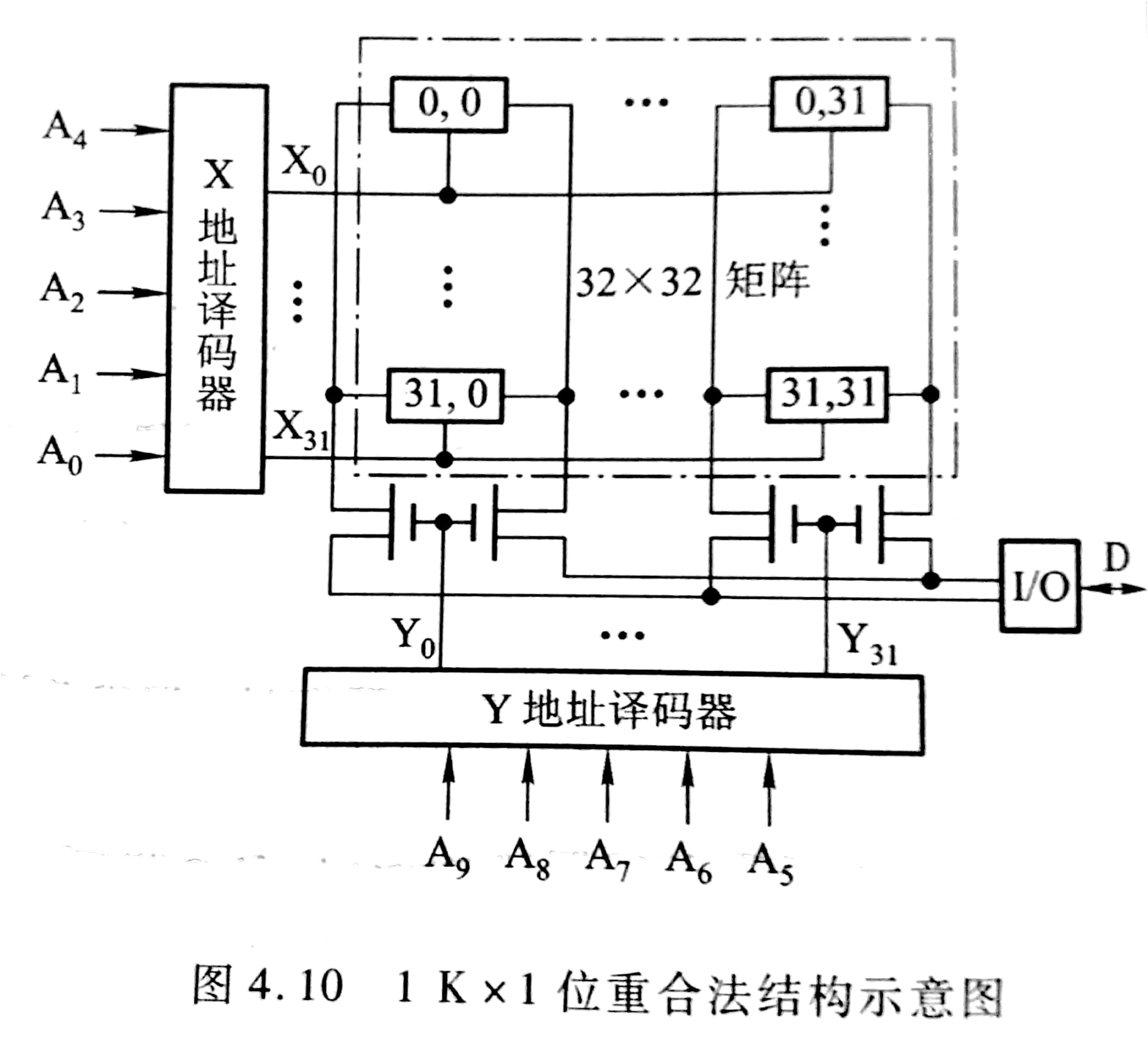

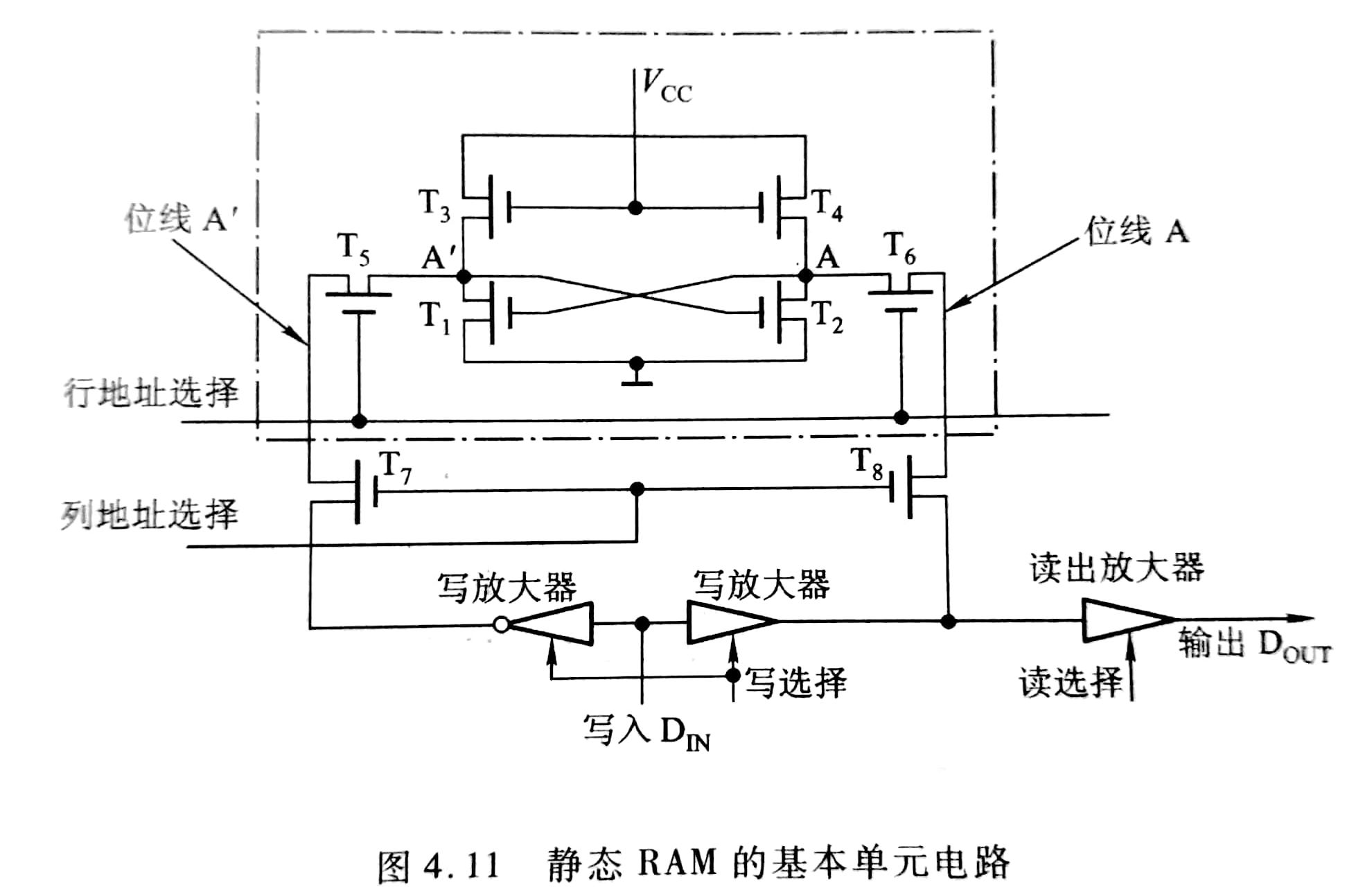

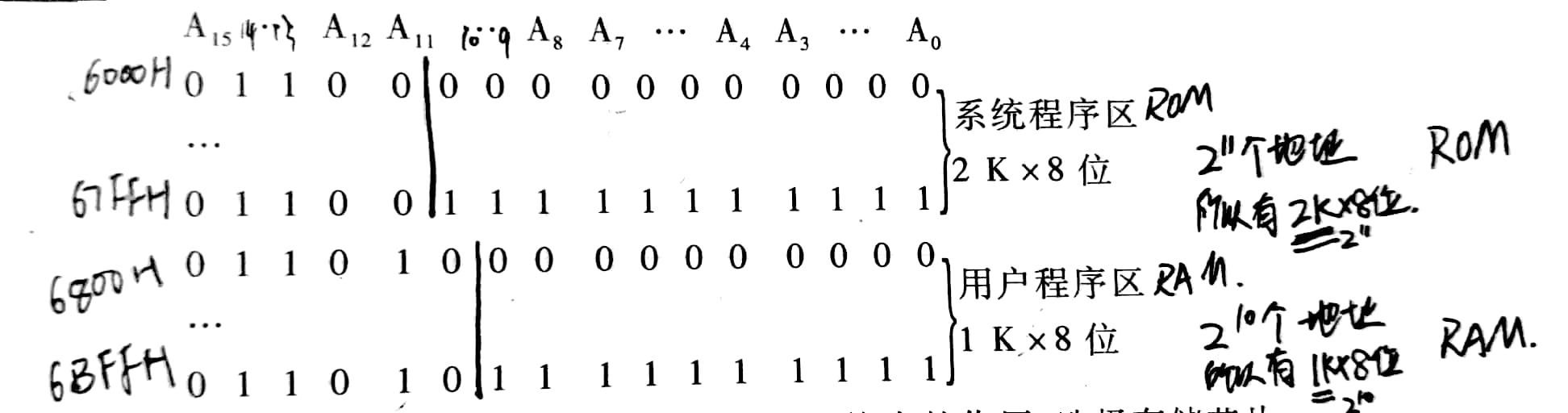

计算机组成原理-第四章-存储器+思维导图 计算机组成原理-第四章-存储器思维导图 思维导图在文末 目录 计算机组成原理-第四章-存储器思维导图 存储器 4.1概述 4.1.1存储器分类 1 按存储介质分类 2. 按存取方式分类 3.按在计算机的作用分类 4.1.2 存储器的层次结构 缓存——主存层次 主存——辅存层次 4.2主存储器 4.2.1概述 4.2.2半导体存储芯片简介 1.基本结构 2.半导体存储芯片的译码驱动方式 4.2.3随机存取存储器 3.1.静态RAM 3.2.动态RAM 3.3动态RAM与静态RAM比较 3.5动态RAM缺点 4.2.5存储器与CPU的连接 5.1存储器容量拓展 5.2存储器与CPU连接 4.2.6存储器的校验 4.2.7提高访存速度的措施 4.3高速缓冲存储器 4.3.1概述 4.3.2Cache——主存地址映射 4.3.3替换策略 4.4辅助存储器 4.4.1概述 4.4.2磁记录原理和记录方式 4.4.3硬磁盘存储器 4.4.3软磁盘存储器 4.4.5磁带存储器 4.4.6循环冗余检验码 4.4.7光盘存储器 存储器 4.1概述 4.1.1存储器分类 1 按存储介质分类 半导体存储器 磁表面存储器 磁芯存储器 光盘存储器 2. 按存取方式分类 随机存取器 只读存储器 串行访问存储器 3.按在计算机的作用分类 主存储器、 辅助存储器 缓冲存储器。 4.1.2 存储器的层次结构 缓存——主存层次 解决CPU和主存速度不匹配的问题 主存——辅存层次 主要解决存储系统容量问题 4.2主存储器 4.2.1概述 主存储存单地址的分配:常用8位为进制数表示一个字节 主存的技术指标是:存储容量和速度 1.存储容量:存储容量=存储单个数*存储字长 字节表示除8即可 2.存储速度:由存取时间和存取周期来表示 3.存储器带宽:表示单位时间内存储器存取信息量,单位:字/秒或字节/秒或位/秒 4.2.2半导体存储芯片简介 1.基本结构 地址线:单向输入的,其位数与芯片容量有关 数据线:双向的其位数与芯片可读出或写入的数据有关。数据线的位数与芯片容量有关 控制线:主要有读写控制线与片选线两种。 地址线和数据线的位数共同反映存储芯片的容量 2.半导体存储芯片的译码驱动方式 1.线选法

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/37330.html