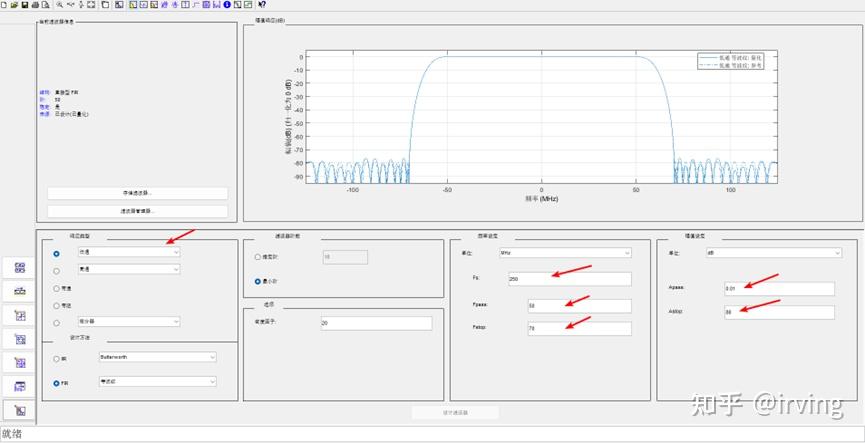

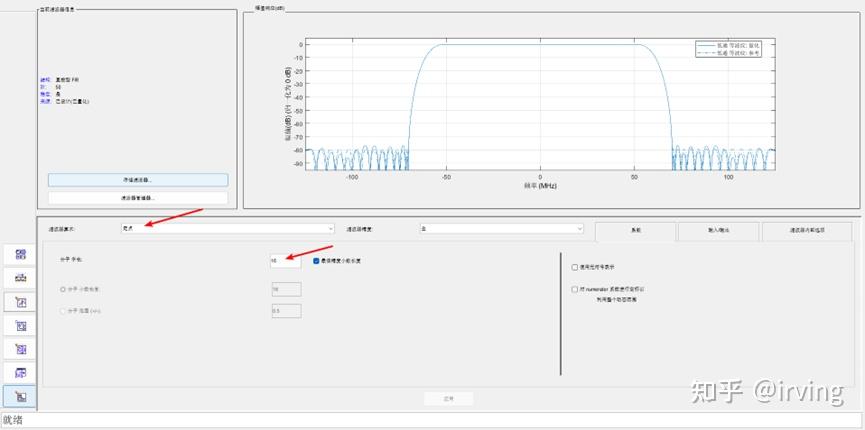

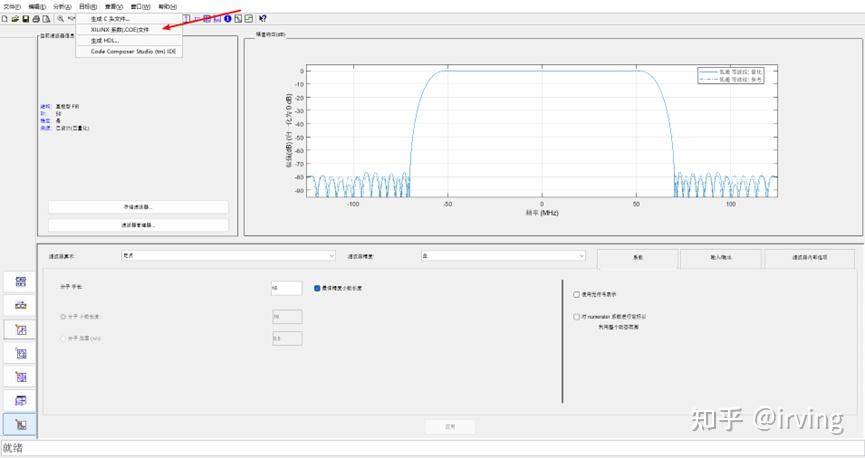

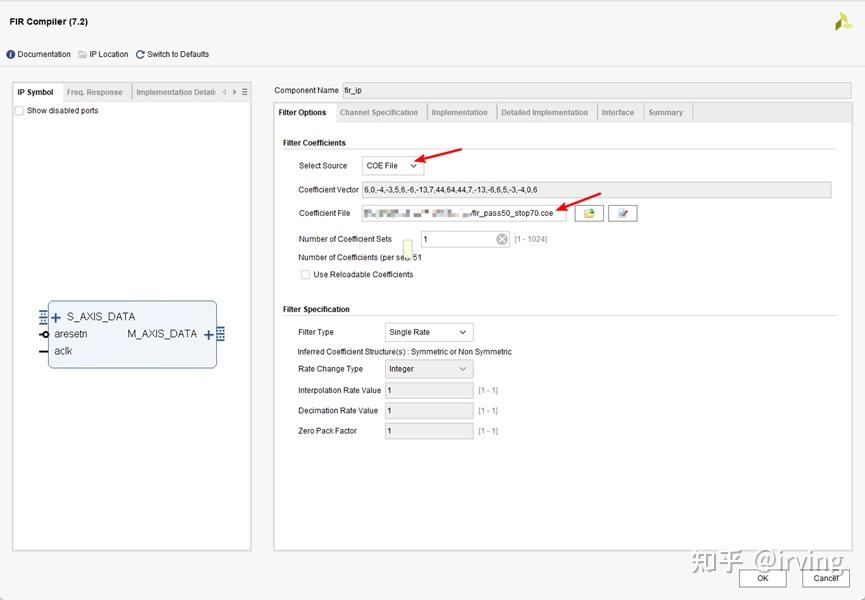

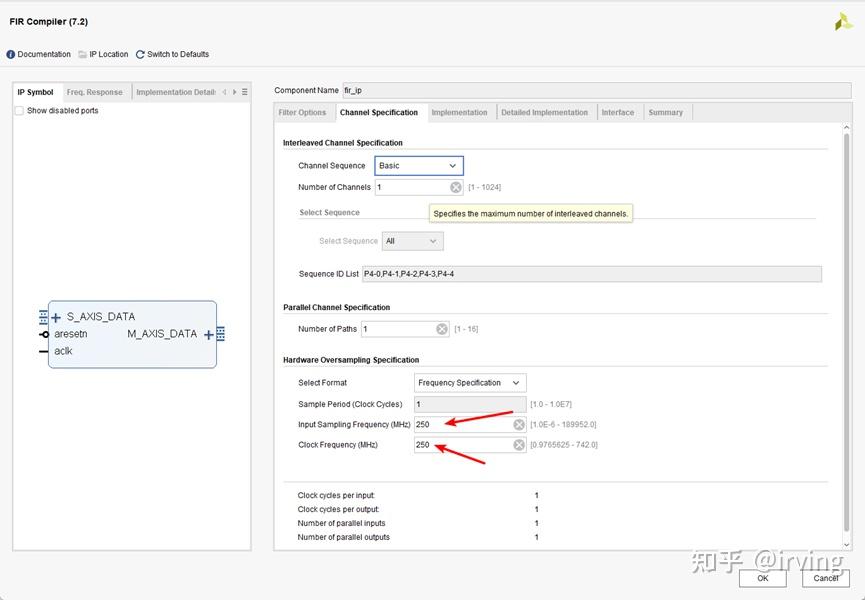

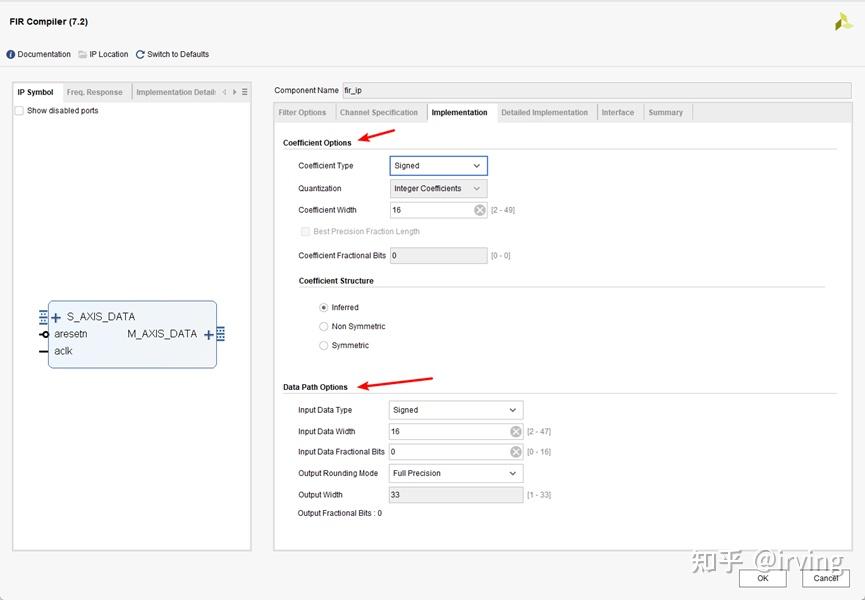

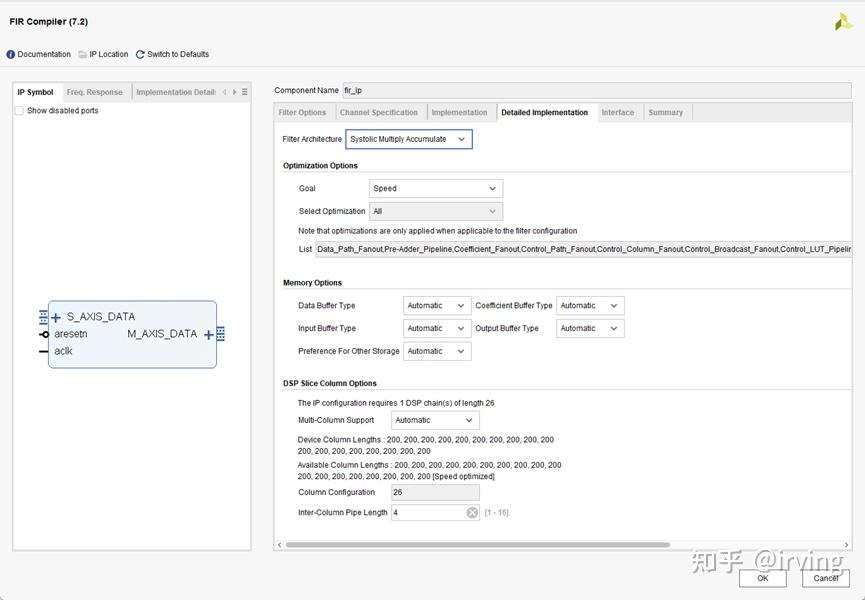

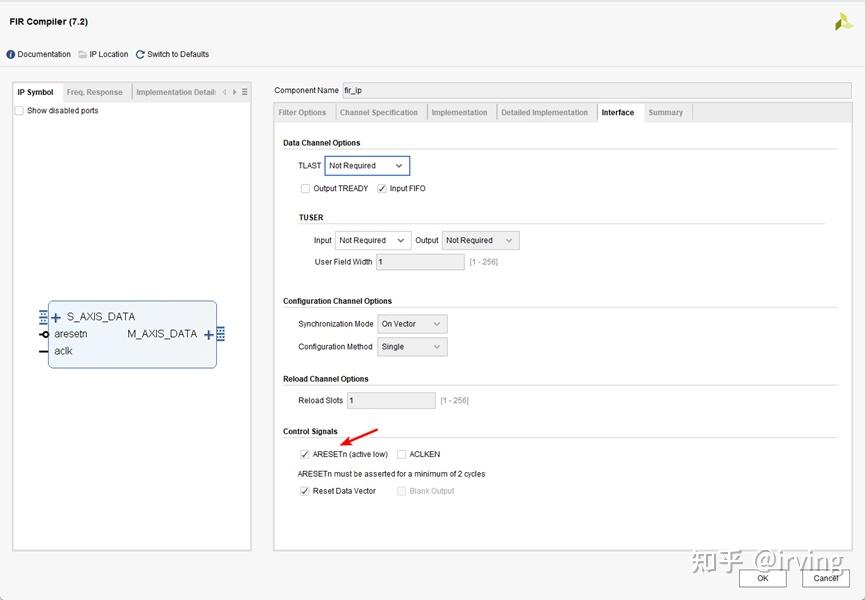

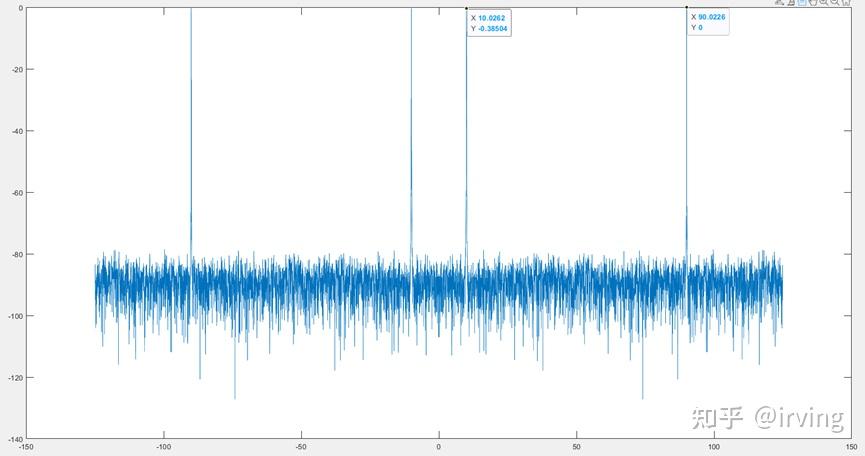

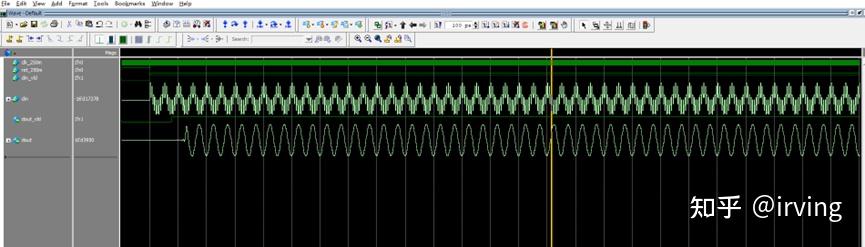

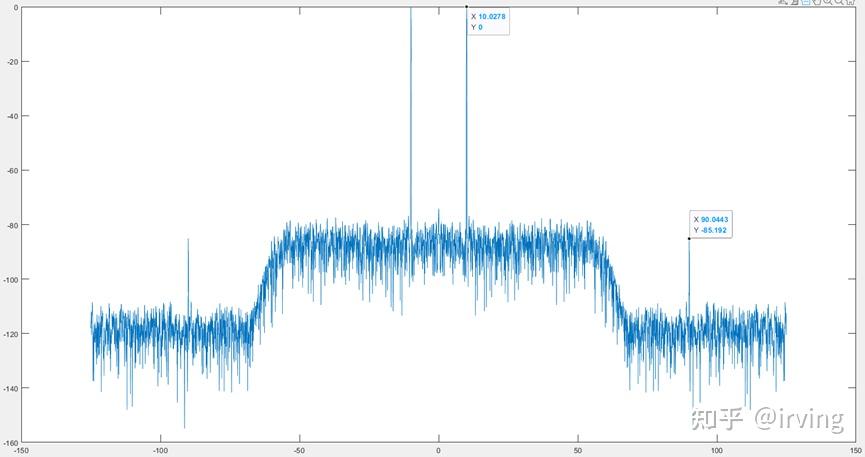

Xilinx FIR IP核设计滤波器 fir ip使用流程 使用matlab工具,根据具体需求设计出滤波器系数; 打开fir ip导入滤波器系数即可; 滤波器系数的生成 1. 打开matlab使用fdatool工具,填入相应的参数生成系数; Fs=250; Fpass=50; Fstop=70; Apass=0.01; Astop=80;

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/37163.html