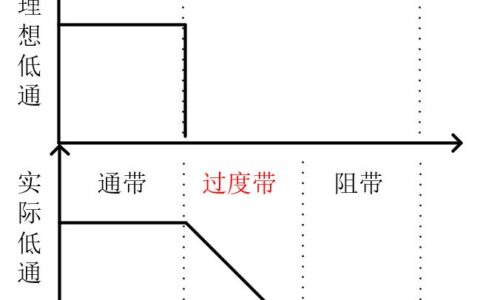

硬件工程师在笔试中容易遇到的题目 名企硬件工程师面试考题大全 一、模拟电路 1、基尔霍夫定理的内容是什么?(仕兰微电子) 2、平板电容公式(C=εS/4πkd)。(未知) 3、最基本的如三极管曲线特性。(未知) 4、描述反馈电路的概念,列举他们的应用。(仕兰微电子) 5、负反馈种类(电压并联反馈,电流串联反馈,电压串联反馈和电流并联反馈);负反 馈的优点(降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非 线性失真,有效地扩展放大器的通频带,自动调节作用)(未知) 6、放大电路的频率补偿的目的是什么,有哪些方法?(仕兰微电子) 7、频率响应,如:怎么才算是稳定的,如何改变频响曲线的几个方法。(未知) 8、给出一个查分运放,如何相位补偿,并画补偿后的波特图。(凹凸) 9、基本放大电路种类(电压放大器,电流放大器,互导放大器和互阻放大器),优缺 点,特别是广泛采用差分结构的原因。(未知) 10、给出一差分电路,告诉其输出电压Y+和Y-,求共模分量和差模分量。(未知) 11、画差放的两个输入管。(凹凸) 12、画出由运放构成加法、减法、微分、积分运算的电路原理图。并画出一个晶体管级的 运放电路。(仕兰微电子) 13、用运算放大器组成一个10倍的放大器。(未知) 14、给出一个简单电路,让你分析输出电压的特性(就是个积分电路),并求输出端某点 的 rise/fall时间。(Infineon笔试试题) 15、电阻R和电容C串联,输入电压为R和C之间的电压,输出电压分别为C上电压和R上电 压,要求制这两种电路输入电压的频谱,判断这两种电路何为高通滤波器,何为低通滤 波器。当RC<<T时,给出输入电压波形图,绘制两种电路的输出波形图。(未知)&NBSP; /> 16、有源滤波器和无源滤波器的原理及区别?(新太硬件) 17、有一时域信号S=V0sin(2pif0t)+V1cos(2pif1t)+V2sin(2pif3t+90),当其通过低通、 带通、高通滤波器后的信号表示方式。(未知) 18、选择电阻时要考虑什么?(东信笔试题) 19、在CMOS电路中,要有一个单管作为开关管精确传递模拟低电平,这个单管你会用P管 还是N管,为什么?(仕兰微电子) 20、给出多个mos管组成的电路求5个点的电压。(Infineon笔试试题) 21、电压源、电流源是集成电路中经常用到的模块,请画出你知道的线路结构,简单描述 其优缺点。(仕兰微电子) 22、画电流偏置的产生电路,并解释。(凹凸) 23、史密斯特电路,求回差电压。(华为面试题) 24、晶体振荡器,好像是给出振荡频率让你求周期(应该是单片机的,12分之一周期….) (华为面试题) 25、LC正弦波振荡器有哪几种三点式振荡电路,分别画出其原理图。(仕兰微电子) 趣味数学和应用数学题 (1)使用下列每组数字,排出加减乘除的公式,得出“24”.第一组“1、2、3、4”;第二组“5、6、7、8”;第三组“3、3、8、8”. (2)10个人排队戴帽子,10个黄帽子,9个蓝帽子,戴好后,后面的人可以看见前面所有人的帽子,然后从后面问起,问自己头上的帽子是什么颜色,结果一直问了9个人都说不知道,而最前面的人却知道自己头上的帽子的颜色.问是什么颜色,为什么? (3)一个班有m名同学,问m为多少时,有两人同一天生日的概率为0.6.建立数学模型并解答.同时说明该模型适用于通信中的那些情况. (4)为了解决学生洗澡难的问题,东方学校新建一座澡堂,水龙头数为m,每天开放k小时,如果学生人数为n,每位学生每周洗一次澡,每次须半小时,学生到达澡堂服从均匀分布,问当m为多少时,学生洗澡等待时间不超过10分钟.建立数学模型并解答.同时请说明该模型适用于通信中的那些情况. (5)有若干台型号相同的联合收割机,收割一片土地上的小麦,若同时投入工作至收割完毕需用24小时;但它们是每隔相同的时间顺序投入工作的,每一台投入工作后都一直工作到小麦收割完毕.如果第一台收割时间是最后一台的5倍,请问:用这种收割方法收割完这片土地上的小麦需用多长时间? (6)有一批货,如果本月初出售,可获利100,然后可将本利都存入银行,已知银行月息为2.4%,如果下月初出售,可获利120,但要付5保管费,试问这批货何时出售最好(本月初还是下月初)?请说明理由. 部分答案: 模拟电路 1、基尔霍夫定理的内容是什么? 基尔霍夫定律包括电流定律和电压定律 电流定律:在集总电路中,任何时刻,对任一节点,所有流出节点的支路电流的代数和恒等于零。 电压定律:在集总电路中,任何时刻,沿任一回路,所有支路电压的代数和恒等于零。 2、描述反馈电路的概念,列举他们的应用。 反馈,就是在电子系统中,把输出回路中的电量输入到输入回路中去。 反馈的类型有:电压串联负反馈、电流串联负反馈、电压并联负反馈、电流并联负反馈。 负反馈的优点:降低放大器的增益灵敏度,改变输入电阻和输出电阻,改善放大器的线性和非线性失真,有效地扩展放大器的通频带,自动调节作用。 电压负反馈的特点:电路的输出电压趋向于维持恒定。 电流负反馈的特点:电路的输出电流趋向于维持恒定。 3、有源滤波器和无源滤波器的区别 无源滤波器:这种电路主要有无源件R、L和C组成 有源滤波器:集成运放和R、C组成,具有不用电感、体积小、重量轻等优点。 集成运放的开环电压增益和输入阻抗均很高,输出电阻小,构成有源滤波电路后还具有一定的电压放大和缓冲作用。但集成运放带宽有限,所以目前的有源滤波电路的工作频率难以做得很高。 数字电路 1、同步电路和异步电路的区别是什么? 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,这有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 2、什么是”线与”逻辑,要实现它,在硬件特性上有什么具体要求? 将两个门电路的输出端并联以实现与逻辑的功能成为线与。 在硬件上,要用OC门来实现,同时在输出端口加一个上拉电阻。 由于不用OC门可能使灌电流过大,而烧坏逻辑门。 3、解释setup和hold time violation,画图说明,并说明解决办法。(威盛VIA2003.11.06上海笔试试题) Setup/hold time是测试芯片对输入信号和时钟信号之间的时间要求。建立时间是指触发器的时钟信号上升沿到来以前,数据稳定不变的时间。输入信号应提前时钟上升沿(如上升沿有效)T时间到达芯片,这个T就是建立时间-Setup time.如不满足setup time,这个数据就不能被这一时钟打入触发器,只有在下一个时钟上升沿,数据才能被打入触发器。 保持时间是指触发器的时钟信号上升沿到来以后,数据稳定不变的时间。如果hold time不够,数据同样不能被打入触发器。 建立时间(Setup Time)和保持时间(Hold time)。建立时间是指在时钟边沿前,数据信号需要保持不变的时间。保持时间是指时钟跳变边沿后数据信号需要保持不变的时间。如果数据信号在时钟沿触发前后持续的时间均超过建立和保持时间,那么超过量就分别被称为建立时间裕量和保持时间裕量。 4、什么是竞争与冒险现象?怎样判断?如何消除?(汉王笔试) 在组合逻辑中,由于门的输入信号通路中经过了不同的延时,导致到达该门的时间不一致叫竞争。 产生毛刺叫冒险。如果布尔式中有相反的信号则可能产生竞争和冒险现象。 解决方法:一是添加布尔式的消去项,二是在芯片外部加电容。 5、名词:SRAM、SSRAM、SDRAM SRAM:静态RAM DRAM:动态RAM SSRAM:Synchronous Static Random Access Memory同步静态随机访问存储器。它的一种类型的SRAM。SSRAM的所有访问都在时钟的上升/下降沿启动。地址、数据输入和其它控制信号均于时钟信号相关。这一点与异步SRAM不同,异步SRAM的访问独立于时钟,数据输入和输出都由地址的变化控制。 SDRAM:Synchronous DRAM同步动态随机存储器 6、FPGA和ASIC的概念,他们的区别。(未知) 答案:FPGA是可编程ASIC。 ASIC:专用集成电路,它是面向专门用途的电路,专门为一个用户设计和制造的。根据一个用户的特定要求,能以低研制成本,短、交货周期供货的全定制,半定制集成电路。与门阵列等其它ASIC(Application Specific IC)相比,它们又具有设计开发周期短、设计制造成本低、开发工具先进、标准产品无需测试、质量稳定以及可实时在线检验等优点。 7、什么叫做OTP片、掩膜片,两者的区别何在? OTP means one time program,一次性编程 MTP means multi time program,多次性编程 OTP(One Time Program)是MCU的一种存储器类型 MCU按其存储器类型可分为MASK(掩模)ROM、OTP(一次性可编程)ROM、FLASHROM等类型。 MASKROM的MCU价格便宜,但程序在出厂时已经固化,适合程序固定不变的应用场合; FALSHROM的MCU程序可以反复擦写,灵活性很强,但价格较高,适合对价格不敏感的应用场合或做开发用途; OTP ROM的MCU价格介于前两者之间,同时又拥有一次性可编程能力,适合既要求一定灵活性,又要求低成本的应用场合,尤其是功能不断翻新、需要迅速量产的电子产品。 8、单片机上电后没有运转,首先要检查什么? 首先应该确认电源电压是否正常。用电压表测量接地引脚跟电源引脚之间的电压,看是否是电源电压,例如常用的5V。 接下来就是检查复位引脚电压是否正常。分别测量按下复位按钮和放开复位按钮的电压值,看是否正确。 然后再检查晶振是否起振了,一般用示波器来看晶振引脚的波形,注意应该使用示波器探头的“X10”档。另一个办法是测量复位状态下的IO口电平,按住复位键不放,然后测量IO口(没接外部上拉的P0口除外)的电压,看是否是高电平,如果不是高电平,则多半是因为晶振没有起振。 另外还要注意的地方是,如果使用片内ROM的话(大部分情况下如此,现在已经很少有用外部扩ROM的了),一定要将EA引脚拉高,否则会出现程序乱跑的情况。有时用仿真器可以,而烧入片子不行,往往是因为EA引脚没拉高的缘故(当然,晶振没起振也是原因只一)。经过上面几点的检查,一般即可排除故障了。如果系统不稳定的话,有时是因为电源滤波不好导致的。在单片机的电源引脚跟地引脚之间接上一个0.1uF的电容会有所改善。如果电源没有滤波电容的话,则需要再接一个更大滤波电容,例如220uF的。遇到系统不稳定时,就可以并上电容试试(越靠近芯片越好)。 10、你知道那些常用逻辑电平?TTL与COMS电平可以直接互连吗?(汉王笔试) 常用逻辑电平:TTL、CMOS、LVTTL、LVCMOS、ECL(Emitter Coupled Logic)、PECL(Pseudo/Positive Emitter Coupled Logic)、LVDS(Low Voltage Differential Signaling)、GTL(Gunning Transceiver Logic)、BTL(Backplane Transceiver Logic)、ETL(enhanced transceiver logic)、GTLP(Gunning Transceiver Logic Plus);RS232、RS422、RS485(12V,5V,3.3V);TTL和CMOS不可以直接互连,由于TTL是在0.3-3.6V之间,而CMOS则是有在12V的有在5V的。CMOS输出接到TTL是可以直接互连。TTL接到CMOS需要在输出端口加一上拉电阻接到5V或者12V。 cmos的高低电平分别为:Vih>=0.7VDD,Vil<=0.3VDD;Voh>=0.9VDD,Vol<=0.1VDD. ttl的为:Vih>=2.0v,Vil<=0.8v;Voh>=2.4v,Vol<=0.4v. 用cmos可直接驱动ttl;加上拉电阻后,ttl可驱动cmos. 1、当TTL电路驱动COMS电路时,如果TTL电路输出的高电平低于COMS电路的最低高电平(一般为3.5V),这时就需要在TTL的输出端接上拉电阻,以提高输出高电平的值。 2、OC门电路必须加上拉电阻,以提高输出的搞电平值。 3、为加大输出引脚的驱动能力,有的单片机管脚上也常使用上拉电阻。 4、在COMS芯片上,为了防止静电造成损坏,不用的管脚不能悬空,一般接上拉电阻产生降低输入阻抗,提供泄荷通路。 5、芯片的管脚加上拉电阻来提高输出电平,从而提高芯片输入信号的噪声容限增强抗干扰能力。 6、提高总线的抗电磁干扰能力。管脚悬空就比较容易接受外界的电磁干扰。 7、长线传输中电阻不匹配容易引起反射波干扰,加上下拉电阻是电阻匹配,有效的抑制反射波干扰。 上拉电阻阻值的选择原则包括: 1、从节约功耗及芯片的灌电流能力考虑应当足够大;电阻大,电流小。 2、从确保足够的驱动电流考虑应当足够小;电阻小,电流大。 3、对于高速电路,过大的上拉电阻可能边沿变平缓。综合考虑 以上三点,通常在1k到10k之间选取。对下拉电阻也有类似道理 //OC门电路必须加上拉电阻,以提高输出的搞电平值。 OC门电路要输出“1”时才需要加上拉电阻 不加根本就没有高电平 在有时我们用OC门作驱动(例如 控制一个 LED)灌电流工作时就可以不加上拉电阻 OC门可以实现“线与”运算 OC门就是 集电极 开路 输出 总之加上拉电阻能够提高驱动能力。 11、如何解决亚稳态。(飞利浦-大唐笔试)? 亚稳态是指触发器无法在某个规定时间段内达到一个可确认的状态。当一个触发器进入亚稳态时,既无法预测该单的输出电平,也无法预测何时输出才能稳定在某个正确的电平上。在这个稳定期间,触发器输出一些中间级电平,或者可能处于振荡状态,并且这种无用的输出电平可以沿信号通道上的各个触发器级联式传播下去。 解决方法: 1 降低系统时钟频率 2 用反应更快的FF 3 引入同步机制,防止亚稳态传播 4 改善时钟质量,用边沿变化快速的时钟信号 关键是器件使用比较好的工艺和时钟周期的裕量要大。亚稳态寄存用d只是一个办法,有时候通过not,buf等都能达到信号过滤的效果 12、IC设计中同步复位与异步复位的区别。(南山之桥) 同步复位在时钟沿采复位信号,完成复位动作。异步复位不管时钟,只要复位信号满足条件,就完成复位动作。异步复位对复位信号要求比较高,不能有毛刺,如果其与时钟关系不确定,也可能出现亚稳态。 13、MOORE 与 MEELEY状态机的特征。(南山之桥) Moore 状态机的输出仅与当前状态值有关, 且只在时钟边沿到来时才会有状态变化. Mealy 状态机的输出不仅与当前状态值有关, 而且与当前输入值有 14、多时域设计中,如何处理信号跨时域。(南山之桥) 不同的时钟域之间信号通信时需要进行同步处理,这样可以防止新时钟域中第一级触发器的亚稳态信号对下级逻辑造成影响,其中对于单个控制信号可以用两级同步器,如电平、边沿检测和脉冲,对多位信号可以用FIFO,双口RAM,握手信号等。 跨时域的信号要经过同步器同步,防止亚稳态传播。例如:时钟域1中的一个信号,要送到时钟域2,那么在这个信号送到时钟域2之前,要先经过时钟域2的同步器同步后,才能进入时钟域2。这个同步器就是两级d触发器,其时钟为时钟域2的时钟。这样做是怕时钟域1中的这个信号,可能不满足时钟域2中触发器的建立保持时间,而产生亚稳态,因为它们之间没有必然关系,是异步的。这样做只能防止亚稳态传播,但不能保证采进来的数据的正确性。所以通常只同步很少位数的信号。比如控制信号,或地址。当同步的是地址时,一般该地址应采用格雷码,因为格雷码每次只变一位,相当于每次只有一个同步器在起作用,这样可以降低出错概率,象异步FIFO的设计中,比较读写地址的大小时,就是用这种方法。如果两个时钟域之间传送大量的数据,可以用异步FIFO来解决问题。 我们可以在跨越Clock Domain 时加上一个低电平使能的Lockup Latch 以确保Timing能正确无误。 华为公司面试题(硬件,笔试题) 一 选择 13个题目,没有全部抄下来,涉及的课程有电路,模拟电路,数字电路,信号与系统,微机原理,网络,数字信号处理有关于1.微分电路2.CISC,RISC3.数据链路层 二 填空 10个题目,没有全部抄下来,涉及的课程有电路,模拟电路,数字电路,信号与系统,微机原理,网络,数字信号处理 有关于1.TIC6000 DSP2.二极管3.RISC4.IIR 三 简答 1.x(t)的傅立叶变换为X(jw)=$(w) $(w-PI) $(w-5) h(t)=u(t)-u(t-2) 问: (1),x(t)是周期的吗? (2),x(t)*h(t)是周期的吗? (3),两个非周期的信号卷积后可周期吗? 2.简述分组交换的特点和不足 四 分析设计 1.波形变换题目 从正弦波->方波->锯齿波->方波,设计电路 2.74161计数器组成计数电路,分析几进制的 3.用D触发器构成2分频电路 4.判断MCS-51单片机的指令正确还是错误,并指出错误原因 (1) MUL R0,R1 (2) MOV A,@R7 (3) MOV A,#3000H (4) MOVC @A DPTR,A (5) LJMP #1000H () 5.MCS-51单片机中,采用12Mhz时钟,定时器T0采用模式1(16位计数器),请问在下面程序中,p1.0的输出频率 MOV TMOD,#01H SETB TR0 LOOP:MOV TH0,#0B1H MOV TL0,#0E0H LOOP1:JNB TF0,LOOP1 CLR TR0 CPL P1.0 SJMP LOOP 迈瑞硬件工程师笔试(北京,2007.11.3) 宣讲会说的三日上午短信、邮件通知,但短信下午两点多才收到,上午收到邮件,好像是半夜3、4点发出的。 原来说的考一个半小时,但是估计题简单,改为一个小时。 考官查证件什么的比较严,霸王考貌似有难度。 1、某存储器地址线长度为行10和列8,每个单位32bit,存储量是 __ Byte。 2、给出描述,判断三极管的工作状态。 3、摩尔定律是什么,对硬件开发有何影响。 4、八位二进制补码表示范围 __ 到 __ 。两个补码表示的数和00001011积是多少 __ (十进制) __ (十六进制) __ (八进制)。 5、一个简单的运放电路(放大倍数为有限值!)的输出。 6、RLC振荡电路,关于电流i(t)的输入方程和输出方程(U=10 V,R=100 Ohm,L=0.1 H,C=1uF,初始状态为0)。 7、英译中:关于嵌入式系统。 8、智力题 有甲乙车站,之间有丙车站,甲乙均每隔10分钟发车一次,但两站发车时间不一定一致。某人下班后去丙站,哪趟车先到坐哪趟。100天中,大 约90天到达甲站,10天到达乙站。问丙站列车时刻表。 9、三选一,可多做 (一)已给出一个系统的对数幅频特性折线图(比较简单), 问: (1)f=1000Hz时,20lg|A|~=?fai=? (2)引入负反馈1(对传输函数影响忽略),是否震荡? (3)保证系统稳定,负反馈最大多少? (二)用FSB(好像是这个)解码什么的。。。 (三)Intel某个芯片的一些问题,三种工作状态,各个状态下的一些操作。。。 后面有个编程题,好像是属于(三),不会做,没有多看。 【开放问题】: 描述你做过的一个项目的结构框图(硬件/软件),简要介绍之,性能要求都有什么,遇到什么问题如何解决的? btw:走的时候发现黑板上写的:可以在最后一页写点建议什么的,说是给迈瑞一次机会,暗含是给答得不好的自己一次机会吧。 (尽量回忆,希望对各位有用) 硬件工程师 1.设计一个4输入的7段LED驱动器,并写出testbench 2.解释什么叫phase noise和jitter,怎样尽量减小jitter 解释什么叫skew,怎样尽量减小skew 3.选作其一 1)解释什么是cpu的实模式,什么是保护模式 2)解释什么是ADC的INL和DNL5a880faf6f©应届生求职网YingJieSheng.COM©c350ade2a4 4.英文作文,你最喜欢什么课?你学到了什么?为什么?200 words以上 模拟工程师 1.比较理想运放和非理想运放的参数放大倍数,输入阻抗,输出阻抗,噪声,带宽 2.比较非理想有反馈运放和非理想无反馈运放的参数放大倍数,输入阻抗,输出阻抗,带宽 3.如果要设计一个正弦波发生器的输出级电路,正弦波峰峰值10V,频率10MHz,负载100欧姆.可能会碰到哪些困难?如何解决? 4.英文作文,比较电子工程和其他如机械工程,生物工程的优势 华为硬件笔试题 2006-09-30 13:01 一 选择 13个题目,没有全部抄下来,涉及的课程有电路,模拟电路,数字电路,信号与系统,微机原理,网络,数字信号处理 有关于 1.微分电路 2.CISC,RISC 3.数据链路层 二 填空 10个题目,没有全部抄下来,涉及的课程有电路,模拟电路,数字电路,信号与系统,微机原理,网络,数字信号处理有关于 1.TIC6000 DSP 2.二极管 3.RISC 4.IIR 三 简答 1.x(t)的傅立叶变换为X(jw)=$(w)+$(w-PI)+$(w-5) h(t)=u(t)-u(t-2) 问: (1),x(t)是周期的吗? (2),x(t)*h(t)是周期的吗? (3),两个非周期的信号卷积后可周期吗? 2.简述分组交换的特点和不足 四 分析设计 1.波形变换题目从正弦波->方波->锯齿波->方波,设计电路 2.74161计数器组成计数电路,分析几进制的 3.用D触发器构成2分频电路 4.判断MCS-51单片机的指令正确还是错误,并指出错误原因 (1) MUL R0,R1 (2) MOV A,@R7 (3) MOV A,#3000H (4) MOVC @A+DPTR,A (5) LJMP #1000H () 5.MCS-51单片机中,采用12Mhz时钟,定时器T0采用模式1(16位计数器),请问在下面程序中,p1.0的输出频率 MOV TMOD,#01H SETB TR0 LOOP:MOV TH0,#0B1H MOV TL0,#0E0H LOOP1:JNB TF0,LOOP1 CLR TR0 CPL P1.0 SJMP LOOP 华为硬件面试题 2006-09-30 13:02 全都是几本模电数电信号单片机题目 1.用与非门等设计全加法器 2.给出两个门电路让你分析异同 3.名词:sram,ssram,sdram (SRAM是静态随机存储器,DRAM是动态随机存储器!SDRAM是同步动态随机存储器,SSRAM就是同步静态随机存储器!) 4.信号与系统:在时域与频域关系 5.信号与系统:和4题差不多 6.晶体振荡器,好像是给出振荡频率让你求周期(应该是单片机的,12分之一周期.. ..) 7.串行通信与同步通信异同,特点,比较 8.RS232c高电平脉冲对应的TTL逻辑是?(负逻辑?) 9.延时问题,判错 10.史密斯特电路,求回差电压 11.VCO是什么,什么参数(压控振荡器?) 12. 用D触发器做个二分颦的电路.又问什么是状态图 13. 什么耐奎斯特定律,怎么由模拟信号转为数字信号 14. 用D触发器做个4进制的计数 15.那种排序方法最快? 华为C语言 1、局部变量能否和全局变量重名? 答:能,局部会屏蔽全局。要用全局变量,需要使用”::” 局部变量可以与全局变量同名,在函数内引用这个变量时,会用到同名的局部变量,而不会用到全局变量。对于有些编译器而言,在同一个函数内可以定义多个同名的局部变量,比如在两个循环体内都定义一个同名的局部变量,而那个局部变量的作用域就在那个循环体内。 2、如何引用一个已经定义过的全局变量? 答:extern 可以用引用头文件的方式,也可以用extern关键字,如果用引用头文件方式来引用某个在头文件中声明的全局变理,假定你将那个变写错了,那么在编译期间会报错,如果你用extern方式引用时,假定你犯了同样的错误,那么在编译期间不会报错,而在连接期间报错。 3、全局变量可不可以定义在可被多个.C文件包含的头文件中?为什么? 答:可以,在不同的C文件中以static形式来声明同名全局变量。 可以在不同的C文件中声明同名的全局变量,前提是其中只能有一个C文件中对此变量赋初值,此时连接不会出错 4、语句for( ;1 ;)有什么问题?它是什么意思? 答:和while(1)相同。 5、do……while和while……do有什么区别? 答:前一个循环一遍再判断,后一个判断以后再循环 6、请写出下列代码的输出内容 以下是引用片段: #include main() { int a,b,c,d; a=10; b=a++; c=++a; d=10*a++; printf(“b,c,d:%d,%d,%d”,b,c,d); return 0; } 答:10,12,120 7、static全局变量与普通的全局变量有什么区别?static局部变量和普通局部变量有什么区别?static函数与普通函数有什么区别? 全局变量(外部变量)的说明之前再冠以static 就构成了静态的全局变量。全局变量本身就是静态存储方式, 静态全局变量当然也是静态存储方式。这两者在存储方式上并无不同。这两者的区别虽在于非静态全局变量的作用域是整个源程序,当一个源程序由多个源文件组成时,非静态的全局变量在各个源文件中都是有效的。而静态全局变量则限制了其作用域,即只在定义该变量的源文件内有效,在同一源程序的其它源文件中不能使用它。由于静态全局变量的作用域局限于一个源文件内,只能为该源文件内的函数公用,因此可以避免在其它源文件中引起错误。 从以上分析可以看出,把局部变量改变为静态变量后是改变了它的存储方式即改变了它的生存期。把全局变量改变为静态变量后是改变了它的作用域,限制了它的使用范围。 static函数与普通函数作用域不同。仅在本文件。只在当前源文件中使用的函数应该说明为内部函数(static),内部函数应该在当前源文件中说明和定义。对于可在当前源文件以外使用的函数,应该在一个头文件中说明,要使用这些函数的源文件要包含这个头文件 static全局变量与普通的全局变量有什么区别:static全局变量只初使化一次,防止在其他文件单中被引用; static局部变量和普通局部变量有什么区别:static局部变量只被初始化一次,下一次依据上一次结果值; static函数与普通函数有什么区别:static函数在内存中只有一份,普通函数在每个被调用中维持一份拷贝 8、程序的局部变量存在于(堆栈)中,全局变量存在于(静态区 )中,动态申请数据存在于( 堆)中。 9、设有以下说明和定义: typedef union {long i; int k[5]; char c;} DATE; struct data { int cat; DATE cow; double dog;} too; DATE max; 则语句 printf(“%d”,sizeof(struct date)+sizeof(max));的执行结果是:___52____ 答:DATE是一个union, 变量公用空间. 里面最大的变量类型是int[5], 占用20个字节. 所以它的大小是20 data是一个struct, 每个变量分开占用空间. 依次为int4 + DATE20 + double8 = 32. 所以结果是 20 + 32 = 52. 当然…在某些16位编辑器下, int可能是2字节,那么结果是 int2 + DATE10 + double8 = 20 10、队列和栈有什么区别? 队列先进先出,栈后进先出 。。。后面还有更精彩的内容 一步一步的看下来,发现这些题目都很变态,对C语言的初学者来说能答出几题就非常意外了。但是以华为选拔人才的标准来看,去参加应聘的人就应该把自己放在一个高水平的起点,能答出这些题目说明已经对C语言有非常深入的理解了,除非是像我一样已经看过这些题目的答案了=*_*= 全部看完之后对于自身也是一个提高,里面有一些自己已经知道的,有一些比较模糊的看过答案后比以前更清楚了,还有一些以前不知道的看了也是一个补充,总之收获颇丰。真正能够把C语言的语法掌握透彻就看对这些题的理解了,但这只是C语言的基础,凭这些在C语言编程上面基本上不会犯什么语法错误了。还有更深入的东西是需要自己去不断钻研的

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/36821.html