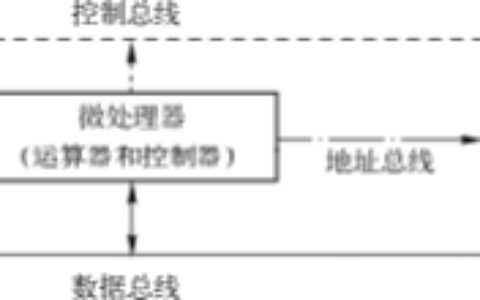

计算机体系结构(第五版)系列-第一章:量化设计与分析基础 要想做好CPU相关的性能优化,这本书不得不读,因此让我们开启计算机体系结构课程之旅。 一、引言 20世纪80年代,开发了一组指令更为简单的新体系结构-RISC(精简指令集计算机)体系结构。 设计人员在设计时,主要投入在2中关键的性能技术上:指令集并行的开发(流水线到多指令发射)和缓存的使用(简单形式到更为复杂的组织和优化方式) 20世纪90年代,晶体管数目的飞速增长,在低端应用中,比如手机,由于X86转换开销所带来的功耗和硅面成本,促使RISC体系结构称为主流,这就是ARM。 20世纪的这一飞速发展,共有4重效果: 1、它显著增强了可供计算机用户使用的功能, 对许多应用来说,当今性能最高的微处理器比不到10年前的超级计算机还要优秀。 2、性价比的这种大幅提高导致了新型计算机的出现, 个人计算机、工作中、智能手机、平板电脑。 3、根据摩尔定律的预测,半导体制造业的持续发展已经使基于微处理器的计算机在整个计算机设计领域中占据了主导地位, 逻辑电路或门整列制造 到 微处理器 的发展 4、硬件复兴的第4重影响,是对软件开发的影响 开发语言的丰富,软件部署的变化(SaaS),应用程序本质的变化(功能和体系形式) 2003年开始,由于风冷芯片最大功耗和无法有效地开发更多指令级并行这2大孪生瓶颈,单处理器的性能提高速度下降到每年不足22%。Intel在2004年取消了高性能单核处理器项目,转而提高一个芯片上集成的核心数目。 里程碑的信号:单纯依赖指令级并行(ILP)转向数据级并行(DLP)和线程级并行(TLP) 二、计算机分类

![计算机组成与设计第五版ch03_计算机组成原理唐朔飞第二版答案插图77 几何平均=\sqrt[n]{\prod_{i=1}^{n}样本_{i}}](https://sigusoft.com/wp-content/themes/justnews/themer/assets/images/lazy.png)

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/29748.html