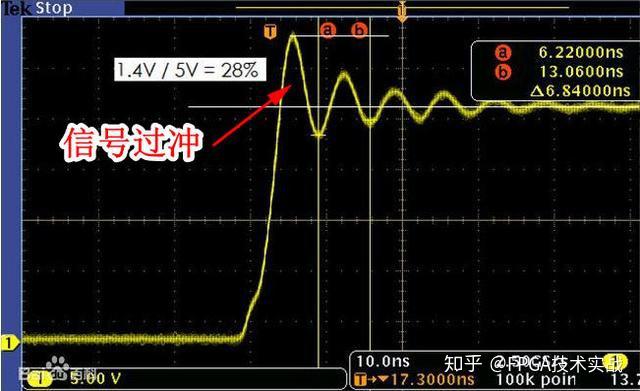

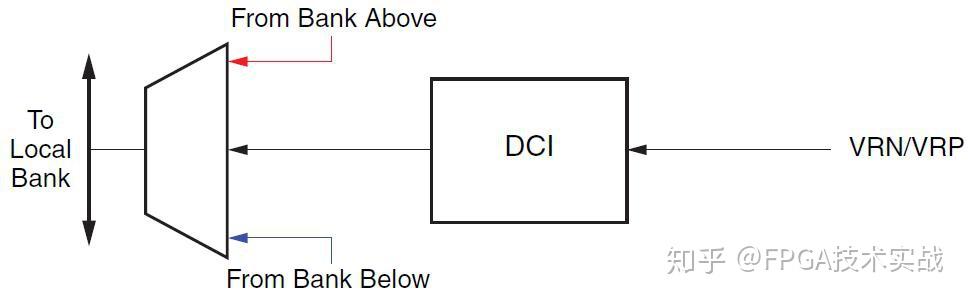

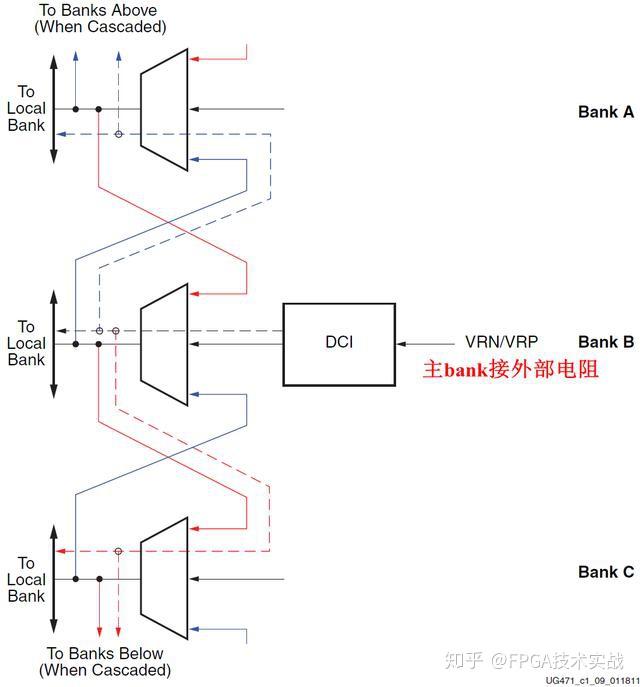

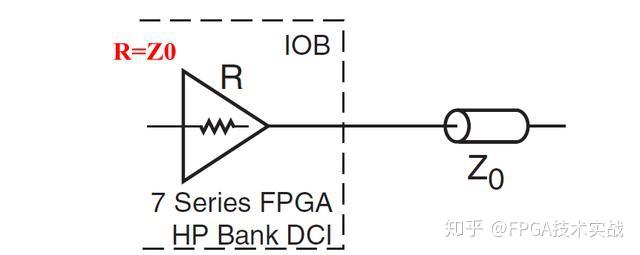

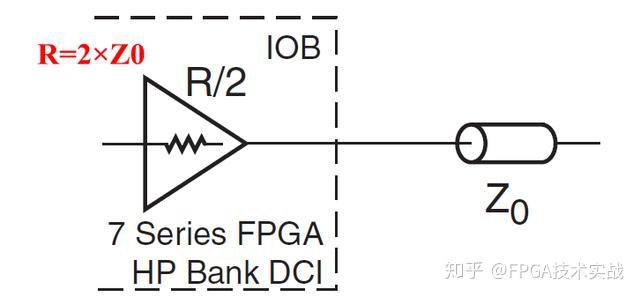

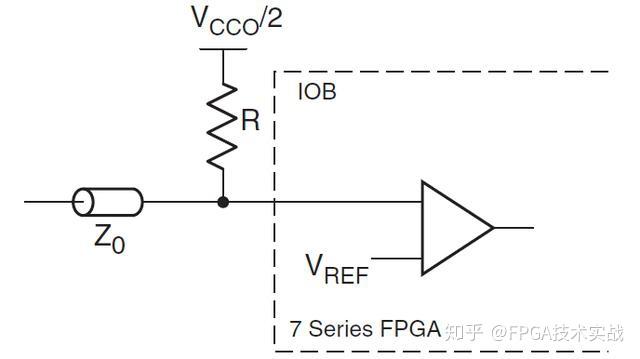

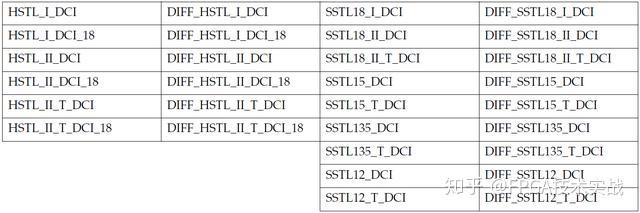

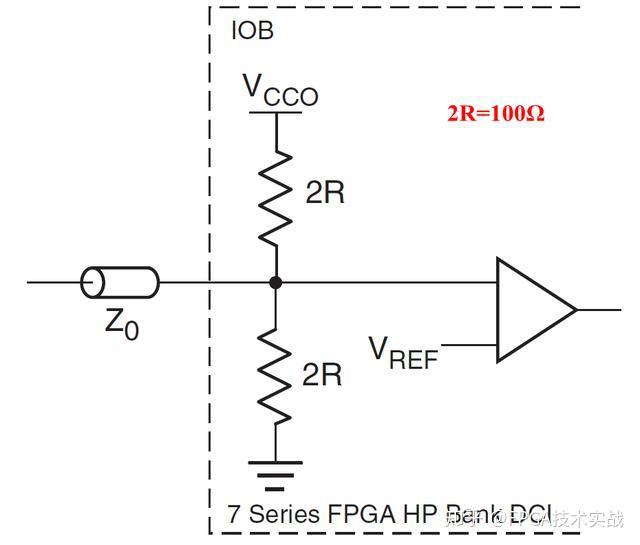

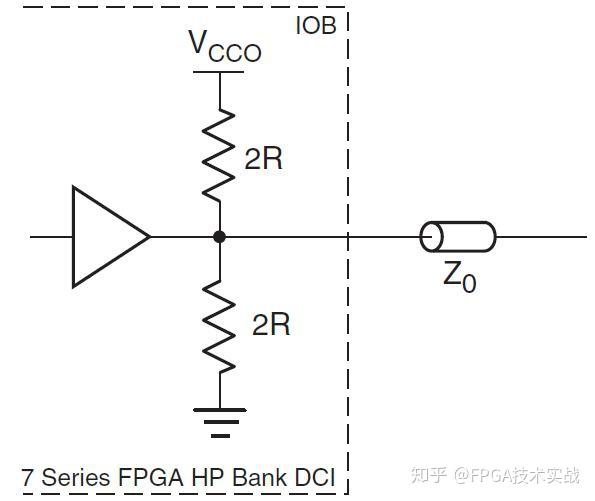

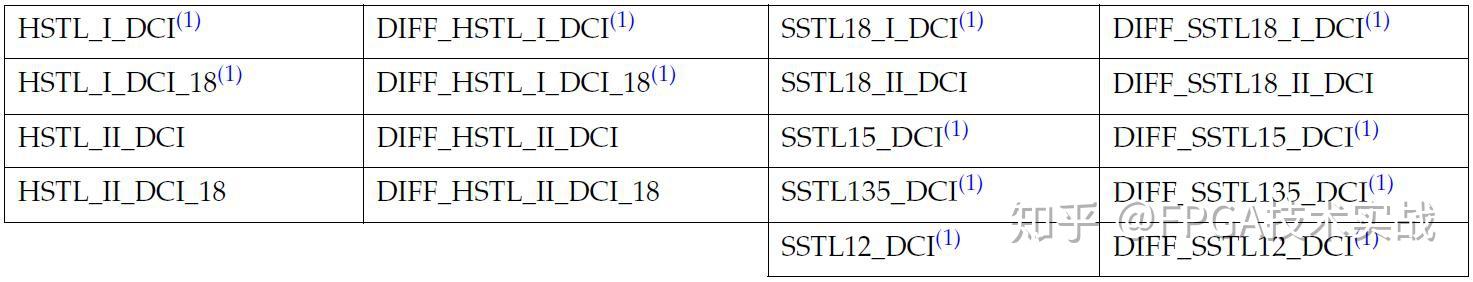

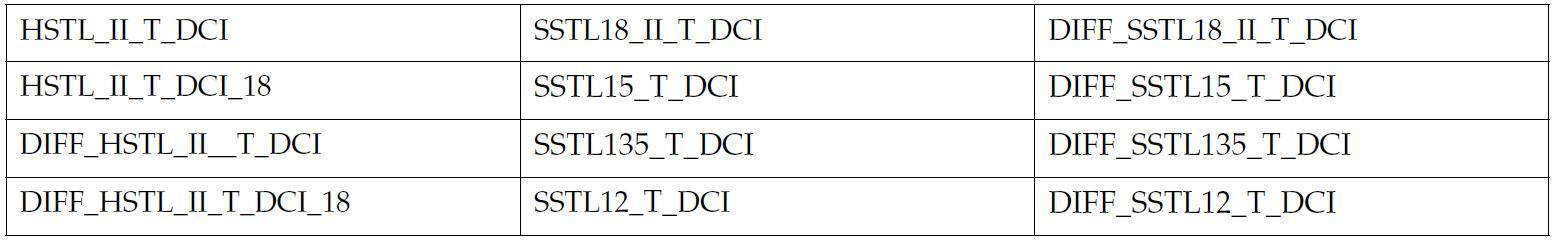

Xilinx 7系列SelectIO结构之DCI(动态可控阻抗)技术(一) 引言:随着FPGA容量越来越大,系统时钟速度越来越快,PC电路板设计和制造更加困难。随着更快的信号边沿速率,保持信号完整性成为关键问题。PC电路板必须恰当的端接避免反射和振铃。本节我们介绍Xilinx器件DCI技术,包括以下内容:DCI技术概述DCI级联技术DCI端接方式 1.DCI技术概述

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/26437.html