计算机组成(超详细)+附带思维导图 计算机的组成 运算器,进行运算,算术运算和逻辑运算控制器,控制指令的执行存储器,包括内存和外存,外存有硬盘,u盘等形式输入设备,鼠标,键盘等输出设备,比如显示器 运算器和控制器组成中央处理单cpu,但是cpu的范围更大一下,还包括一些寄存器,总线等 运算器中比较重要的寄存器 算术逻辑单ALU 负责进行算术运算和逻辑运算累加寄存器AC 存储源操作数,比如一个数加另一个数,在累加计算器中存储一个加数,算术逻辑单中也只能存储一个加数,运算完成得到的结果没有别的地方存储,会重新存在累加寄存器中,当做源操作数数据缓冲寄存器DR 暂时存储数据和指令状态条件寄存器PSW 存储条件码,比如溢出状态,除数为0等不只有上述几个寄存器,只是上面几个比较重要 控制器中比较重要的寄存器 指令寄存器IR 暂时存储要执行的指令程序计数器PC 很重要,存储指令执行的地址,要根据这个地址取出指令,然后执行地址寄存器AR 保存当前程序正在访问的地址指令译码器ID 分析指令操作码,将指令编译成可执行的内容不只有上述几个寄存器,只是上面几个比较重要 指令和数据都存储在地址中,怎么判断取出的是指令还是数据呢? 根据指令的执行周期来判断取出的是指令还是数据指令的执行周期是先取出指令,然后分析指令操作码,之后再执行指令,执行指令的时候才会去取数据所以一开始取得是指令,在指令执行的时候取得是数据 一些寄存器的英文缩写 PC程序计数器,控制器AR地址寄存器,控制器DR数据缓冲寄存器,运算器ID指令译码器,控制器PSW状态条件寄存器,运算器IR指令寄存器,控制器ALU算术逻辑单,运算器AC累加寄存器,运算器 奇偶校验码 相关概念 码距 对于单个编码来说,要变成另一个编码只需要改变一位,所以码距为1,比如00改变一位就可以变成01或10对于两个编码来说,A编码要变成B编码需要改变的位数,其实就是A编码和B编码有几位数不一样,比如00到11的码距就是2对于校验来说,码距越大就越利于检错和纠错。因为码距越大,A编码就越不容易变成B编码 奇偶校验 奇偶校验就是在原本的编码最后面加一位校验码(注意只加一位),使得编码中1的个数为奇数(奇校验)或偶数(偶校验),这样码距就变成了2,也就是在传输一个编码时,这个编码最少变两个数,才会在接收的时候被当做正确数据接收。其实如果变得数多于两位,也必须是偶数个,才会被当做正确数据接收。 例子

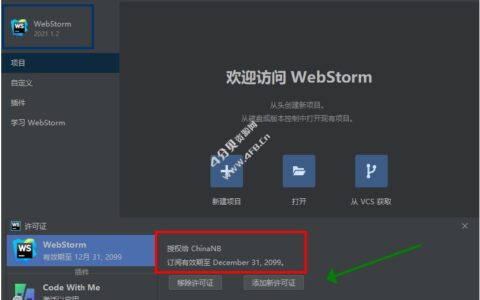

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/23322.html