目录

芯片简介:

功能配置设计

高速DAC软件驱动设计

芯片简介:

AD9122 是一款双通道16位高性能数模转换器(DAC),在800MSPS工作条件下其无杂散动态范围(SFDR)高达72dBc,最高可提供1200 MSPS采样速率。

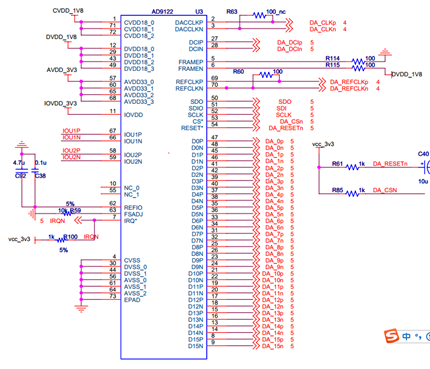

高速DAC–AD9122电路原理图

硬件设计的电路原理图如上图所示,AD9122具备针对直接变频传输应用进行优化的特性,包括复数数字调制以及增益与失调补偿。DAC输出经过优化后可直接与模拟正交调制器无缝接口,便于后期使用多载波调制技术。

高速AD9122实现数模转换功能经过其内部功能模块转换包括:预调制;NCO正交调制;HB1、HB2、HB3半带插值滤波器、反sinc滤波器。其中内部的各个模块通过SPI可程序控制,在应用中根据输出需求配置相应寄存器值可实现多种模式的调制信号输出。

功能配置设计

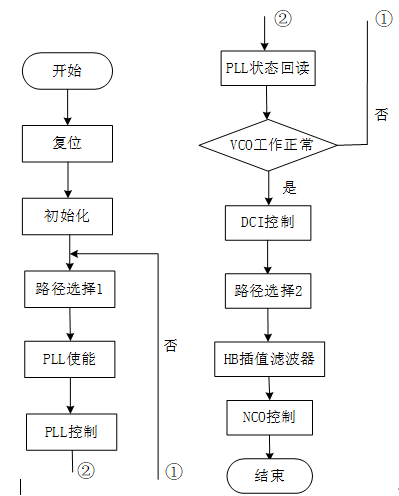

AD9122芯片其内部强大的功能均是通过对内部功能寄存器的配置实现的,在后期维护与功能扩展时,只需设置对应寄存器就可实现预期功能,方便实现软件定义通信功能。根据芯片手册说明,如下图所示为芯片功能配置流程图。

AD9122功能配置流程图

高速DAC软件驱动设计

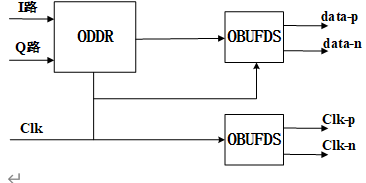

AD9122和Zynq中PL侧并行数据通过LVDS端口传输,用以接收I、Q两路发射路径的数据。DAC芯片支持接受字、字节和半字节三种格式数据。本设计中使用字节模式传输数字信号。字节模式下时钟信号的上升沿发送16位I路数据、下降沿发送Q路16位数据。其逻辑代码实现框图如图所示:

DAC逻辑代码实现框图

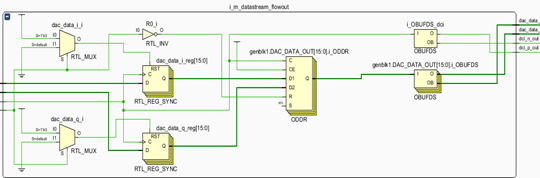

AD9122逻辑代码主要包括ODDR和OBUFDS两部分:

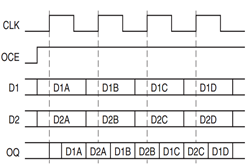

(1)ODDR:Xilinx 7系列器件OLOGIC中专用于实现输出DDR的原语,ODDR原语支持OPPOSITE_EDGE模式和SAME_EDGE模式。本文中使用SAME_EDGE模式,其工作时序图如下图所示。

ODDR SAME_EDGE模式时序图

(2)OBUFDS:是一个输出缓冲器,实现数据LVDS接口模式输出。

在完成输出功能配置后需要对输出DCI时钟信号的延时进行调整,以使DCI时钟信号与16位数字信号到达器件时间保持一致,防止出现输出信号毛刺。

下图所示为Vivado开发软件中AD9122 RTL实现框图。

AD9122 RTL实现框图

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/168700.html