计算机组成原理第四章课后习题及答案-唐朔飞(完整版) 第4章 存储器 1. 解释概念:主存、辅存、Cache、RAM、SRAM、DRAM、ROM、PROM、EPROM、EEPROM、CDROM、Flash Memory。 答:主存:主存储器,用于存放正在执行的程序和数据。CPU可以直接进行随机读写,访问速度较高。 辅存:辅助存储器,用于存放当前暂不执行的程序和数据,以及一些需要永久保存的信息。 Cache:高速缓冲存储器,介于CPU和主存之间,用于解决CPU和主存之间速度不匹配问题。 RAM:半导体随机存取存储器,主要用作计算机中的主存。 SRAM:静态半导体随机存取存储器。 DRAM:动态半导体随机存取存储器。 ROM:掩膜式半导体只读存储器。由芯片制造商在制造时写入内容,以后只能读出而不能写入。 PROM:可编程只读存储器,由用户根据需要确定写入内容,只能写入一次。 EPROM:紫外线擦写可编程只读存储器。需要修改内容时,现将其全部内容擦除,然后再编程。擦除依靠紫外线使浮动栅极上的电荷泄露而实现。 EEPROM:电擦写可编程只读存储器。 CDROM:只读型光盘。 Flash Memory:闪速存储器。或称快擦型存储器。 2. 计算机中哪些部件可以用于存储信息?按速度、容量和价格/位排序说明。 答:计算机中寄存器、Cache、主存、硬盘可以用于存储信息。 按速度由高至低排序为:寄存器、Cache、主存、硬盘; 按容量由小至大排序为:寄存器、Cache、主存、硬盘; 按价格/位由高至低排序为:寄存器、Cache、主存、硬盘。 3. 存储器的层次结构主要体现在什么地方?为什么要分这些层次?计算机如何管理这些层次? 答:存储器的层次结构主要体现在Cache-主存和主存-辅存这两个存储层次上。 Cache-主存层次在存储系统中主要对CPU访存起加速作用,即从整体运行的效果分析,CPU访存速度加快,接近于Cache的速度,而寻址空间和位价却接近于主存。 主存-辅存层次在存储系统中主要起扩容作用,即从程序员的角度看,他所使用的存储器其容量和位价接近于辅存,而速度接近于主存。 综合上述两个存储层次的作用,从整个存储系统来看,就达到了速度快、容量大、位价低的优化效果。 主存与CACHE之间的信息调度功能全部由硬件自动完成。而主存与辅存层次的调度目前广泛采用虚拟存储技术实现,即将主存与辅存的一部分通过软硬结合的技术组成虚拟存储器,程序员可使用这个比主存实际空间(物理地址空间)大得多的虚拟地址空间(逻辑地址空间)编程,当程序运行时,再由软、硬件自动配合完成虚拟地址空间与主存实际物理空间的转换。因此,这两个层次上的调度或转换操作对于程序员来说都是透明的。 4. 说明存取周期和存取时间的区别。 解:存取周期和存取时间的主要区别是:存取时间仅为完成一次操作的时间,而存取周期不仅包含操作时间,还包含操作后线路的恢复时间。即: 存取周期 = 存取时间 + 恢复时间 5. 什么是存储器的带宽?若存储器的数据总线宽度为32位,存取周期为200ns,则存储器的带宽是多少? 解:存储器的带宽指单位时间内从存储器进出信息的最大数量。 存储器带宽 = 1/200ns ×32位 = 160M位/秒 = 20MB/秒 = 5M字/秒 注意:字长32位,不是16位。(注:1ns=10-9s) 6. 某机字长为32位,其存储容量是64KB,按字编址它的寻址范围是多少?若主存以字节编址,试画出主存字地址和字节地址的分配情况。 解:存储容量是64KB时,按字节编址的寻址范围就是64K, 如按字编址,其寻址范围为:64K / (32/8)= 16K 主存字地址和字节地址的分配情况:如图 7. 一个容量为16K×32位的存储器,其地址线和数据线的总和是多少?当选用下列不同规格的存储芯片时,各需要多少片? 1K×4位,2K×8位,4K×4位,16K×1位,4K×8位,8K×8位 解:地址线和数据线的总和 = 14 + 32 = 46根; 选择不同的芯片时,各需要的片数为: 1K×4:(16K×32) / (1K×4) = 16×8 = 128片 2K×8:(16K×32) / (2K×8) = 8×4 = 32片 4K×4:(16K×32) / (4K×4) = 4×8 = 32片 16K×1:(16K×32)/ (16K×1) = 1×32 = 32片 4K×8:(16K×32)/ (4K×8) = 4×4 = 16片 8K×8:(16K×32) / (8K×8) = 2×4 = 8片 8. 试比较静态RAM和动态RAM。 答:略。(参看课件) 9. 什么叫刷新?为什么要刷新?说明刷新有几种方法。 解:刷新:对DRAM定期进行的全部重写过程; 刷新原因:因电容泄漏而引起的DRAM所存信息的衰减需要及时补充,因此安排了定期刷新操作; 常用的刷新方法有三种:集中式、分散式、异步式。 集中式:在最大刷新间隔时间内,集中安排一段时间进行刷新,存在CPU访存死时间。 分散式:在每个读/写周期之后插入一个刷新周期,无CPU访存死时间。 异步式:是集中式和分散式的折衷。 10. 半导体存储器芯片的译码驱动方式有几种? 解:半导体存储器芯片的译码驱动方式有两种:线选法和重合法。 线选法:地址译码信号只选中同一个字的所有位,结构简单,费器材; 重合法:地址分行、列两部分译码,行、列译码线的交叉点即为所选单。这种方法通过行、列译码信号的重合来选址,也称矩阵译码。可大大节省器材用量,是最常用的译码驱动方式。 11. 一个8K×8位的动态RAM芯片,其内部结构排列成256×256形式,存取周期为0.1μs。试问采用集中刷新、分散刷新和异步刷新三种方式的刷新间隔各为多少? 解:采用分散刷新方式刷新间隔为:2ms,其中刷新死时间为:256×0.1μs=25.6μs 采用分散刷新方式刷新间隔为:256×(0.1μs+×0.1μs)=51.2μs 采用异步刷新方式刷新间隔为:2ms 12. 画出用1024×4位的存储芯片组成一个容量为64K×8位的存储器逻辑框图。要求将64K分成4个页面,每个页面分16组,指出共需多少片存储芯片。 解:设采用SRAM芯片,则: 总片数 = (64K×8位) / (1024×4位)= 64×2 = 128片 题意分析:本题设计的存储器结构上分为总体、页面、组三级,因此画图时也应分三级画。首先应确定各级的容量: 页面容量 = 总容量 / 页面数 = 64K×8 / 4 = 16K×8位,4片16K×8字串联成64K×8位 组容量 = 页面容量 / 组数 = 16K×8位 / 16 = 1K×8位,16片1K×8位字串联成16K×8位 组内片数 = 组容量 / 片容量 = 1K×8位 / 1K×4位 = 2片,两片1K×4位芯片位并联成1K×8位 存储器逻辑框图:(略)。 13. 设有一个64K×8位的RAM芯片,试问该芯片共有多少个基本单电路(简称存储基)?欲设计一种具有上述同

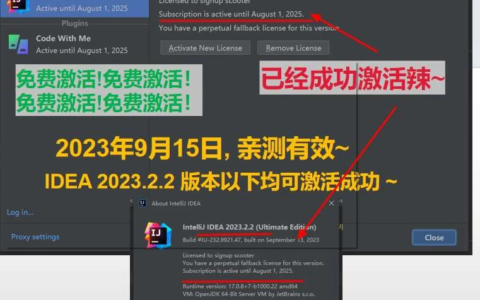

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/86811.html