时钟同步方法:多片FPGA原型验证系统 上方蓝字我们

SoC设计是一个整体的芯片设计,最终整个设计将在统一到一块硅片上完成整个芯片,但是,原型验证中,这个SoC的设计要分布在多个FPGA芯片上,因此整体的设计连续性会受到影响。将我们的RTL设计分别映射到多个FPGA芯片上有三个特别的方面,我们需要特别。时钟、复位和启动条件。为了尽可能实现FPGA原型平台和最终SoC之间的完全保真度,时钟、重置和启动应表现为FPGA之间的硬边界不存在。

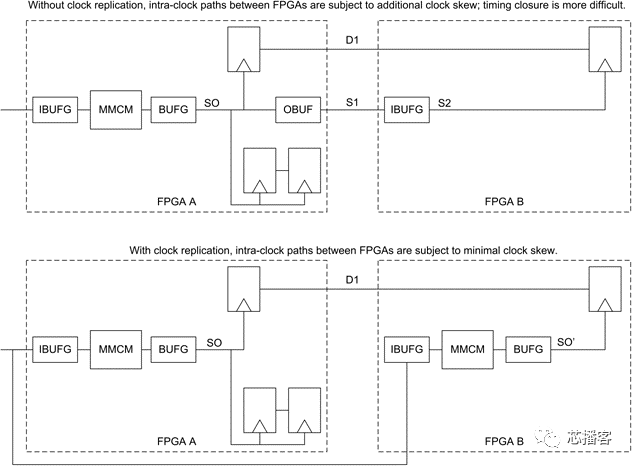

这篇文章,我们来看一下多片FPGA原型验证系统的时钟同步。先从多片FPGA原型平台上综合时钟网络时会存在的两个潜在问题说起: 时钟偏移和时钟不确定性:一种常见的设计方法是使用FPGA硬件板上的PLL来生成所需的时钟,并将其作为主要输入分配给每个FPGA。由于到达FPGA所采用的路径不同,板载PCB轨迹线和缓冲器可能会在相关时钟之间引入一些不确定性和时钟偏移。如果忽略,这种偏移可能会在这些相关时钟之间的短路径上导致保持时间违例。后端布局布线工具通常可以解决FPGA内的保持时间违例,但目前无法导入从综合之前引入的时钟偏斜和不确定性信息。为了解决这个问题,FPGA拥有PLL(通常是FPGA中MCMM的一部分)可以与板的PLL结合使用或代替板的PLL。后端工具了解MCMM的偏斜和不确定性,并可以在布局过程中解决这些问题。然而,分布式MCMM的使用可能会带来上述第二个潜在问题。 时钟同步:当在每个FPGA上本地重新生成相关时钟时,存在一个潜在的时钟同步问题,该问题确实会影响原始SoC设计,其中时钟是从公共源生成和不受信任的。当一个N分频时钟的多个拷贝来自一个基本时钟,但由于复位或初始启动条件以及刚好不走运遇到硬件故障,它们就不同步。 经过分割设计的时钟网络分布在相应的FPGA以及板上的其他时钟组件上。通过成功的时钟门转换,可以使跨越所有FPGA的大量不同时钟变得更容易,从而减少时钟的数量和复杂性。然而,仍有许多时钟驱动器需要在多个FPGA中复制。重要的是,这些复制时钟保持同步,并且在主时钟的正确边缘上生成任何分频时钟。这取决于每个FPGA在同一时钟边缘上的复位应用。因此,有一种通用的FPGA之间的时钟分布,如图所示,

点个在看你最好看

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/81559.html