Altera系列FPGA芯片IP核学习 一直以来,关于IP核感觉比较陌生,对此通过5W1H原则简单总结下: Why(原因)?——为什么会出现IP核? 在FPGA 开发中,通过使用IP核替代用户自己设计的逻辑。 可以大大缩短开发周期,提高更加有效的逻辑综合和实现。 What(目的)?——使用IP核的目的? 在FPGA 开发中通过使用IP核替代用户自己设计的逻辑,可以大大缩短开发周期,提高更加有效的逻辑综合和实现。使用高度优化的IP核有助于加速开发进程,降低开发成本。 When(时间)?——什么时间内使用? 规模化高速FPGA产品开发过程中使用. Where(地点)?——在什么地点使用? 对于想快速实现产品验证并上市,且目前不需要自研芯片的公司使用。 Who(谁)?——谁来使用? 高速FPGA产品开发人员使用。 How(方法)?——怎么使用IP核? 仅本人当前了解,使用Altera系列FPGA芯片的对象使用Quartus 软件调用IP核,或者Xilinx系列FPGA芯片的对象使用Vivado 软件调用IP核。 Altera系列FPGA的IP核既包括诸如逻辑和算数运算等简答的IP核,也包括诸如数字信号处理器、以太网MAC、PCI/PCI Express接口等比较复杂的系统构造模块,按功能划分为以下几类: (1) 逻辑运算IP核。 包括与、或、非、异或、等基本逻辑运算单和复用器、循环移位器、三态缓存器和解码器等相对复杂的逻辑运算模块。 (2)数学运算IP核 1)整数运算IP核 包括LPM库(参数化模型IP库) 提供的IP核和Altera 指定功能的IP核,LPM库中的IP核有加/减法器、乘法器、除法器,比较器,计数器和绝对自计算器;Altera 指定功能的IP核包括累加器,ECC编码器/解码器、乘法器,基于存储的常系数乘法器、乘累加器、乘加器、复数乘法器和整数平方根计算器等。 2)浮点运算IP核 包括浮点加/减法器,浮点乘法器,浮点除法器,浮点数平方根计算器、浮点指数计算器、福覅倒数计算器,浮点数平方根倒数计算器,浮点数自然对数计算器,浮点数正弦/余弦计算器和反正切计数器,浮点数矩阵求逆和乘法器以及浮点数绝对值计算器、比较器和转换器等。 (3)存储器类IP核 包括移位寄存器、触发器、锁存器等简单的存储器IP核和较为复杂的ROM、RAM、FIFO、和flash 存储器模块,另外,Altera 还提供了包括RAM初始化器和针对部分FPGA系列应用的FIFO分割器等辅助存储器设计IP核。 (4)数字信号处理IP核 包括有限冲激响应滤波器(FIR)编译器,级联积分梳状(CIC)滤波器编译器,数控振荡器(NCO)编译器以及快速傅里叶变换(FET)等IP核,用于数字信号系统设计。 (5)数字通信IP核 RS码编译器, 用于卷积码译码的Viterbi 译码器,循环冗余校验(CRC)编译器,8B/10B 编/译码器 以及SONET/SDH 物理层IP核等。 (6)图像处理IP核 主要是实现视频和图像处理系统中常用功能的IP核,具体有2D FIR滤波器和2D中值滤波器,a混合器,视频监视器,色度重采样器,图像剪裁器,视频输入和输出模块,颜色面板序列器,颜色空间转换器,同步器,视频帧读取和缓存器,r校正器,隔行扫描和去隔行扫描器,缩放器,切换器,测试模板生成器和视频跟踪模块。 (7)输入/输出IP核 主要包括时钟控制器,锁相环(PLL)、低电压查分信号(LVDS)收发器,双数据速率(DDR) I/O,访问外部存储器的DQ-DQS I/O、I/O缓存器等。 (8) 芯片接口IP核 用于数字视频广播(DVB)的异步串行接口(ASI),10/100/1000 Mbps以太网接口,DDR和DDR2 SDRAM 控制器,存储器物理层访问接口,PCI/PCI Express 编译器,Rapid IO和利用数字电视信号传输的串行数字接口(SDI)等。 (9)芯片调试IP核 包括提供设计调试功的SignalTap 逻辑分析仪,串行和并行Flash 加载器,系统内的源和探测模块以及虚拟Jtag等。 (10)其他IP核 比如针对Altera系列FPGA应用的专用IP核

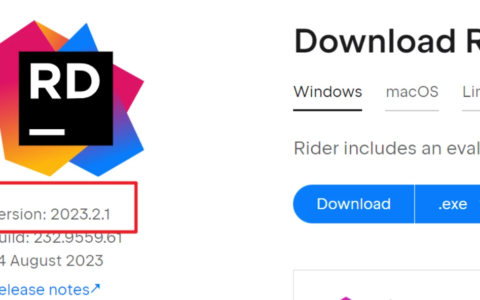

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/75143.html