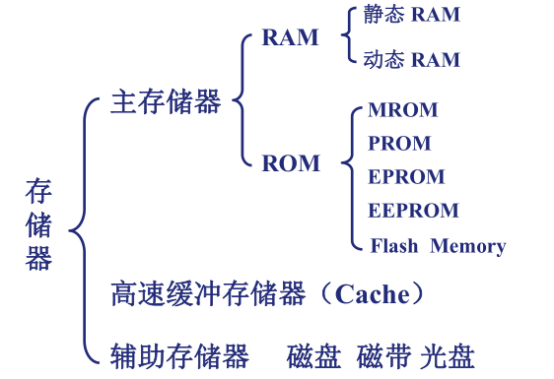

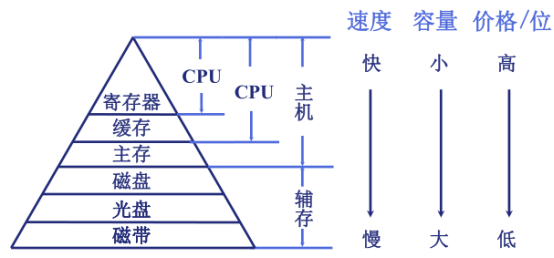

计算机组成原理(第四章(1)) 第四章 存储器 存储器的层次结构 1)存储器的分类 2)存储器的层次化结构 3)半导体随机存取存储器 1.SRAM存储器的工作原理 2.DRAM存储器的工作原理 4)只读存储器 5)主存储器与CPU的连接 6)双口RAM和多模块存储器 7)高速缓存存储器(Cache) 1.程序访问的局部性原理 2.Cache的基本工作原理 3.cache和主存之间的映射方式 4.Cache中主存块的替换算法 5Cache写策略 8)虚拟存储器 1.虚拟存储器的基本概念 2.页式虚拟存储器 3.段式虚拟存储器 4.段页式虚拟存储器 5.TLB(快表) 基本术语: 记忆单(存储基、存储,位)(cell) 具有两种稳态的能够表示二进制数码0和1的物理器件 存储单(编制单位) 主存中具有相同地址的位构成一个存储单,也称为一个编制单 存储体(存储矩阵,存储阵列) 所有存储单构成的一个存储阵列 编址方式 字节编址、按字编址 存储器地址寄存器(MAR) 用于存放主存单地址的寄存器 存储器数据寄存器(MDR) 用于存放主存单中数据的寄存器 存储器的分类: 1.按存储介质分类 1)半导体存储器 ——》易失的 2)磁表面存储器 磁盘、磁带 3)磁芯存储器 硬磁材料、环状件 4)光盘存储器 激光、磁光材料 ——》非易失的 2.存取方式分类 1)存取时间与物理地址无关(随机访问) 每个单读写时间一样,且与各单所在位置无关(如内存) 随机存储器RAM 在程序的执行过程中可读可写 静态RAM:触发器原理寄存信息 动态RAM:电容充放电原理寄存信息 只读存储器ROM 掩模型ROM:一旦制成无法更改 可编程ROM:可编程一次 可擦除可编程ROM:可擦除、编程多次 电可擦除编程ROM:可(局部)擦除,编程多次 闪存或快擦型存储器Flash Memory:比EEPROM快得多 2)存取时间与物理地址有关(串行访问) 顺序存取存储器 数据按顺序从存储载体的始端寻找,然后进行读出或写入,因而存取时间的长短与信息所在位置有关。(如磁带) 直接存取存储器 直接定位到要读写的数据块,在读写某个数据块时按顺序进行(如磁盘) 相联存储器 按内容检索到存储位置进行读写。(如快表) 3.按在计算机中的作用分类

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/73936.html