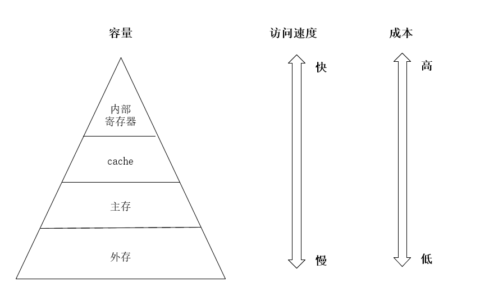

1.1计算机组成原理 1.1计算机组成原理 1.1.1计算机系统组成 CPU的定义 定义:运算器和控制器合称中央处理器(CPU) CPU的功能 1.程序控制:CPU通过执行指令来控制程序的执行顺序 2.操作控制:控制器生成每条指令的操作信号,传送到不同的部件并控制各部件的操作 3.时序控制:控制器通过时序电路产生的时钟信号进行定时,来控制各种操作有序进行 4.数据处理:运算器完成对数据的加工处理 CPU的构成 运算器、控制器、寄存器组和内部总线等部件 1.1.2CPU系统组成 运算器 算数逻辑单(ALU)执行算术或逻辑运算 累加器(AC)保存操作数和运算结果 通用寄存器(GR)存储操作熟或地址。其作用是减少CPU访问存储器的次数,提高运算速度 控制器 程序计数器(PC)存储程序指令起始地址。用于CPU从内存中读取待执行的指令。程序员可访问 指令寄存器(IR)存储从内存取出的、正在运行的指令。用于指令译码器分析指令 寄存器组 状态寄存器(SR)用于保存指令执行完成后产生的信息信息,以及中断和系统工作状态 地址寄存器(AR)用来保存当前CPU所访问的内存单的地址 1.1.3指令系统 1.基本概念 指令系统也叫机器语言,是计算器所具有的全部机器指令的集合,反映了计算机所拥有的基础功能 1.指令由操作码和地址码构成 操作码指明了指令的操作功能 地址码给出了操作数或是操作数的地址 2.指令系统功能 数据传输 算数逻辑操作 移位操作 控制操作 3.指令长度 分为固定长度和可变长度,一般字节的整数倍 2.寻址方式 指令寻址方式是指处理器根据指令中的地址码字段,查找操作数或是操作数地址的方式。常用的方法有7种 1.立即寻址 操作数就包含在指令中。指令的地址码字段给出的不是地址而是数据。(速度最快) 2.直接寻址 操作数存放在内存中,指令中直接给出操作数所在内存单的地址 3.间接寻址 指令中给出操作数地址的地址。需要通过一次或多次访问主存来操作数 4.寄存器寻址 操作数存放在某一寄存器中,指令中给出操作数的地址是寄存器编号。 5.寄存器间接寻址 操作数存放在内存中,操作数所在内存地址放在某个寄存器中。 6.相对寻址 指令中的地址码给出的是一个偏移量,操作数地址等于程序计数器PC中的地址加上指令中的偏移量。 7.变址寻址 指令中的地址码给出的是一个地址(通常是起始地址),操作数地址等于指令中的地址加上变址寄存器中的偏移量。 3.指令集 指令系统也叫机器语言,是计算器所具有的全部机器指令的集合,反映了计算机所拥有的基础功能 4.流水线 1.流水线周期 = 执行时间最长的那个指令(例如: 取指3ns,分析2ns, 执行4ns) 2.流水线执行时间 = (取指t + 分析t +执行t)+(总指令-1)*流水线时间 3.流水线技术指标:吞吐率=总指令数/流水线执行时间 1.1.4数据的表示及运算 机器码 逻辑运算 1.1.5存储体系 层次结构 层次 大多数计算机都采用3层存储架构。 结构 高速缓冲存储器cache、主存储器、外存储器。 目的 解决存储容量、成本和速度之间的矛盾 访问 高速缓存和主存可以直接被CPU访问。 原理 原理:程序存储在外存上。CPU要执行程序,先把程序从外存调入内存,再调入高速缓存,最后被CPU执行。 主存储器 定义 主存储器简称主存或内存,用来存放当前正在使用的或将要使用的数据和程序 种类 1.随机存储器RAM:特点是数据可读写,断电后会丢失数据。(RAM又分为用于制作内存的DRAM动态存储器和用于制作高速缓存的SRAM静态存储器) 2.只读存储器ROM:特点是只能读取数据,断电后不会丢失数据(特例:PROM和EPROM可擦除可编程只读存储器,PROM只能写入一次,EPROM可以多次写入) Cache 定义 高速缓存是为了解决CPU和主存速率不匹配而设置的。是介于CPU和主存之间的小容量存储器,存取速度比主存快。 原理 CPU每次读取数据时,先访问高速缓存。如果没有找到数据,才会再次访问主存,并把找到的数据放入高速缓存中。 结构 Cache由控制部分和存储器构成。存储器用来存放数据。控制部分的功能是判断CPU要访问的信息是否在Cache中,若在即为命中。 外存储器 定义 用来存放暂时不用的程序和数据,并且以文件的形式存储。 原理 CPU不能直接访问外存中的程序和数据,只有将其以文件为单位,调入主存后,才可以访问。 特点 存储容量大,存取速度慢,单位成本低 种类 硬盘,Flash闪存盘(u盘,固态硬盘),光盘(CD和DVD-ROM)等。 相关术语 存储方式 存储方式:顺序存取(磁带),直接存取(硬盘),随机存取(内存),相关存取(Cache) 存储容量 bit → Byte →KB → MB →GB →TB 位示图计算 硬盘容量 % 物理快大小 % 计算机字长 1.1.6I/O系统 基本概念 I/O系统是输入设备和输出设备的总称。输入设备包括键盘等设备,输出设备包括显示器等设备。 I/O接口是I/O设备在设备主板上的各个接口。主要功能是完成数据缓存,程序中断和管理等功能。 I/O接口分类 按传送方式:并行接口和串行接口。按时序控制方式:同步接口和异步接 按主机访问l/O设备的控制方式:程序查询接口,中断接口,DMA接口。 接口控制方式 1.直接程序控制:也叫轮询方式,CPU需要对各个I/O设备的状态进行循环检查。CPU利用率最低。 2.中断方式:I/O接口中设置中断控制器,当I/O设备发出中断请求后,CPU暂停执行现行程序,使用堆栈保护好程序的断点和中断服务程序入口,转而去处理中断请求,处理完成后再返回来继续执行程序。 3.DMA方式:DMA方式采用专门的DMA控制器来管理内存与外设的数据传送,在不受CPU干预的情况下,控制I/O设备与系统主存之间的直接数据传输。CPU利用率最高。 1.1.7总线系统 定义 总线是一组用来连接计算机各个设备的公共信息传送线路 按工作任务分类 1.数据总线: 用于传送数据。可以在CPU,存储器和I/O设备之间双向传送数据。 2.地址总线:用于传送地址。而且只能单方向从CPU传向外部设备 3.控制总线:用来传送控制信号和时序信号。控制总线采用双向传送数据,具体方向由控制信号决定 按数据传输方式 1.并行线路:并行线路是数据一组一组的同时发送。常见总线有内存,PATA硬盘,PCI等。 2.串行总线:串行就是数据是一位一位的顺序发送。常见总线有USB,SATA硬盘,PCI-E,UART,I2C等。 按物理结构分类 1.单总线结构:用一条系统总线将各个部件连接起来 2.双总线结构:在单总线的基础上,在CPU和主存之间专门架设一组高速存储总线。 3.三总线结构:在双总线的基础上增加了I/O总线,适用于大型计算机 总线带宽 总线带宽:是指总线的最大数据传输率,即每秒传输的数据总量 计算公式:总线带宽(MB/s)=总线宽度*传输能力(时钟频率/时钟频率)

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/73077.html