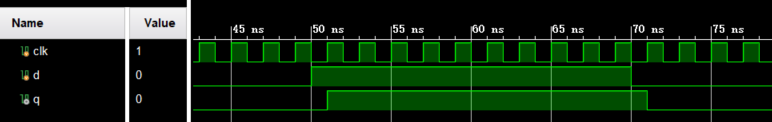

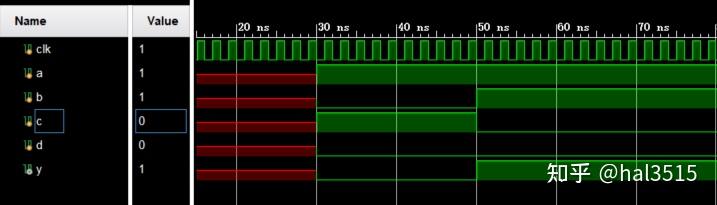

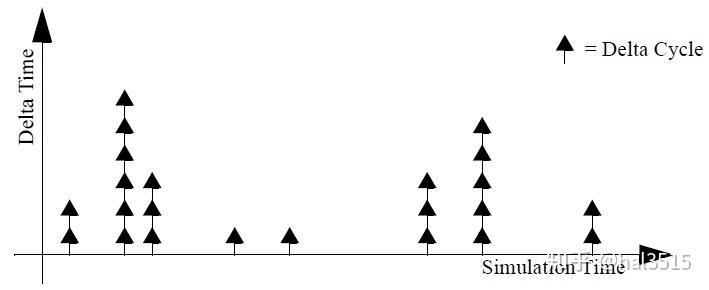

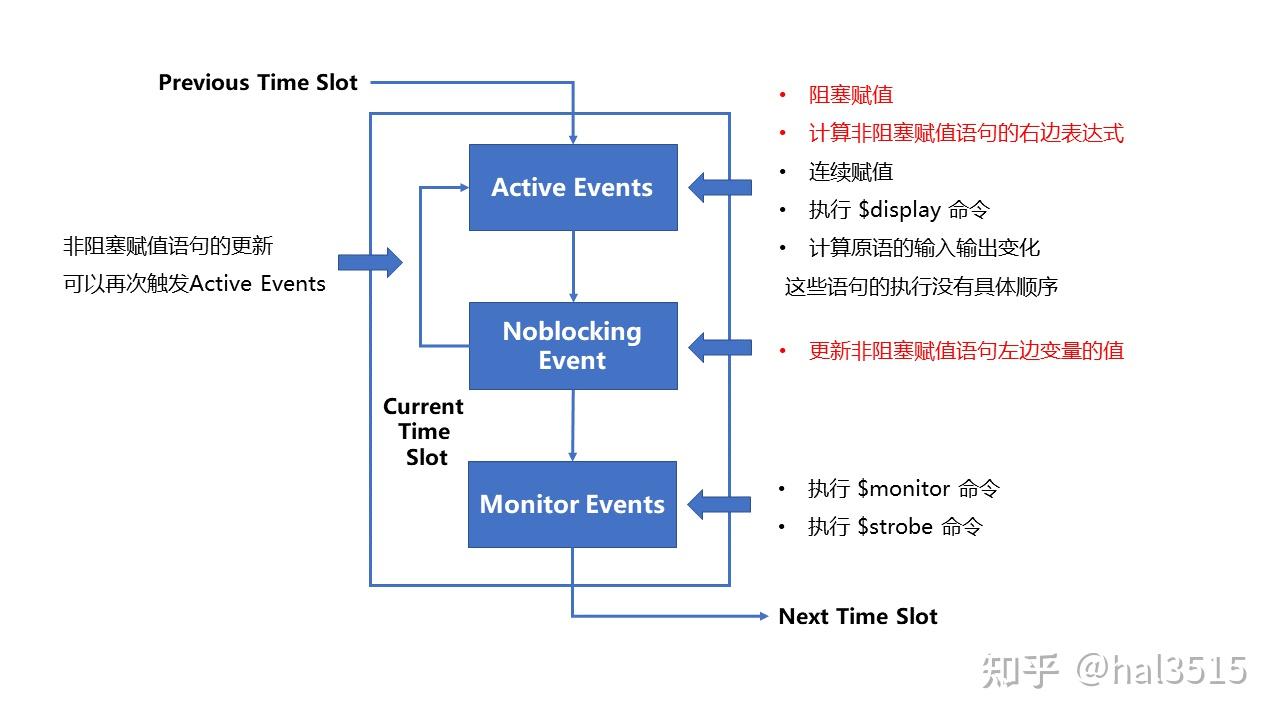

verilog语法学习1:深入理解阻塞赋值与非阻塞赋值 准备入坑FPGA了,verilog肯定是绕不开的第一关。今天我学了阻塞赋值和非阻塞赋值,但是对这两种赋值方式感到非常困惑,为啥要用两种赋值方式呢?只用一种它不简单吗?它不香吗?于是好奇的我就去仔细理解了一下这两种方式的异同。具体参考过的内容列在下面了:verilog数字系统设计教程(夏宇闻):学习verilog的必读书。第四版第十四章深入理解阻塞和非阻塞赋值的异同。Nonblocking Assignments in Verilog Synthesis, Coding Styles That Kill! (Clifford E. Cummings ):这篇文章是夏老师那本书中相关内容的来源。IEEE Standard for Verilog® Hardware Description Language:想知道有关仿真器更详细和更准确的内容可以直接看IEEE的标准,1364™-2005的11.Scheduling semantics。 一、阻塞赋值与非阻塞赋值的两条要点 实际上在写verilog代码的过程中没有必要对阻塞赋值与非阻塞赋值有很深刻的了解,总体记住以下两条原则就可以愉快的写代码了:描述组合逻辑使用阻塞赋值“=”。描述时序逻辑使用非阻塞赋值“<=”。 如果对具体为什么没兴趣的话读到这里就可以结束了。但是毕竟人都是有好奇心的,所以也就继续说明具体原因。 二、阻塞赋值与非阻塞赋值名称的由来 首先为了方便后面的说明这里引入两个缩写RHS(right-hand-side):赋值等号右边的表达式或变量可分别缩写为RHS表达式或RHS变量。LHS(left-hand-side):赋值等号左边的表达式或变量可分别缩写为LHS表达式或LHS变量。 阻塞赋值的英文名称是(blocking assignment),符号是“=”:我们看交通阻塞就是说这条路上的车堵上了,只有这条路上的车过去旁边路上的车才能继续通过,相似的阻塞赋值要求在赋值时先计算RHS部分的值,这时赋值语句不允许任何别的verilog语句的干扰,直到现行的赋值完成时刻,即把RHS赋值给LHS的时刻,它才允许别的赋值语句的执行。由于在赋值过程中阻塞别的语句的执行,因此得名阻塞赋值。 非阻塞赋值的英文名称是(nonblocking assignment),符号是“<=”:与阻塞赋值不同,非阻塞赋值在赋值开始的时刻计算RHS表达式,在赋值结束的时刻计算LHS表达式,而在这之间其他的verilog语句是可以正常执行的。由于在赋值过程中并未阻塞别的语句的执行,因此得名非阻塞赋值。 对这两个名称有了进一步认识之后就可以对阻塞赋值与非阻塞赋值进行深入的理解了。 三、深入理解:EDA中的仿真器 首先来简单说明EDA工具中的仿真流程。我们都知道,硬件电路是并行执行,而在CPU上跑的仿真器是软件编写的,因此是串行执行的。为了用串行的软件模拟出并行的硬件特性,仿真器中就引入了仿真时间这个概念。仿真是严格按照仿真时间的时间轴向前推进的。对于在不同时间发生的事件,为了以正确的时间处理它们,仿真器会按顺序将事件放在事件队列中。如果同一时刻有多个事件,那么按照优先级放到事件队列。事件的优先级就定义在后面提到的层次化事件队列(stratified event queue)中。下面这张图展示了仿真的流程,一方面横轴按照仿真时间推进,另一方面纵轴要按照同一时刻发生的事件推进。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/52131.html