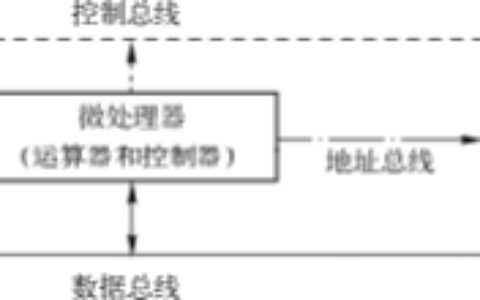

FPGA_Xilinx_7系列_时钟篇2_时钟结构详细解剖 导读: 通过上一篇文章“时钟管理技术”,我们了解Xilinx 7系列FPGA主要有全局时钟、区域时钟、时钟管理块(CMT)。 通过以上时钟资源的结合,Xilinx 7系列FPGA可实现高性能和可靠的时钟分配,以满足各种设计需求,并提供时钟驱动逻辑资源的灵活性和可扩展性。那今天我们一起解剖Xilinx 7系列FPGA的时钟结构,看看它到底如何实现如此丰富的时钟资源并能够做到完美平衡。 先打一针预防针,基于FPGA的时钟结构相关知识本身比较复杂,读者必须认真跟着节奏阅读,我将以更形象和更通俗易懂的描述/示图带大家了解FPGA整个时钟树框架、涉及的名称概念、区域时钟、时钟管理块(CMT)等概念。 先抛出一个问题:FPGA如果不设计合适的时钟结构会有什么后果?

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/49034.html