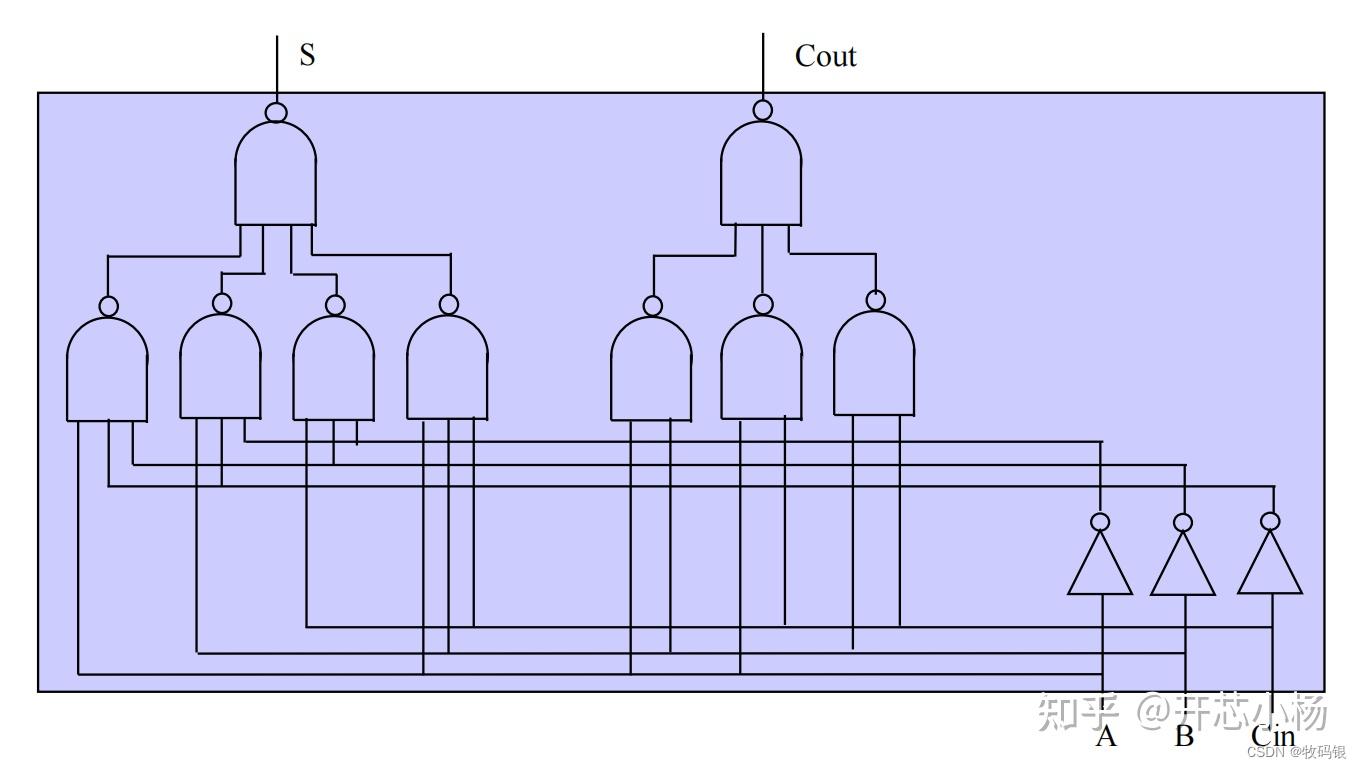

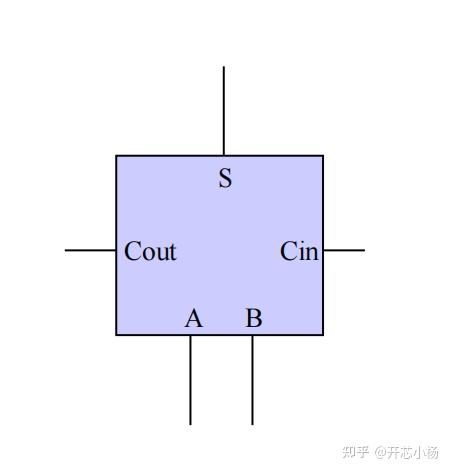

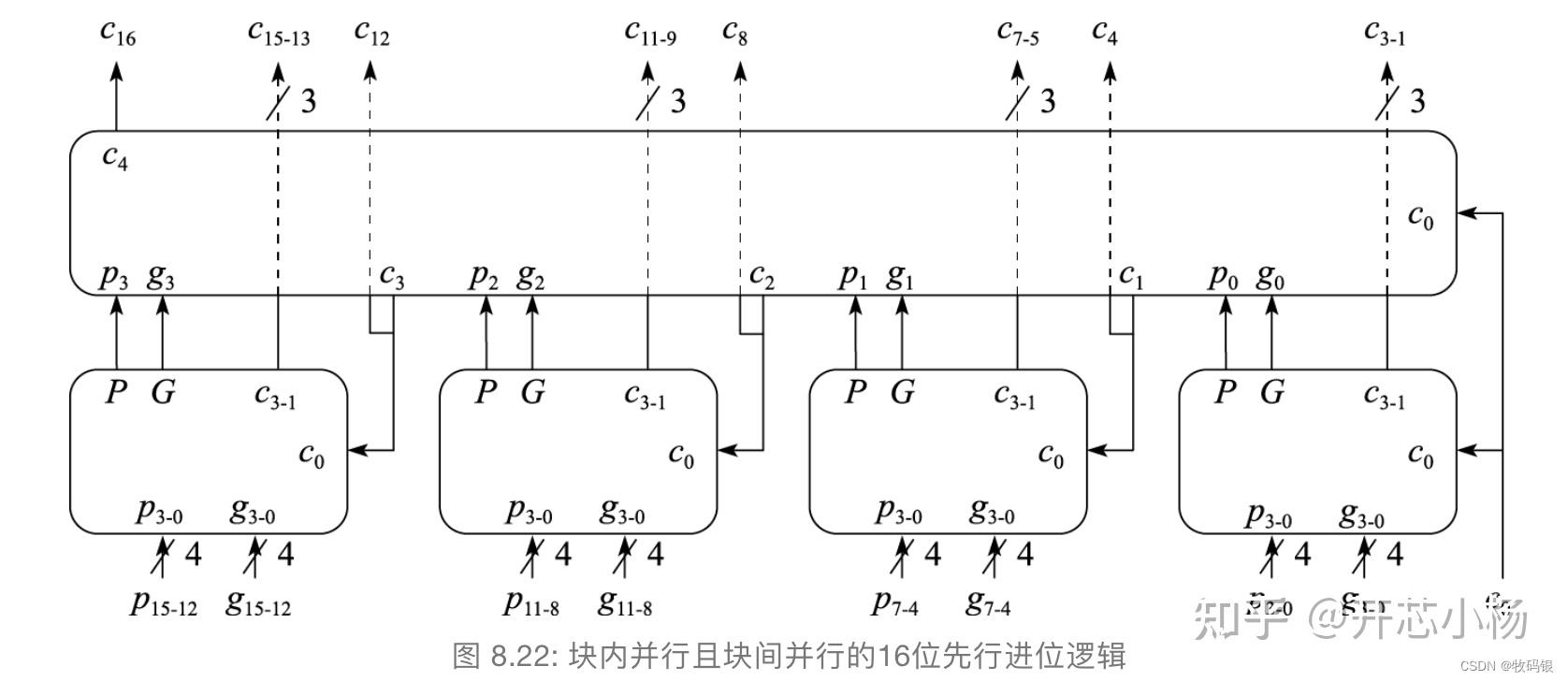

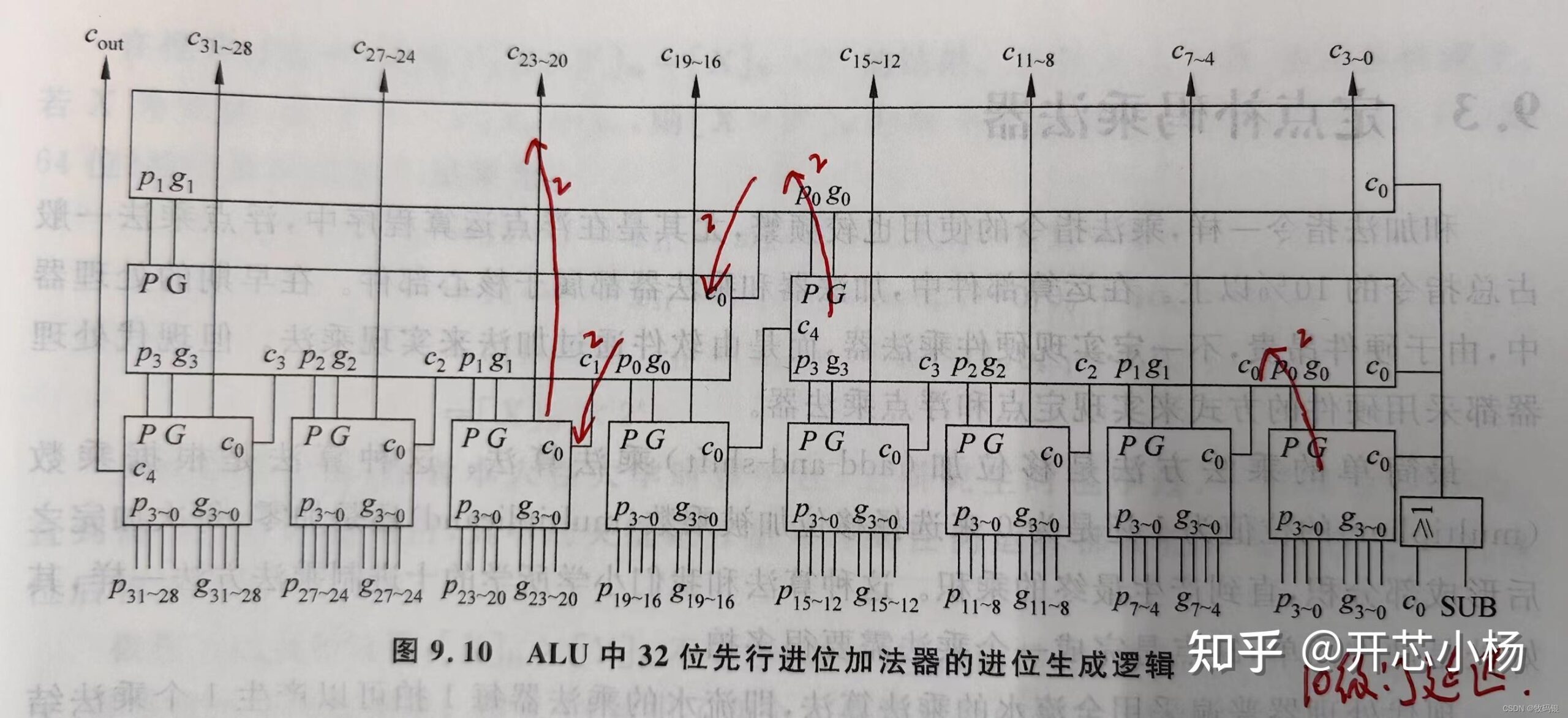

计算机体系结构——功能部件 一、功能部件——加法器 1. 全加器 全加器——将两位本地二进制数和1位低位进位的数进行相加,求的1位本地结果以及1位向高位进位的结果。简单来说就是3个input,2个output,这里的逻辑比较简单,我就不具体介绍了。 下图所示的数全加器的逻辑图,这里我们需要分析一下门的延迟,得到进位Cout需要2级门的延迟,得到结果S需要3级门的延迟。这个延迟需要特别留意,对后面分析问题比较重要‼️ 图1:

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/28757.html