计算机组成原理第三章课后题参考答案_计算机组成原理答案计算机组成原理(万字爆肝整理)第一章 计算机系统概述“较简单,不做过多赘述,后面会详细学到”第一节 计算机系统层次结构1.计算机系统的基本组成:硬件+软件2.计算机硬件的基本组成:运算器+存储器+控制器+输入设备+输出设备3.系统软件和应用软件系

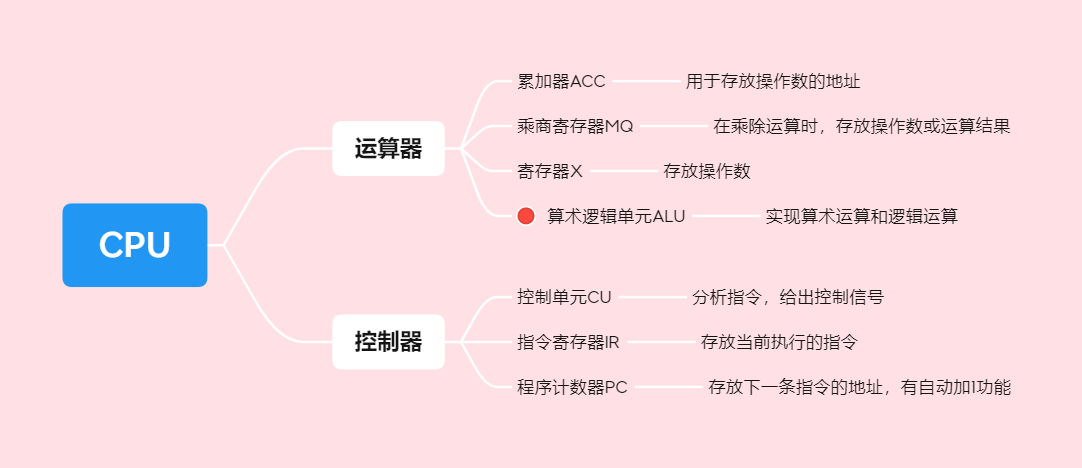

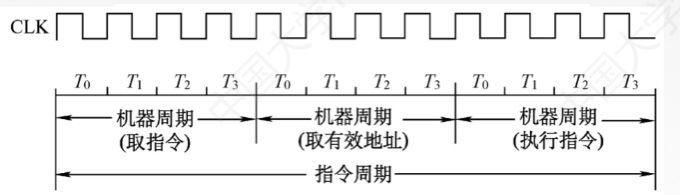

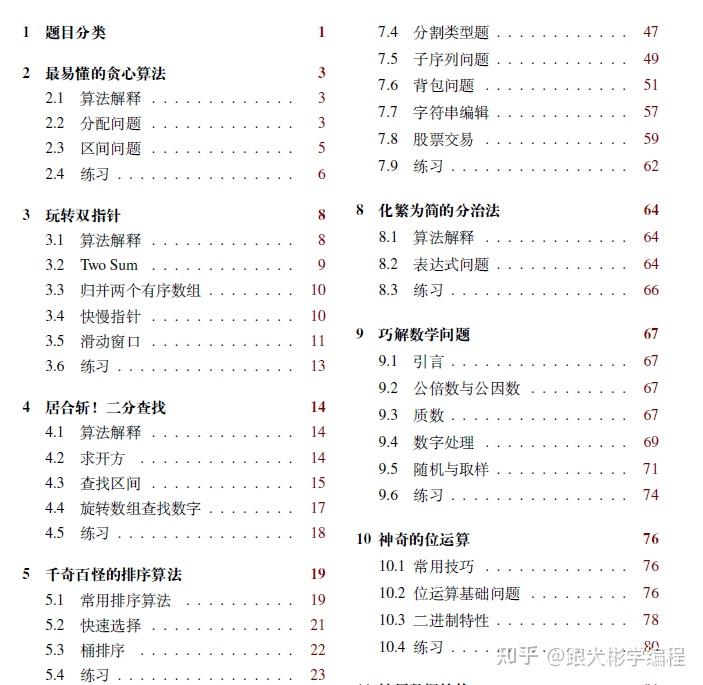

计算机组成原理(万字爆肝整理) 第一章 计算机系统概述 “较简单,不做过多赘述,后面会详细学到” 第一节 计算机系统层次结构 1.计算机系统的基本组成:硬件+软件 2.计算机硬件的基本组成:运算器+存储器+控制器+输入设备+输出设备 3.系统软件和应用软件系统软件操作系统、数据库管理系统、语言处理程序、分布式软件系统、网络软件系统、标准库语言、服务性程序应用软件科学计算类程序、工程设计类程序、数据统计与处理程序 4.(易考)翻译程序:汇编程序(汇编器)将汇编语言程序翻译成机器语言程序解释程序(解释器)将源程序翻译成机器指令并立即执行编译程序(编译器)将高级语言翻译城机器语言或汇编语言 第二节 计算机性能指标 吞吐量:表征一台计算机在某一时间间隔内能够处理信息量。响应时间:表征从输入有效到系统产生响应之间的时间度量,用时间单位来度量的。利用率:在给定的时间间隔系统被实际使用的时间所占的比率,用百分比表示的。处理机字长:指处理机运算器中一次能够完成二进制数运算的位数,如 32 位、64 位。总线宽度:一般指 CPU 中运算器与存储器之间进行互连的内部总线二进制位数。存储器容量:存储器中所有存储单的总数目,通常用 KB、MB、GB、TB 来表示。公式一般是:位数×个数 (MAR×MDR)存储器带宽:单位时间内从存储器读出的二进制数信息量,一般用字节数/秒表示。主频/时钟周期:CPU 的工作节拍受主时钟控制,主时钟不断产生固定频率的时钟度量单位是 MHz、GHz 主频的倒数称为 CPU 时钟周期(T),T=1/f,度量单位是 μs、ns。 K= 103 ,M= 106 ,G= 109 易错:时钟频率的提高,不能保证CPU执行速度又同倍速的提高,有时候还会减慢。CPU 执行时间:表示 CPU 执行一般程序所占用的 CPU 时间,可用下式计算: CPU 执行时间 = CPU 时钟周期数 * CPU 时钟周期CPI:执行一条指令所需的平均时钟周期数。用下式计算: CPI = 执行某段程序所需的 CPU 时钟周期数 / 程序包含的指令条数MIPS:(Million Instructions Per Second)的缩写,表示平均每秒执行多少百万条定点指令数,用下式计算: MIPS = 指令数 / (程序执行时间 * 10^6)FLOPS:(Floating-point Operations Per Second)的缩写,表示每秒执行浮点操作的次数,用来衡量机器浮点操作的性能。用下式计算:FLOPS = 程序中的浮点操作次数 / 程序执行时间(s) 题目总结: ①对于高级语言程序员来说,浮点数格式、乘法指令、数据如何在运算器中运算时透明的。对于汇编语言程序员,指令格式,机器构造,数据格式则不是透明的。 ②在CPU中,IR、MAR、MDR对各类程序员都是透明。 ③机器字长,指令字长,存储字长 机器字长也称字长——是计算机直接处理二进制数据的位数,机器字长一半等于内部寄存器的大小,它决定了计算机的运算精度。 指令字长——一个指令中包含的二进制代码的位数。 存储字长——一个存储单中二进制代码的长度。 指令字长一般是存储字长的整数倍,若指令字长等于存储字长的2倍,则需要2次访存来取出一条指令,因此取值周期为机器周期的2倍;若指令字长等于存储字长,则取值周期等于机器周期的。分享一本谷歌大佬撰写的算法手册,整整 300 道 LeetCode 题目,并且都是最优解,非常强!这本手册帮助不少朋友加入大厂,大家加油!

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们 举报,一经查实,本站将立刻删除。

文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/24221.html