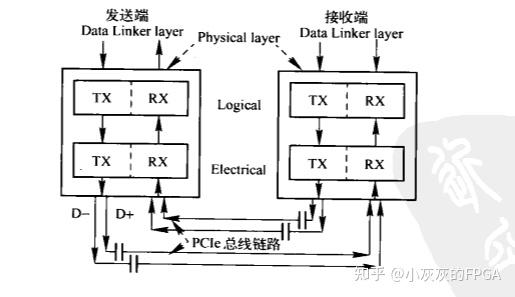

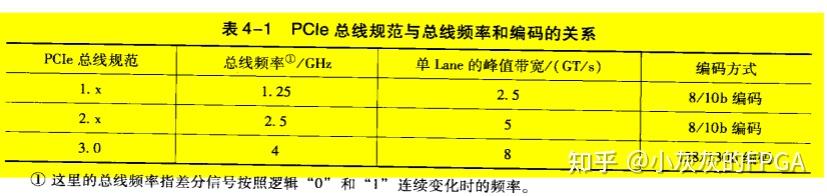

PCIe 3.0和PCIe 4.0的区别在哪? 可以看看这篇文章,更多的是带宽吞吐量,至于编码方式,访问方式,几乎没什么变化。 本节目录 本节内容 一、PCIe总线概述 PCIe总线使用了高速差分线,并采用端到端的链接方式,每一条PCIe链路中只能连接两个设备。还使用了网络通信中的技术,比如支持多种数据路由方式,基于多通路的数据传递方式和基于报文的数据传送方式,并充分考虑在数据传送中出现的服务质量Qos(Quality of Service)问题。 二、PCIe——端到端的数据传递 PCIe链路使用“端到端的数据传递方式”,发送端和接收端中都含有发送逻辑TX和接收逻辑RX。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/21177.html