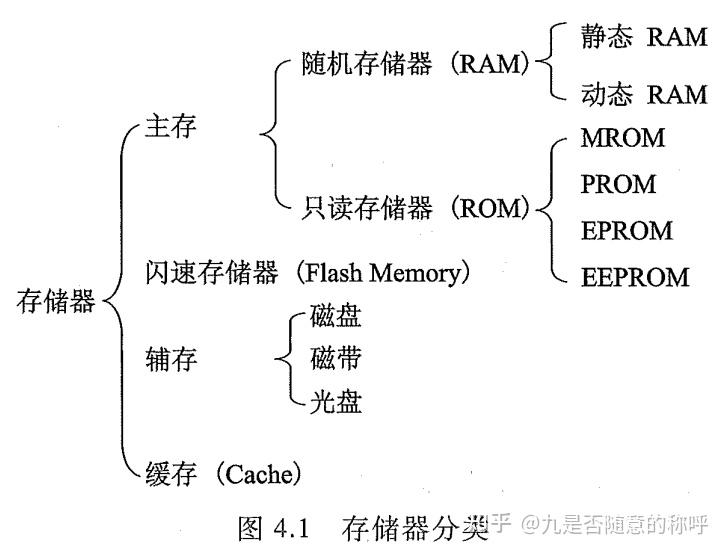

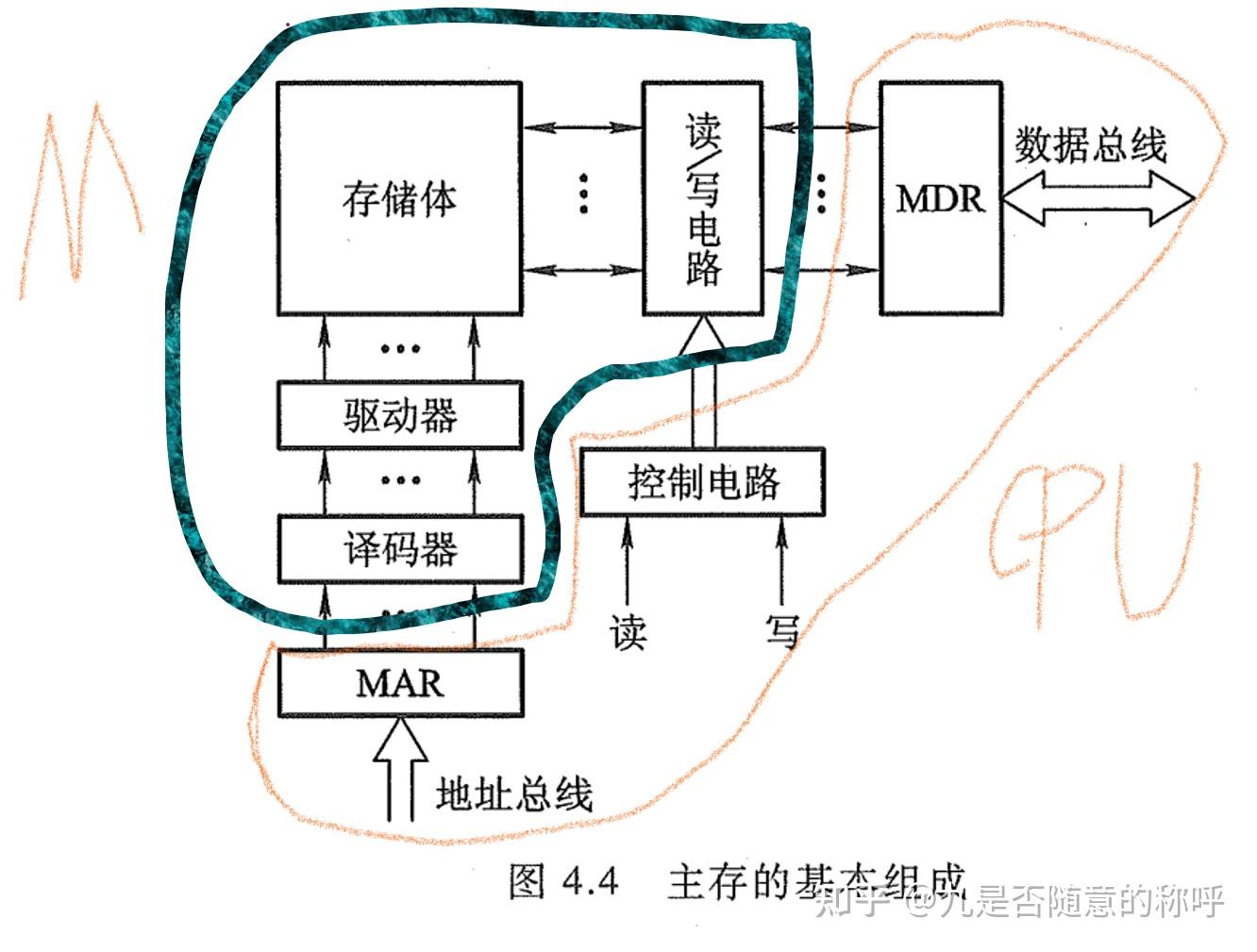

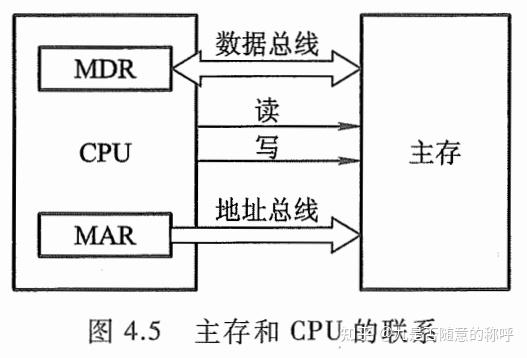

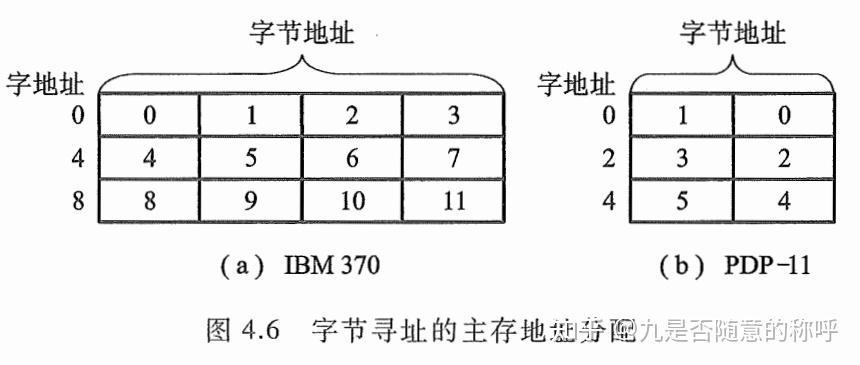

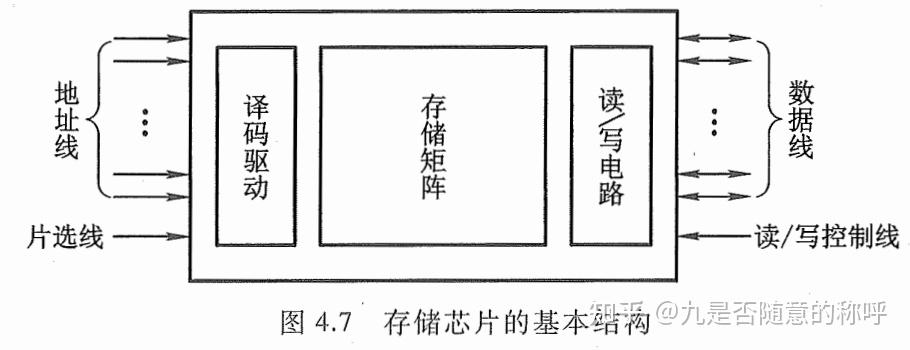

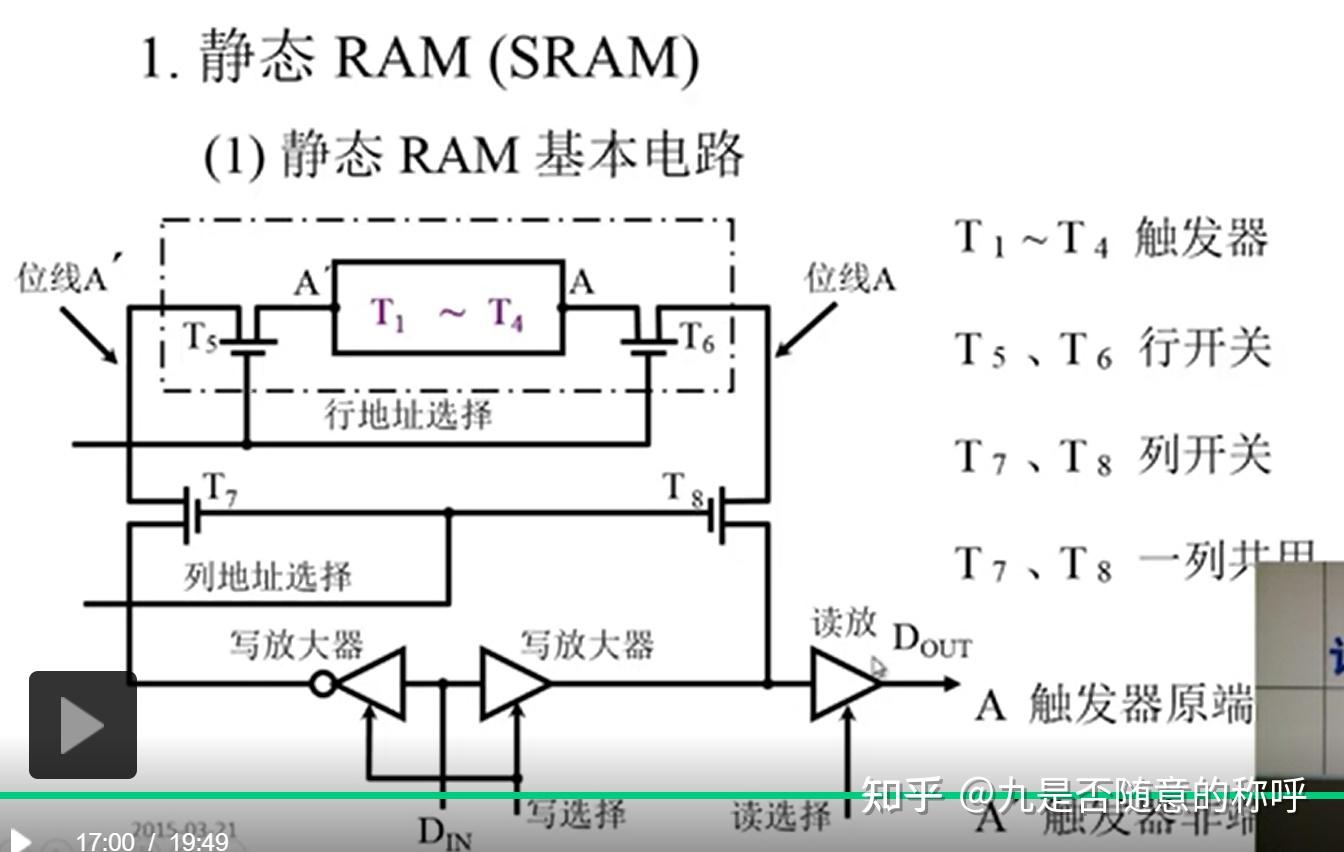

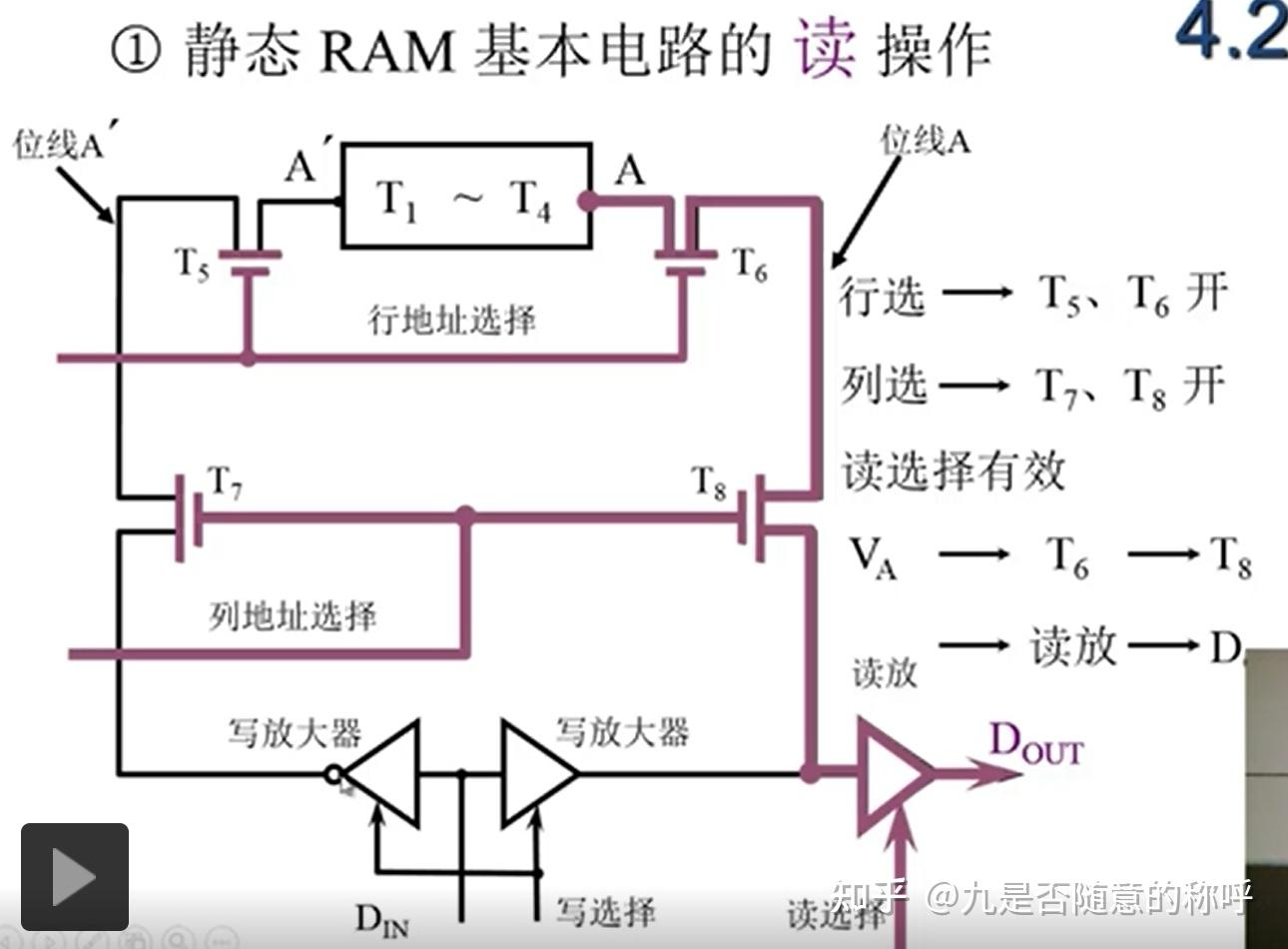

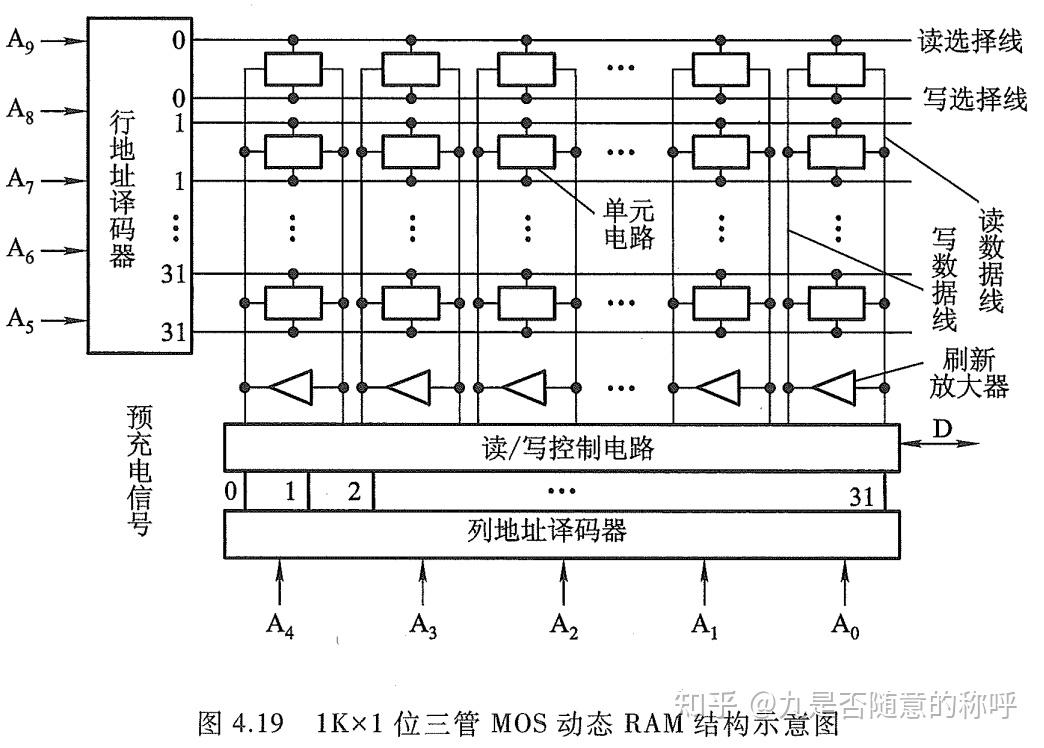

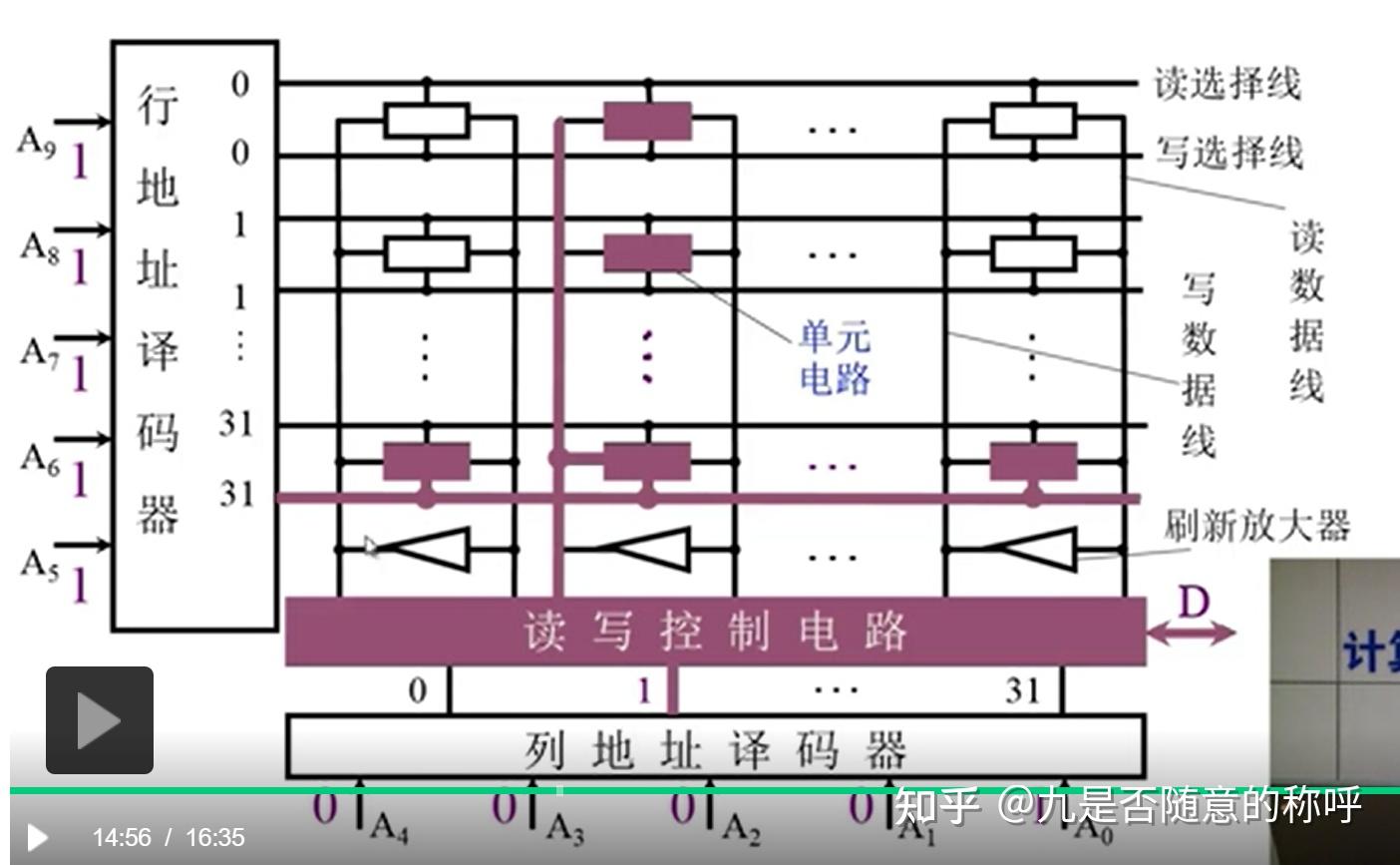

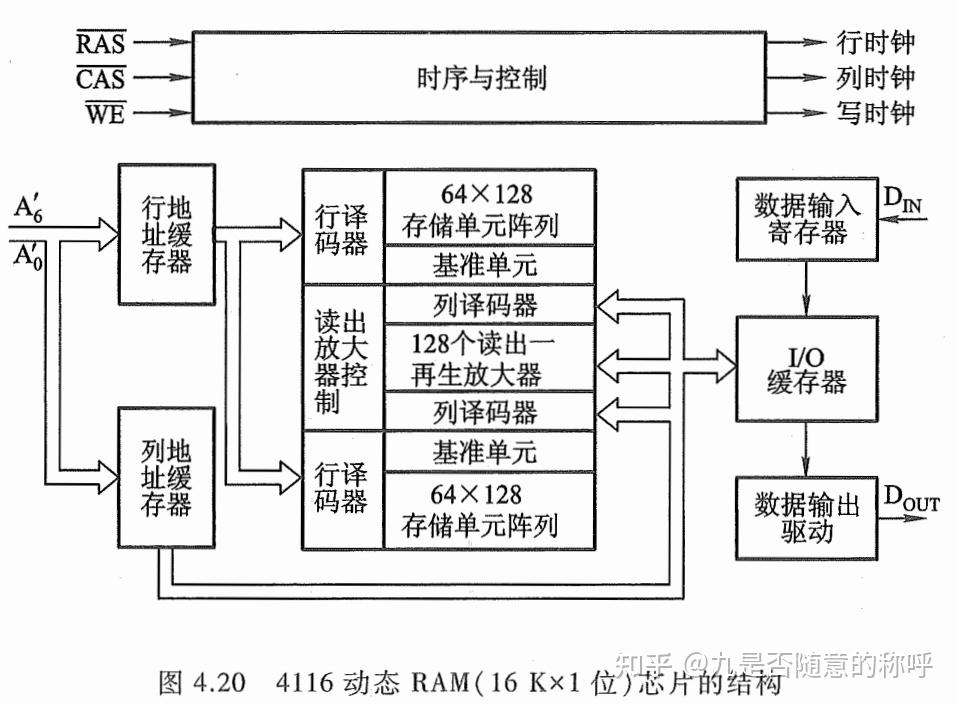

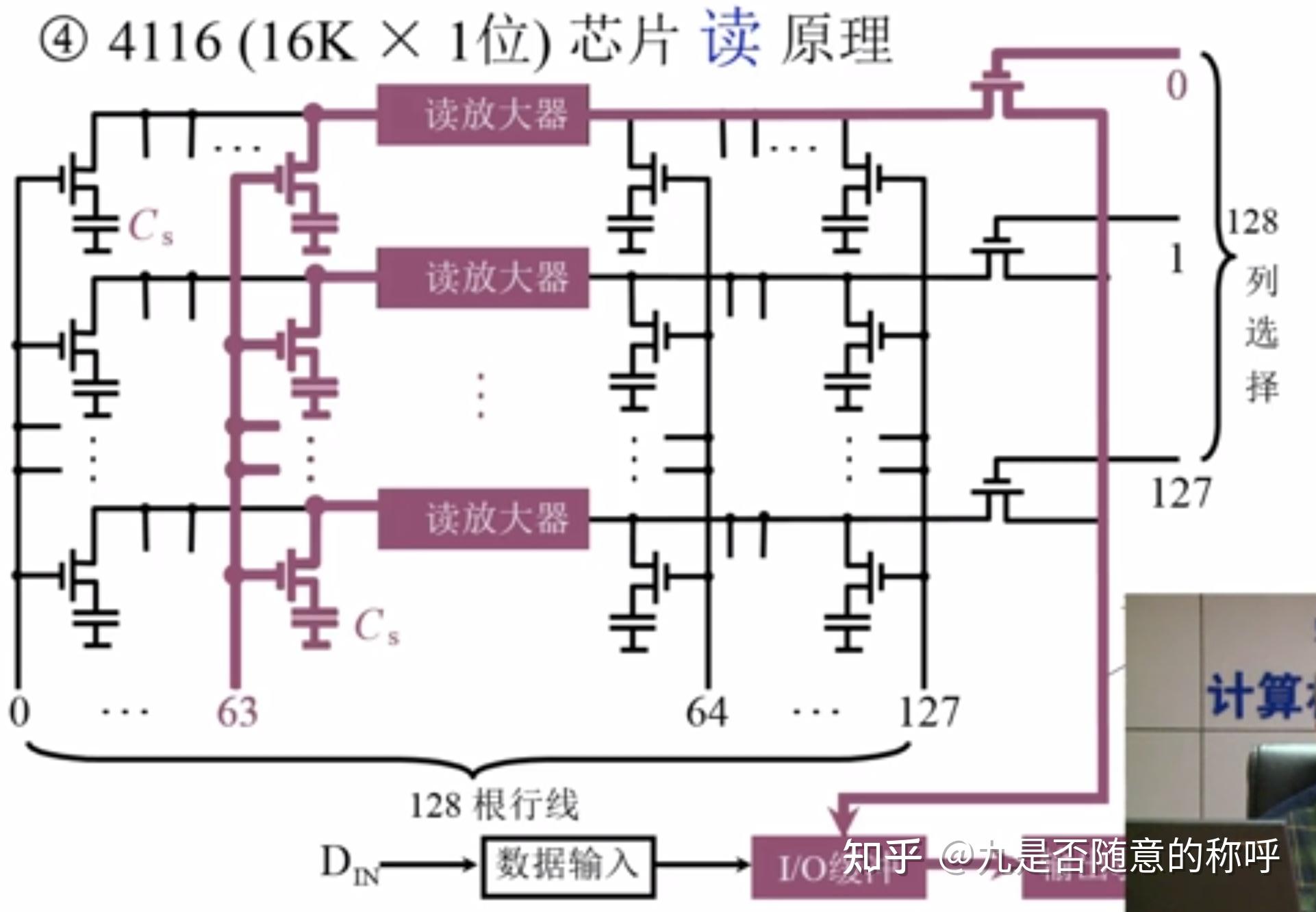

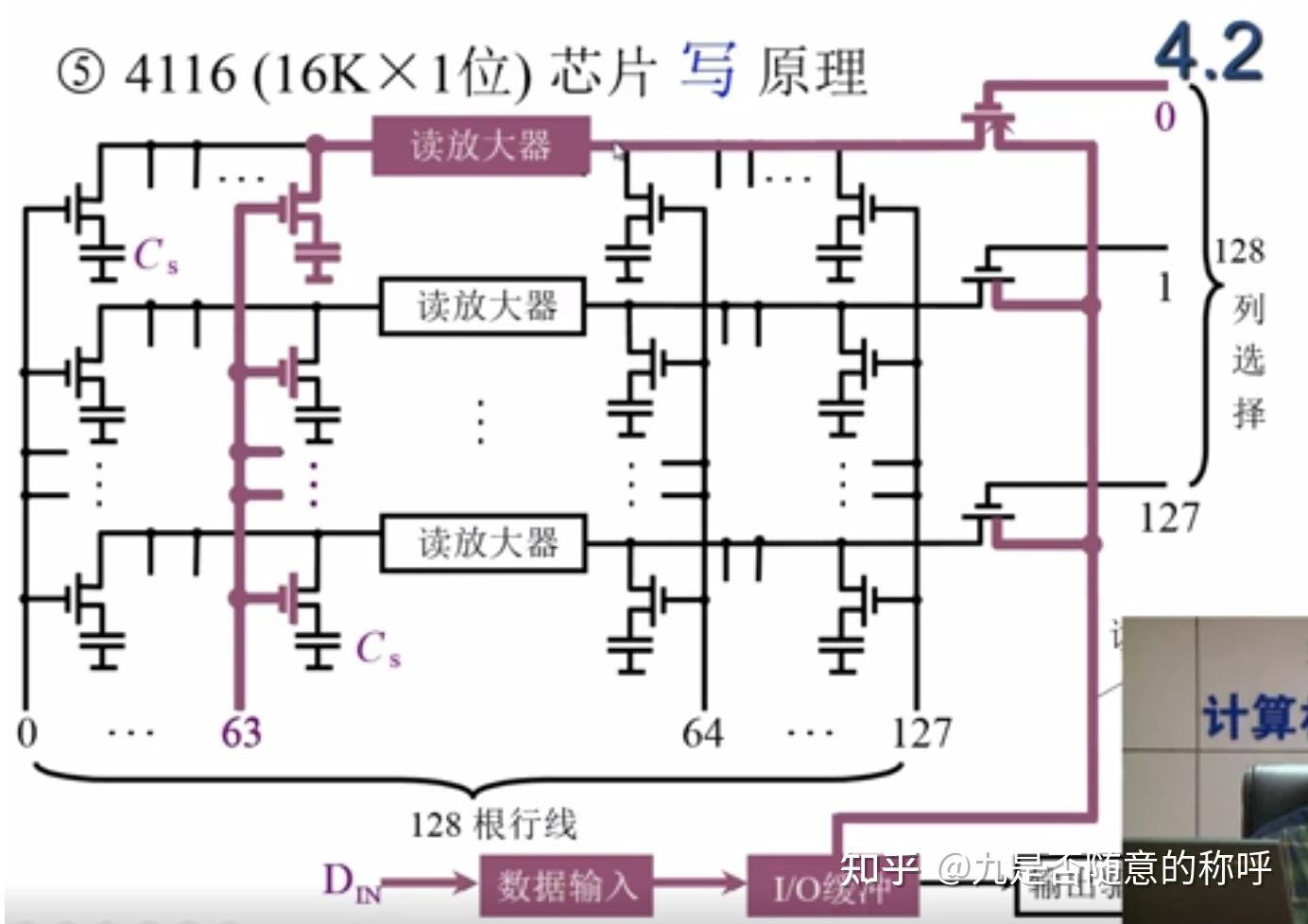

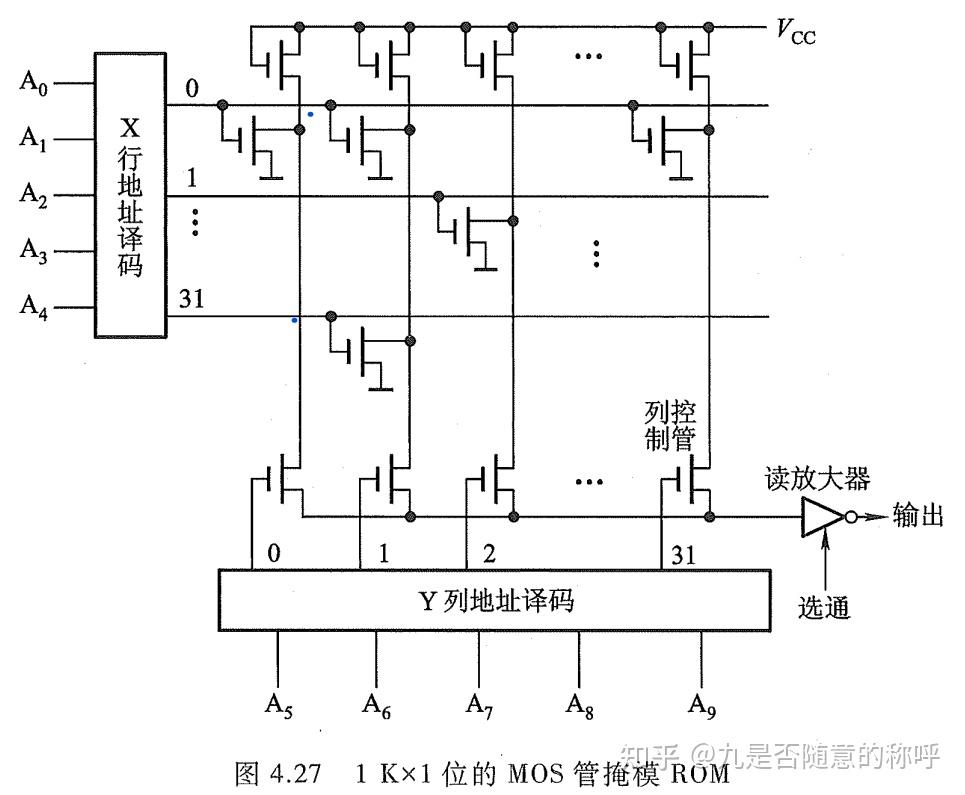

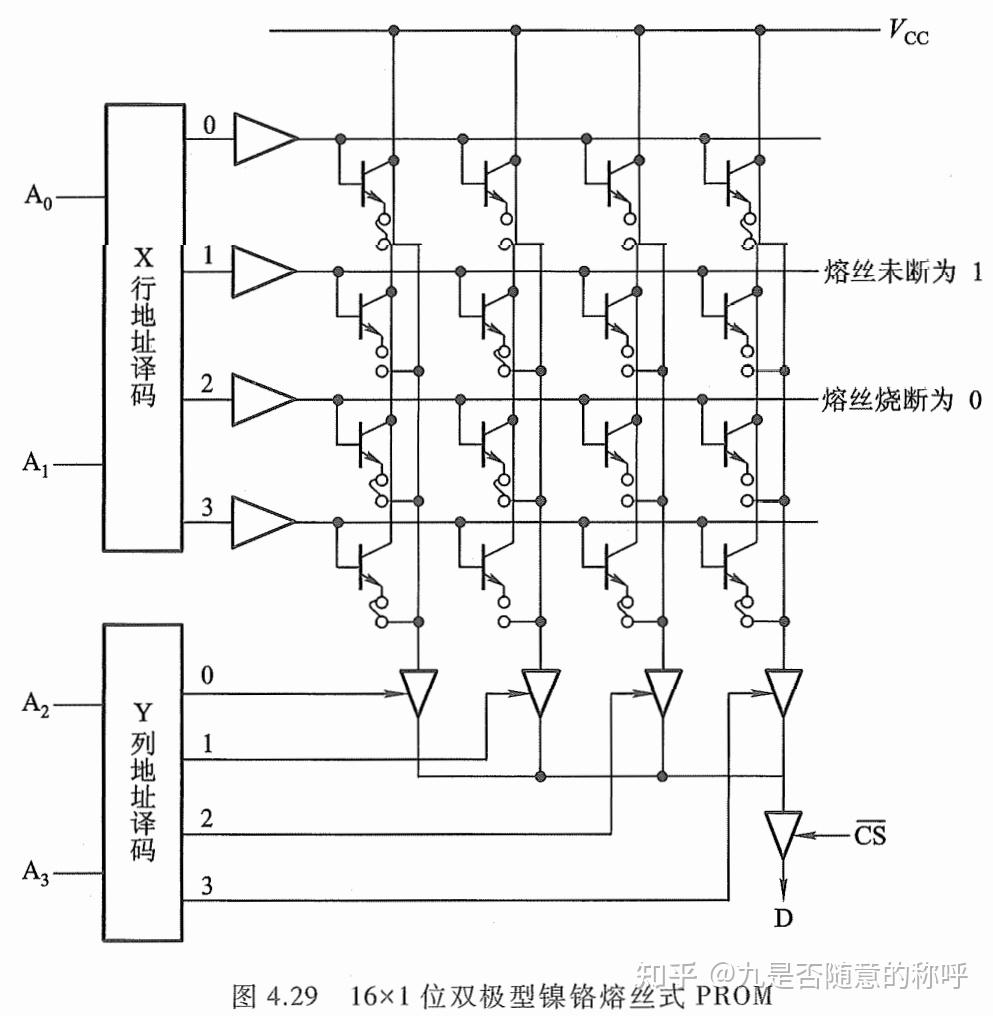

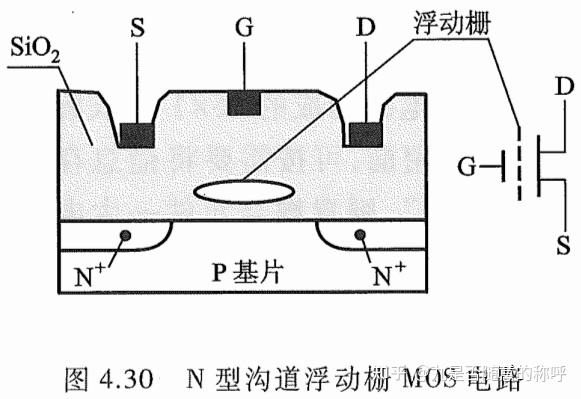

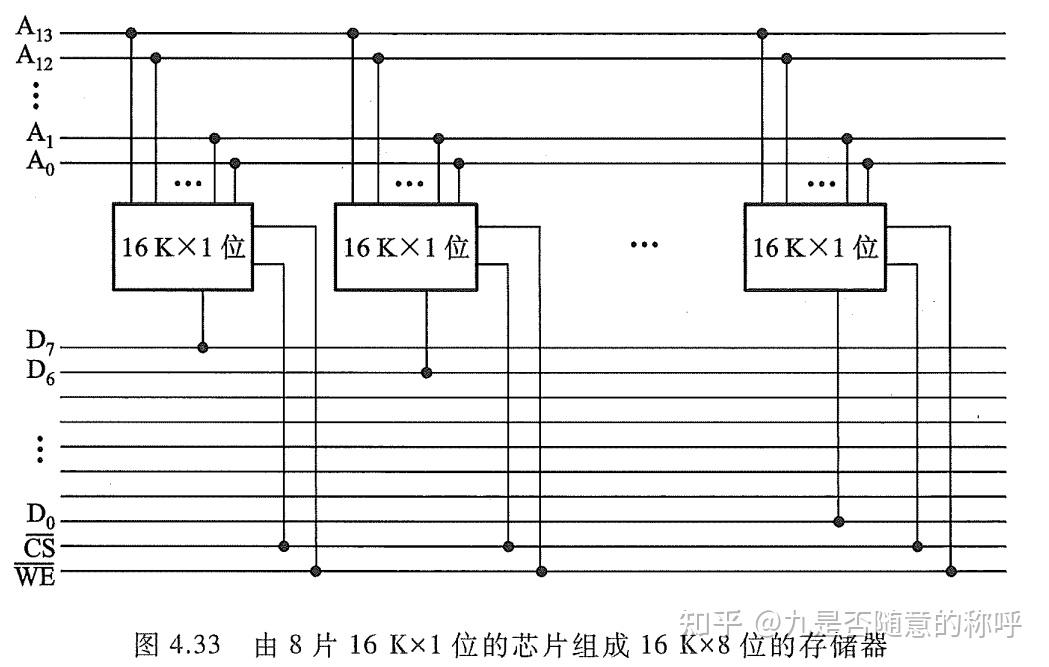

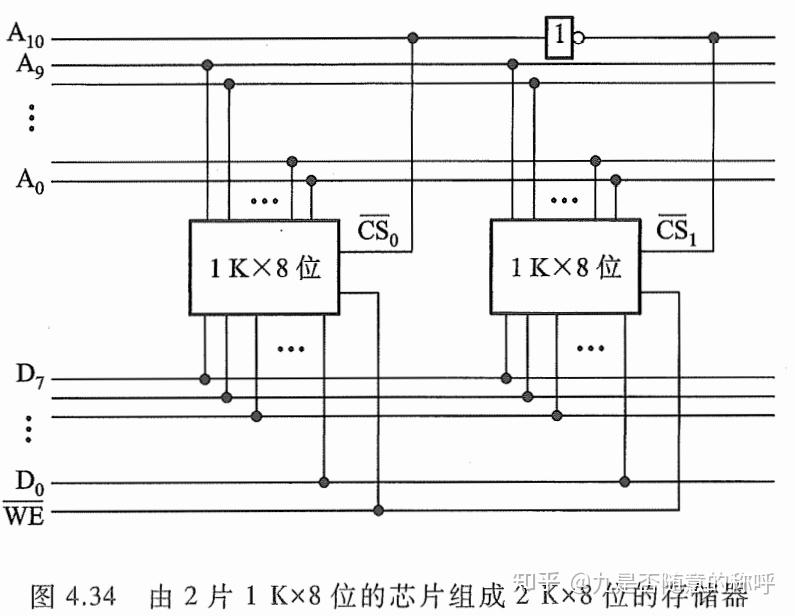

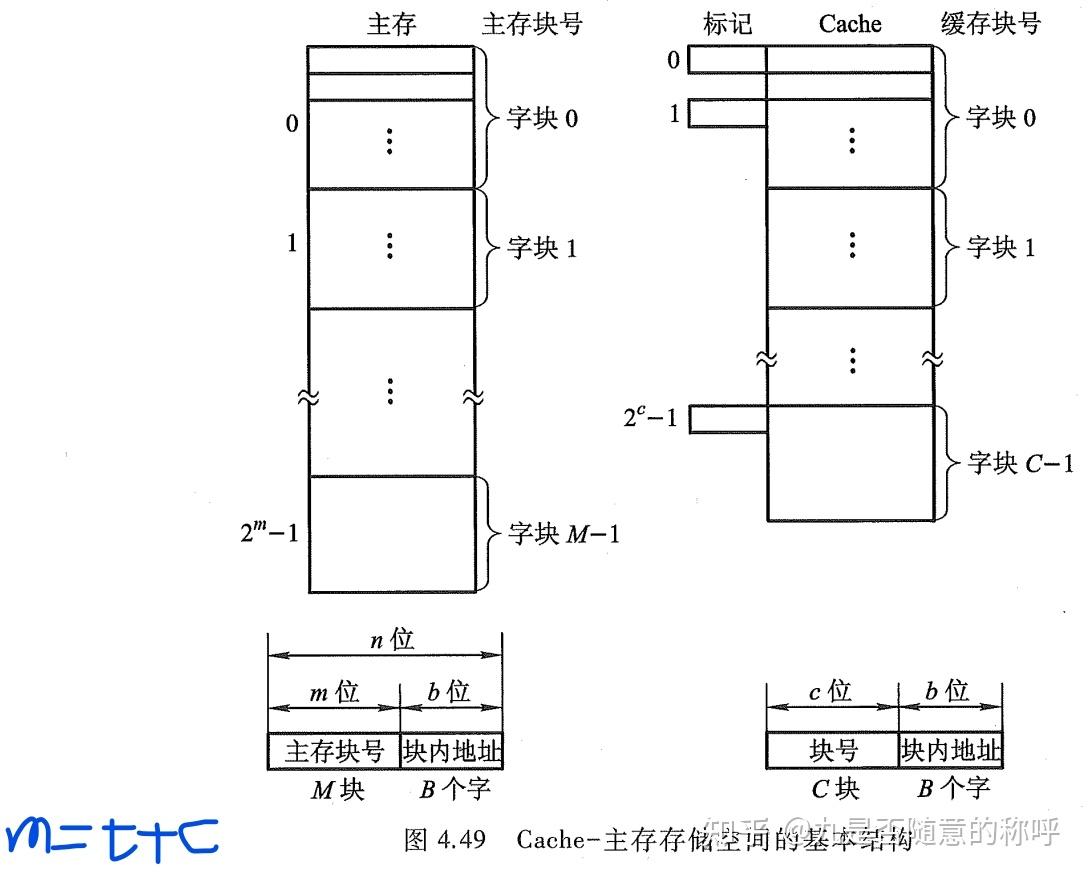

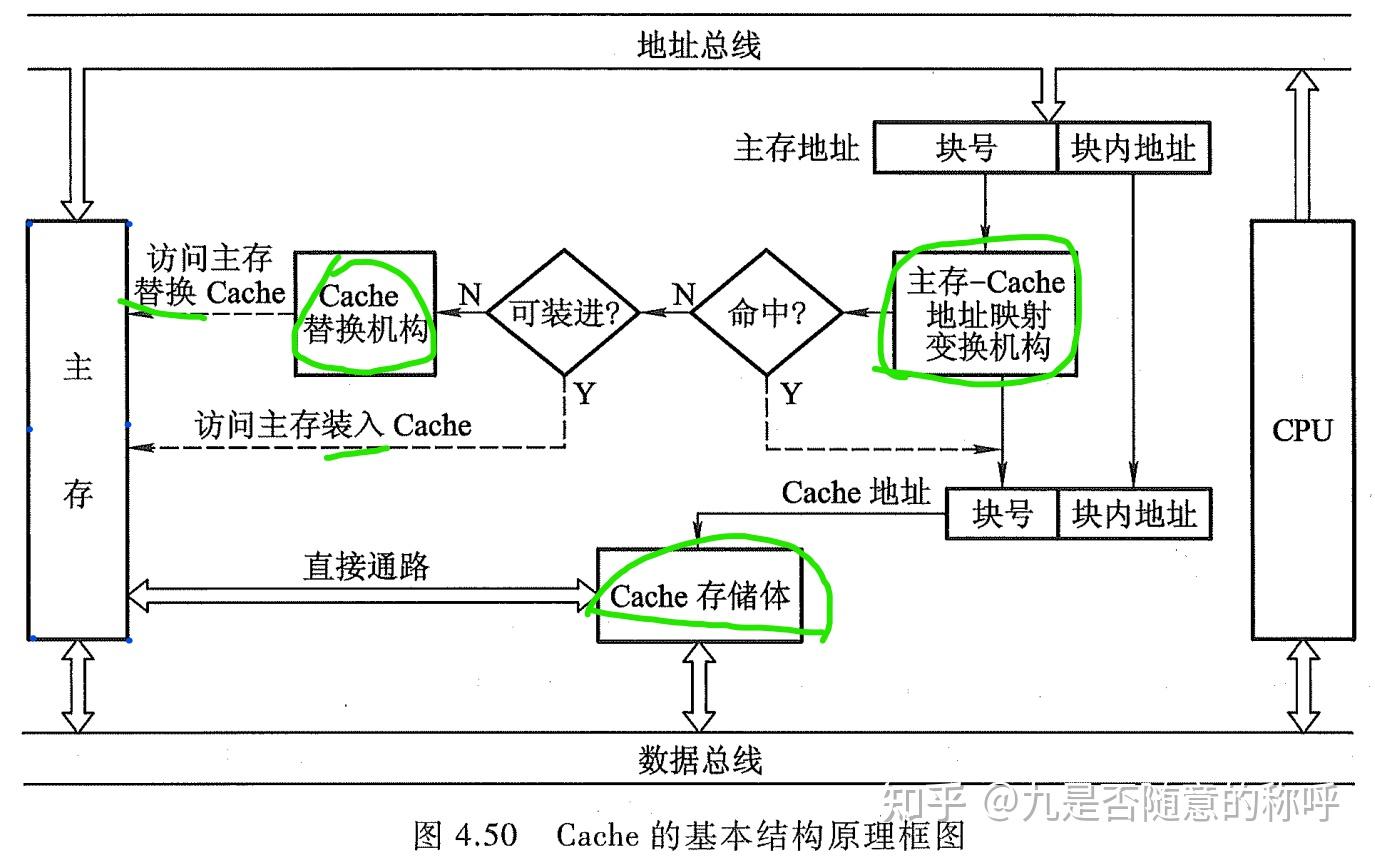

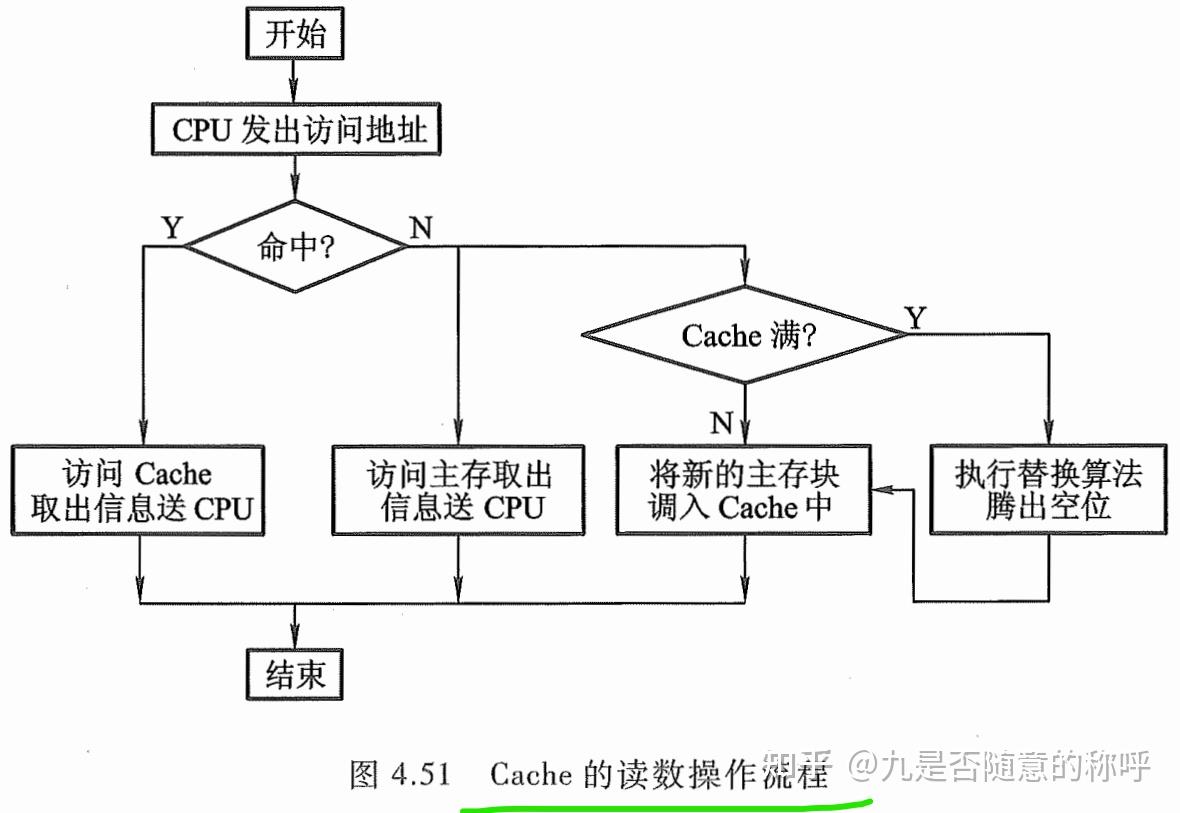

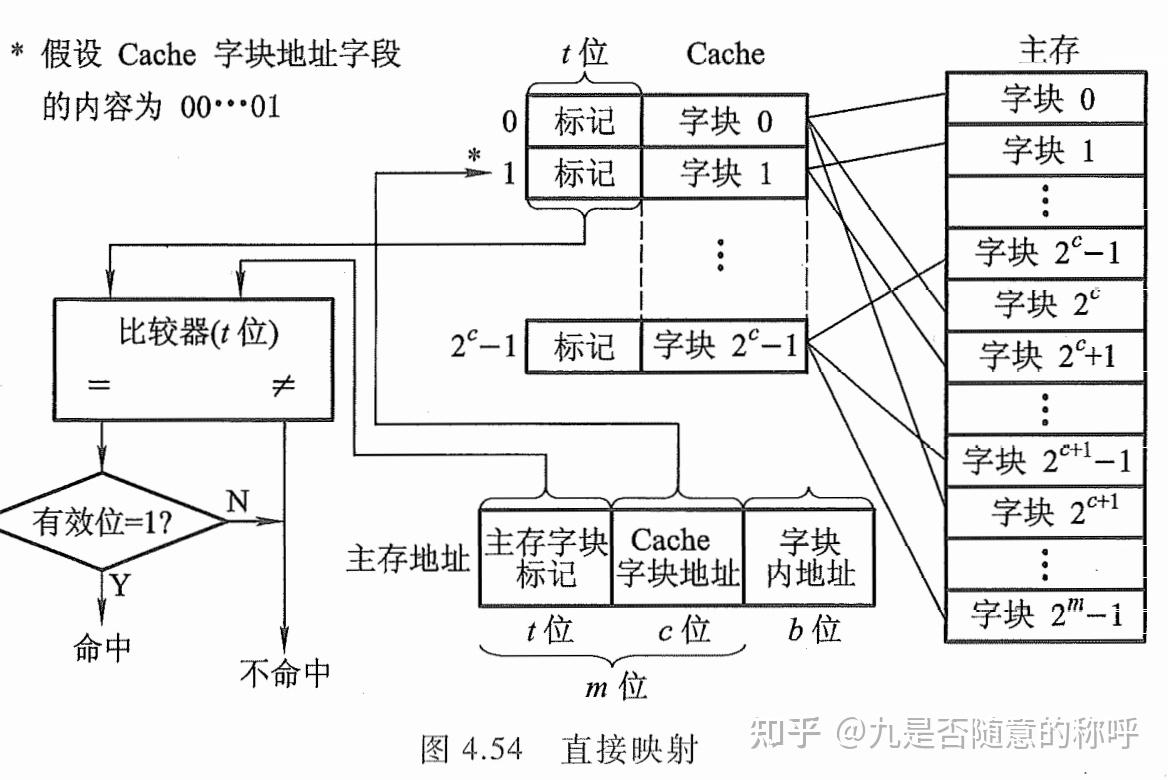

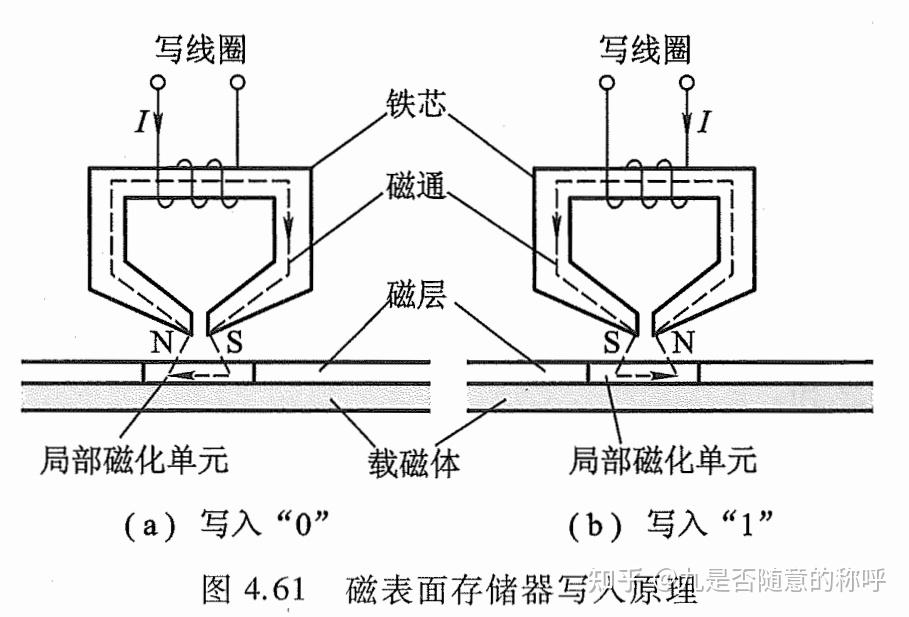

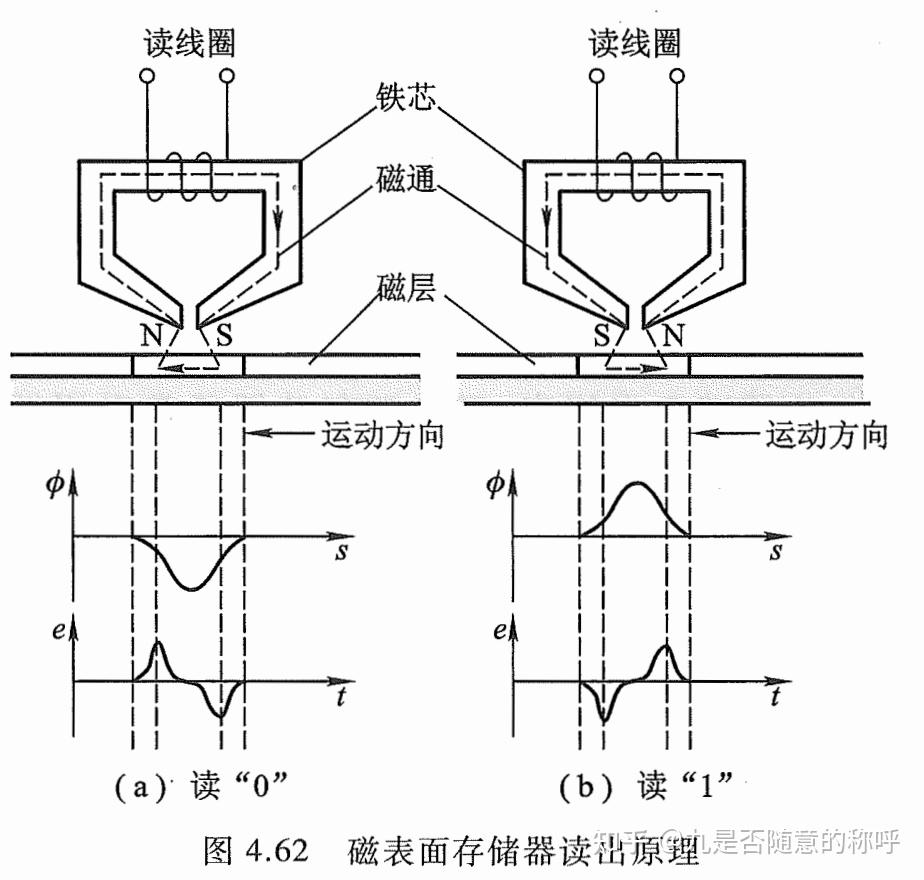

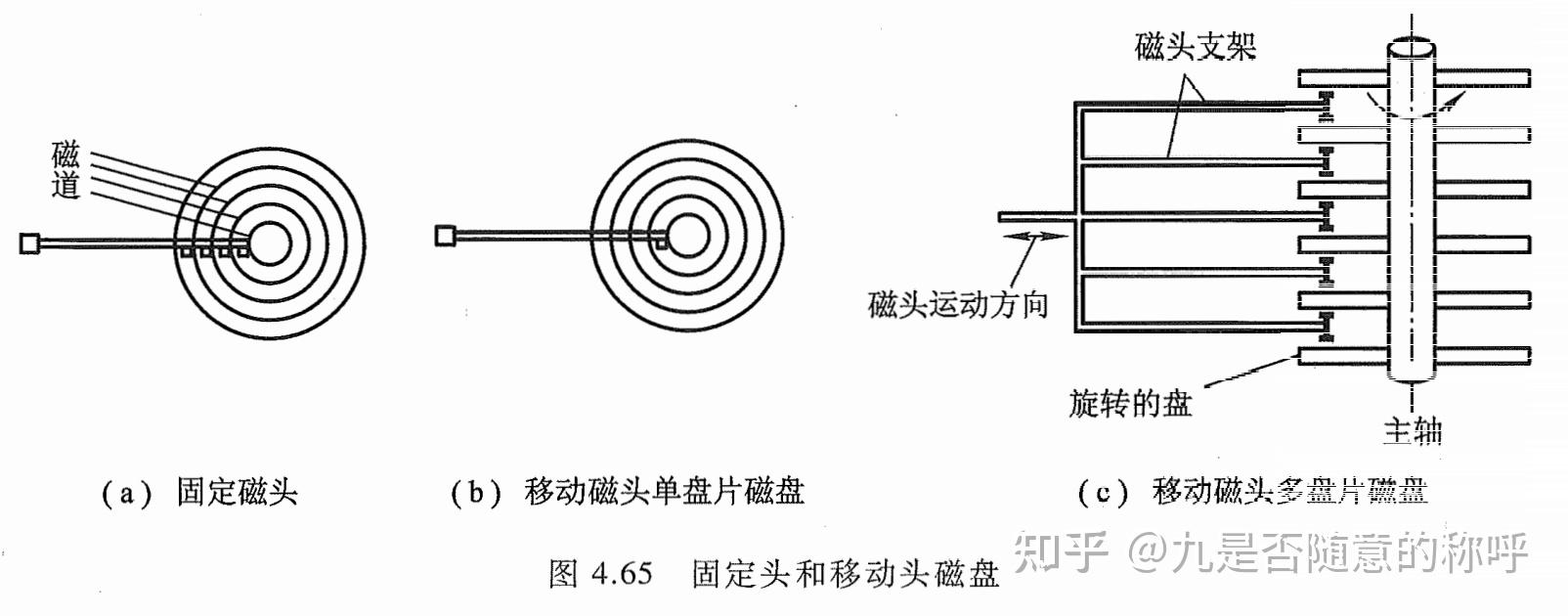

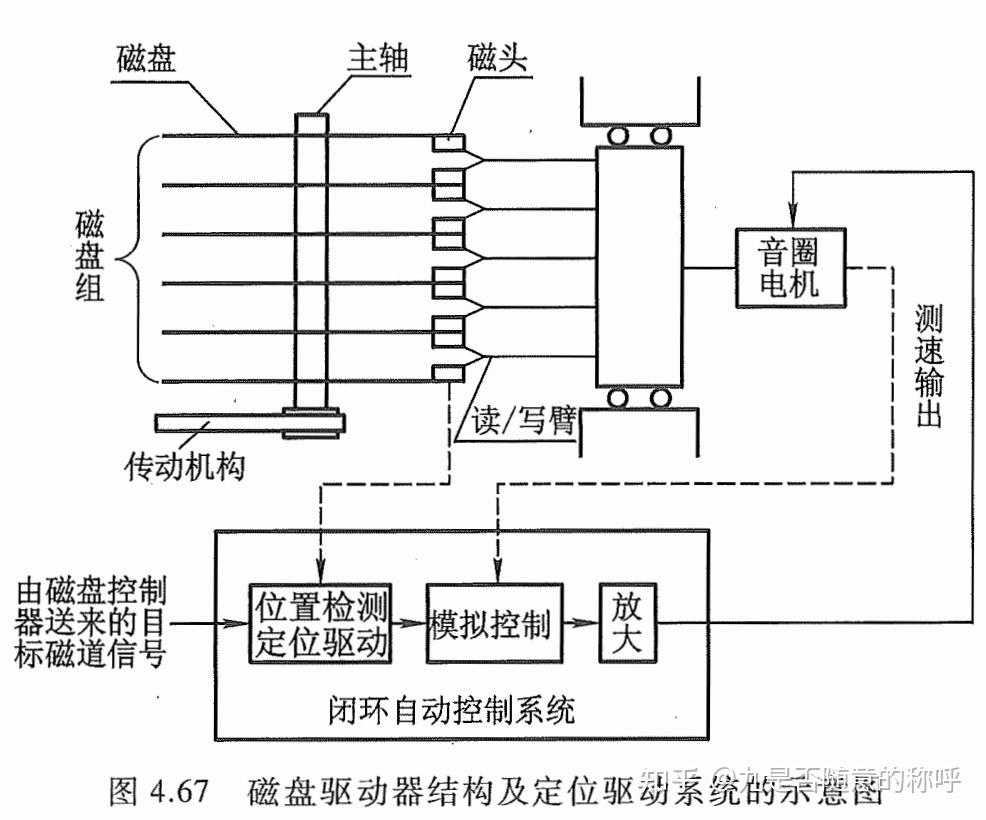

计算机组成原理 – chapter four 存储器 《计算机组成原理(第3版)》(唐朔飞)【简介_书评_在线阅读】 – 当当图书 (dangdang.com) 计算机组成原理(上)_中国大学MOOC(慕课) (icourse163.org) 第二篇 – 计算机系统的硬件结构 计算机硬件系统由中央处理器、存储器、I/O系统以及connect它们的系统总线组成,本篇主要介绍了系统总线、存储器和I/O系统。 这个chapter重点介绍了主存储器的分类、工作原理、组成方式以及与其他部件(像CPU)的联系,还介绍了高速缓冲存储器和磁表面存储器等的基本组成和工作原理的。 用不同的存储器组成具有层次结构的存储系统的概念。 four.1 概述 four.1.1 存储器分类 存储器是计算机系统中的记忆设备,用来存放程序和数据。出现了I/O和存储器直接存取方式(DMA)。也使存储器的地位更加突出。存储器的性能已成为计算机系统的核心,多处理器需要和主存交换信息,在相互通信中,需要共享存储器中的数据。 1、按存储介质分类 存储介质是指能寄存“0”、“1”两种代码并能区别两种状态的物质或器件。存储介质主要有 半导体器件、磁性材料和光盘等。 (1)半导体存储器,存储件由半导体器件组成的存储器称为半导体存储器。现代半导体存储器都用超大规模集成电路工艺制成芯片,优点:体积小、功耗低、存取时间短,缺点:电源消失时,所存信息也丢失,易失性存储器,目前开发出了非挥发性材料制成的半导体存储器,克服了信息易失的弊病。 按材料不同分类:双极性(TTL)半导体存储器 和 MOS半导体存储器。前者高速的,后者高度集成且制造简单成本低廉功耗小,后者应用广泛。 (2)磁表面存储器,在金属或塑料基体的表面上涂上一层磁性材料作为记录介质,工作时磁层随载磁体高速运转,用磁头在磁层上进行读/写操作,故称为磁表面存储器。 按载磁体形状的不同,可分为:磁盘、磁带和磁鼓(很少使用了),由于用具有矩形磁滞回线特性的材料作磁表面物质,它们按其剩磁状态的不同而区分“0”和“1”,而且剩磁状态不会轻易丢失,这类存储器具有非易失性的特点。 (3)磁芯存储器,体积大、工艺复杂、功耗太大,20世纪70年代以后,逐步被半导体存储器取代,目前几乎已不被采用。 (four)光盘存储器,应用激光在记录介质(磁光材料)上进行读/写的存储器,具有非易失性特点,光盘记录密度高、耐用性好、可靠性高和可互换性强等特点。 2、按存取方式分类 随机存储器、只读存储器、顺序存取存储器 和 直接存取存储器 (1)随机存储器(Random Access Memory),RAM是一种可读/可写存储器,任何一个存储单的内容都可以随机存取,存取时间和存取单的物理位置无关。主存都采用这种随机存储器。根据原理不同可分:静态RAM和动态RAM。 (2)只读存储器(Read Only Memory)ROM,只能初始化写入,以后只能读不能写,存放固定不变的程序、常数和汉字字库。和RAM可共同作为主存的一部分,统一构成主存的地址域。还有很多种不同的ROM,像MROM、PROM、EPROM等。 (3)串行访问存储器(顺序存取存储器),对存储单进行读/写操作时,按其物理地址的先后顺序寻找地址。磁带就是的,磁盘属于部分串行访问存储器,首先直接访问先找到磁道,然后顺序寻访找到扇区,称作直接存取存储器。 3、按在计算机中作用分类 主存储器、辅助存储器和缓冲存储器 主存储器(主存)可以和CPU直接交换信息,辅助存储器(辅存)是主存储器的后援存储器,用来存放暂时不用的程序和数据,不能和CPU直接交换信息,主存速度快、容量小、价格高,辅存速度慢、容量大、价格低。缓冲存储器(缓存)用在两个速度不相同的部件之中。CPU和主存之间可设置一个快速缓存。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/17817.html