首先,了解一下什么是GMSL

GMSL(Gigabit Multimedia Serial Links),中文名称为千兆多媒体串行链路,是Maxim公司推出的一种高速串行接口,适用于音频,视频和控制信号的传输。

通信介质支持同轴电缆以及屏蔽双绞线,使用50Ω同轴电缆或者100Ω屏蔽双绞线(STP)时,长度可达15m甚至更长

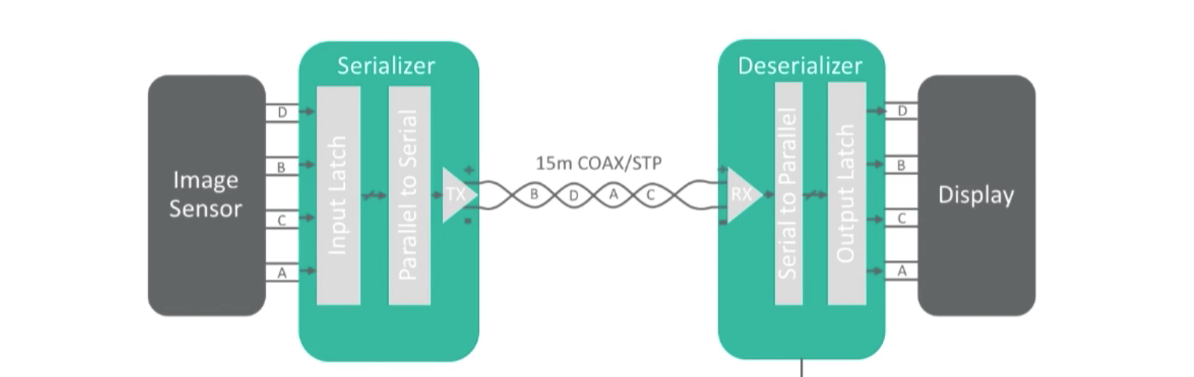

其核心技术为串行器/解串器技术,简称SerDes.首先通过串行器将并行数据流转为串行数据流,然后通过更高的频率进行传输,之后通过解串器将接收到的串行数据流转换为并行数据流。

GMSL诞生的意义

GMSL的意义在于解决了音频,视频和控制信号的高速传输问题。

在GMSL诞生之前,面对大量的数据传输一般采用的方法是通过并行总线增加带宽,一根线传输不够,我10根线总够了吧,10根还不够,我继续往上加。这种方式面临一个问题,就是线束会特别多,在工业生产中,大量的线束意味着增加成本和重量,同时也会增加EMI电磁干扰。因此线束的数量一般不能太多,但面对大量的数据,我又该怎么传输呢?还有一个办法就是增加频率,我之前一秒发10组数据,我现在改成一秒发100组,这种方式在数据量不算太大时,是可以实施的。但当数据量达到一定量级后,高频率的发送数据会使并行总线的劣势显示出来了。

并行总线传输数据的前提是使用同一时序(同时发送,同时接收)。当频率过高时,数据传送难以和时钟同步,同时布线的长度稍有差异,也会导致同步困难,另外,提升时钟频率还容易引起信号线间的相互干扰。总之,一系列的问题表明高速的数据传输并行总线是无法胜任的,这也是目前并行总线的技术瓶颈所在。

并行总线无法胜任高数据流传输,于是人们又把目光集中到串行总线上。想了想,串行总线就一根,不存在信号线之间的干扰,而且也没有同一时序问题,只需提高频率,就能进行高数据流传输,而且工业上,串行总线一般使用差分信号进行传输,这更加保证了信号的准确性。可以说,目前面对高数据流的传输,大家一般都会采用串行总线,差分信号传输。

以ADAS摄像头为例,这也是GMSL应用的主要领域。一般来讲,摄像头除了对外发送捕获到的图像数据外,还会发送帧同步信号,行同步信号,像素时钟等信息,此外还有电源供给等等,它是由许多信号线组成的一个并行总线,之前我们说过,并行总线在高速的数据传输过程中,是不占据优势的,因此我们需要将这些并行的信号合并为串行信号,再通过更高频率进行传输。

办法可能看起来很简单,但其中涉及的技术却是很复杂的,需要考虑数据流的合并、回原、带宽以及稳定性等等问题,目前掌握这项技术的只有Maxim和TI两家。

Maxim将这种串行器/解串器技术称为GMSL;

TI将串行器/解串器技术称为FPD Link,现已发展到第三版本:FPD Link III

这两家旗下分别有相对应的串行器和解串器产品,一般是为摄像头供应商服务,集成到摄像头内部,作为OEM的二级供应商。

今天我们的内容只涉及GMSL

GMSL的通信机理

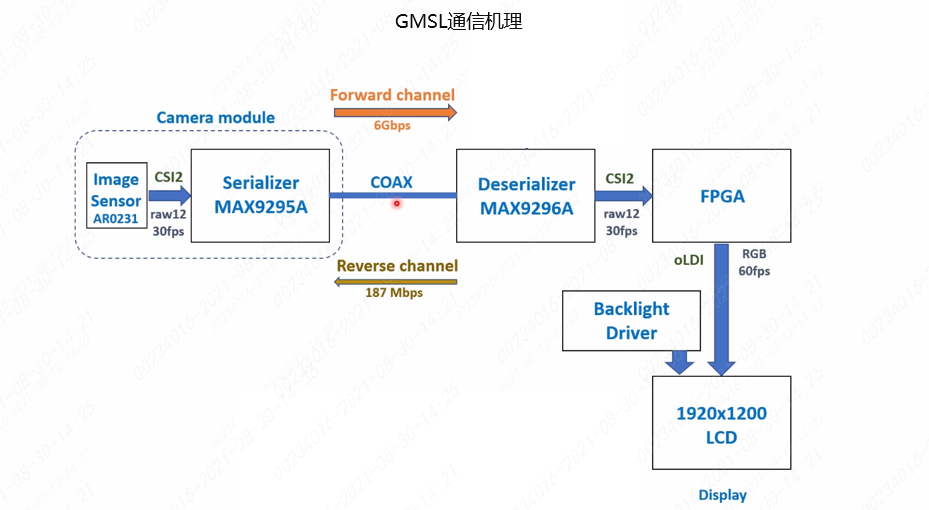

下图为GMSL在ADAS摄像头中的应用,其大体流程如下:

具体描述:

- 图像传感器Image Sensor将捕获的光信号转为数字信号,经CSI2协议传输给串行器(MAX9295A),

传输内容包括:图像数据信息,像素时钟,行同步信号,帧同步信号,其中raw12表示摄像头的传输数据格式为原始数据raw格式,每个像素点有12bit数据,30fps表示每秒发送30张图像 - 串行器接收到数据信息后,对信息进行串行化处理,将数据整理成包的形式,然后通过同轴电缆,将包以串行的形式发送出去,我们注意到在通过同轴电缆时,有两个方向的数据流传输,其中一个是前向通道,用于发送摄像头捕捉的图像数据,其带宽为6Gbps,还有一个为回馈通道,用以接收应答信息,带宽为187Mbps,这两个通道的传输速率是不一样的,可以根据实际需要进行设定,这也是GMSL的一大特色

- 之后解串器会接收到串行器串行化的数据,对数据再进行解串,使数据回复至原来模样,然后将原始数据传给FPGA,这个一个定制电路板,一般图像处理器ISP模块会集成到里面,原始数据其实就是发送给了FPGA里面的ISP模块,在它里面对数据进行一些算法处理,最终输出RGB或者YUV格式

- 图中是将处理好的数据发送给了LCD(液晶显示器),但在自动驾驶中,这个地方就会有些差异,ISP会将处理好的图像数据发送给FPGA里的AI芯片,通过卷积神经网络(CNN)对图像进行分类,检测,跟踪等等,然后根据实际情况,指挥FPGA中的MCU对底盘进行控制,以达到自动驾驶的目的

GMSL数据传输

本文以MAX96711产品文档为例,介绍GMSL数据传输的特点:

MAX96711产品描述

- 该设备可在各种输入宽度和字数下工作,串行数据速率高达1.74Gbps

- 高带宽模式提供116MHz的并行时钟速率,具有12位视频数据和2位同步(HS/VS)数据

- 嵌入式9.6kbps至1Mbps控制通道程序

- 序列化程序、反序列化程序和任何连接的UART或I2C外围设备。

- 为了促进安全应用,该设备具备视频和控制数据的CRC保护。

- 控制信道重传和高抗扰度模式减少位错误对通信的影响

串行链路信号和数据格式

序列化程序对输入的并行数据进行加扰,然后将其与前进控制数据相结合。这个数据之后会进行编码然后以几倍于输入字速率的单个序列化比特流进行传输(取决于总线宽度)。反序列化程序接收串行数据并恢复时钟信号。然后,数据将被反序列化、解码并解扰为并行输出数据和前向控制数据

工作模式

GMSL设备可配置为以多种模式运行(取决于应用程序)。这些模式可以更有效地利用串行带宽。其中大部分设置在系统设计期间设置,并使用外部配置引脚或通过寄存器位进行配置。

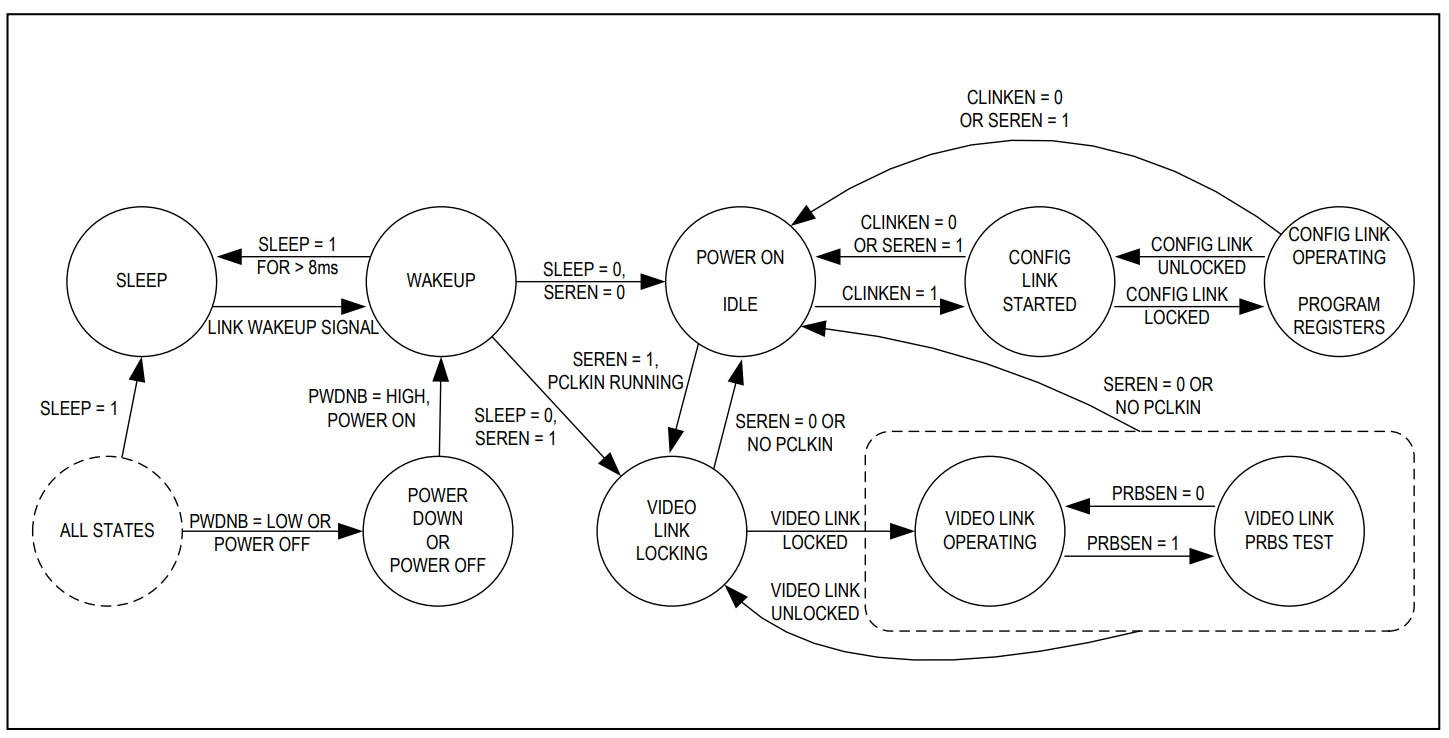

视频链路和配置链路

在正常工作中,序列化程序以视频链路模式运行(serializer SEREN=1)将视频数据和控制数据通过串行链路发送。在序列化程序中设置SEREN=0关闭序列化。序列化程序以视频链路模式启动,需要有效的PCLK才能运行。当PCLK不可用时,配置链路可用于设置串行器,解串器和外围设备。在序列化程序中设置SEREN=0和CLINK=1以启用配置链接(SEREN=1强制序列化程序进入视频链接模式)。一旦PCLK被建立,就打开视频链路(SEREN=1)。

默认情况下,视频链路模式需要有效的PCLK才能工作。在序列化程序中设置AUTO_CLINK bit=1和SEREN=1,使设备在视频链路和配置链路之间自动切换,当PCLK不存在时。

单/双模式

单/双模操作将可用的1.74Gbps带宽配置为各种宽度和字速率。单模操作与所有GMSL设备和串行器兼容,每个串行字产生一个并行字。双模式为每个串行字序列化两个半宽并行字,从而使并行字速率范围增加2倍(与单模式相比)。对于单模式操作,设置DBL=0;对于双模式操作,设置DBL=1。

HS/VS编码

默认情况下,GMSL为HSYNC、VSYNC和DE(如果使用)分配一个视频位插槽。使用HS/VS编码,该设备将对特殊数据包进行编码,以同步信号,从而释放额外的视频比特槽。当设备处于高带宽模式(HIBW=1)时,默认情况下HS/VS编码打开。DE仅在HIBW=1且DE_EN=1时编码。当HIBW=0时,设置HVEN=1以启用HS/VS编码(DE,如果启用,则使用一个视频位)。HS/VS编码要求HSYNC、VSYNC和DE(如果使用)在活动视频期间保持高电平,在消隐期间保持低电平。使用反极性同步信号时,使用HS/VS反转。

错误监测

串行链路的8b/10b编码/解码和1位奇偶校验检测串行链路上发生的位错误。可选的6位CRC检查是以牺牲6个视频位为代价的(当HIBW=0时)。要激活6位CRC模式,首先在远程侧设备中设置PXL_CRC=1,然后在本地侧设备中设置。当使用6位CRC模式时,可用的内部总线宽度在单输入模式(DBL=0)下减少6位,在双输入模式(DBL=1)下减少3位。注意,由于串行器或解串器的引脚可用性,输入总线宽度可能已经减小;因此,CRC的带宽减少可能不可见

一个额外的32位视频链路CRC可通过设置LINE_CRC_EN=1获得。启用时,序列化程序计算视频链路的32位CRC,并在消隐期间发送此信息。解串器将接收到的CRC与视频链路数据进行比较。当检测到CRC错误时,解串器的LINE_CRC_ERR位锁存。读取时,LINE_CRC_ERR清除。

总线带宽

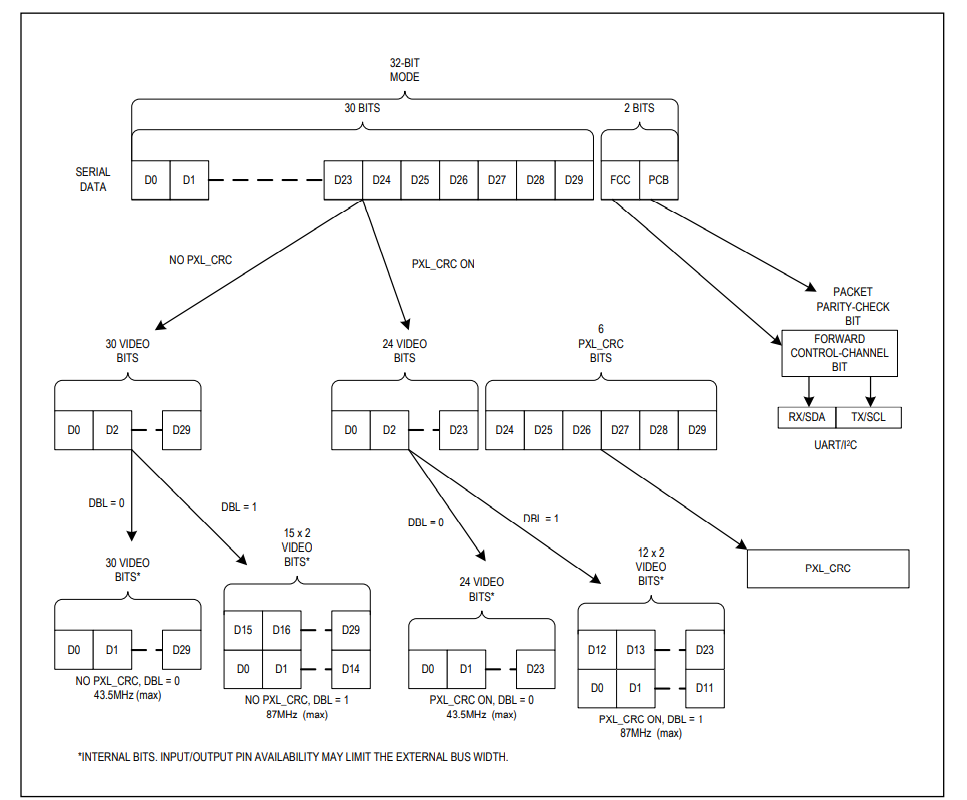

串行链路具有多个总线宽度设置,这些设置决定并行总线宽度和产生的并行字速率。串行链路的最大串行比特率为1.74Gbps。BWS位决定每个串行数据包的长度是30位还是40位,当BWS=0或1时,这将转换为最大串行数据包速率(以及产生的最大并行字速率)分别为58MHz或43.5MHz。编码将24、27或32并行位转换为30或40位串行数据包。一位用于奇偶校验,另一位用于控制通道。在可选的6位CRC期间,使用额外的6位。除此之外,如果使用双模式,则会将剩余的字大小一分为二。剩余的位可用于视频位(如果不使用H/V编码,则减去任何同步位)

以下模式列出了内部总线宽度。可用输入和输出引脚的数量可能会限制可用的实际总线宽度

-

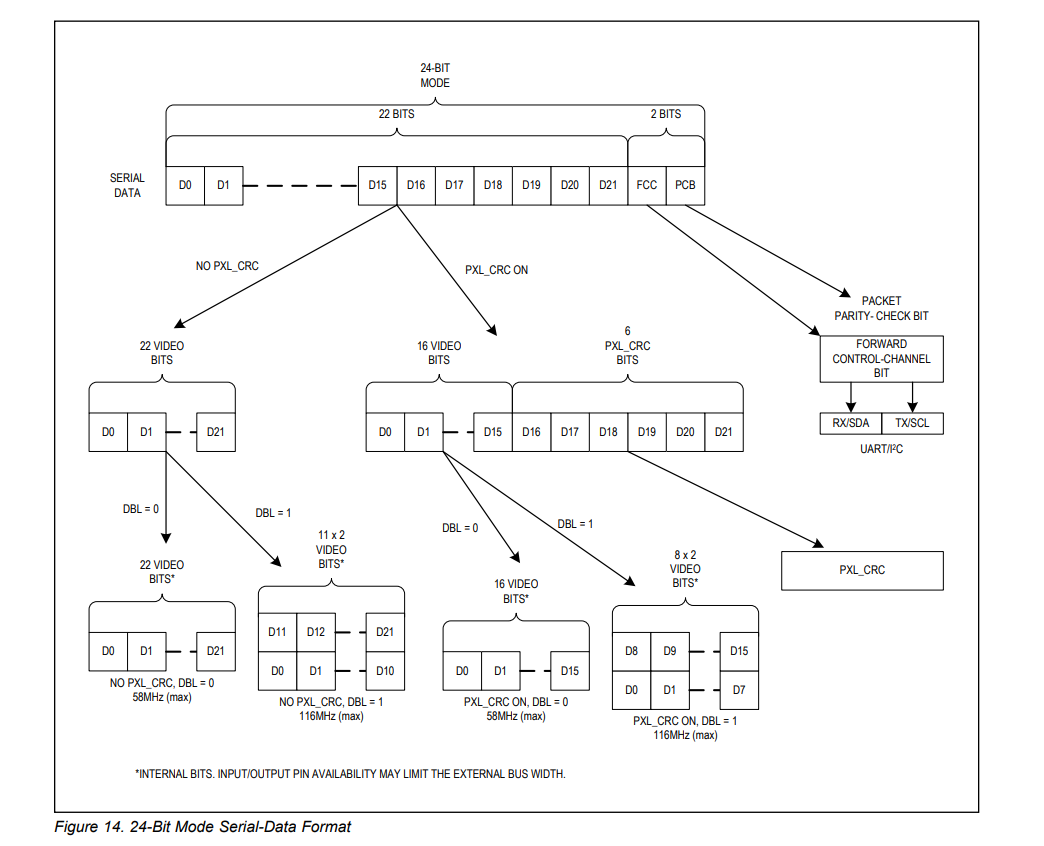

24位模式

当BWS=0和HIBW=0时,30位串行包与表示24位(24位模式)的三个8b/10b符号相对应。在奇偶校验和控制信道之后,如果使用或未使用CRC(单模式下),则留下16/22位视频数据;如果使用或未使用CRC(双模式下),则留下8/11位视频数据。

-

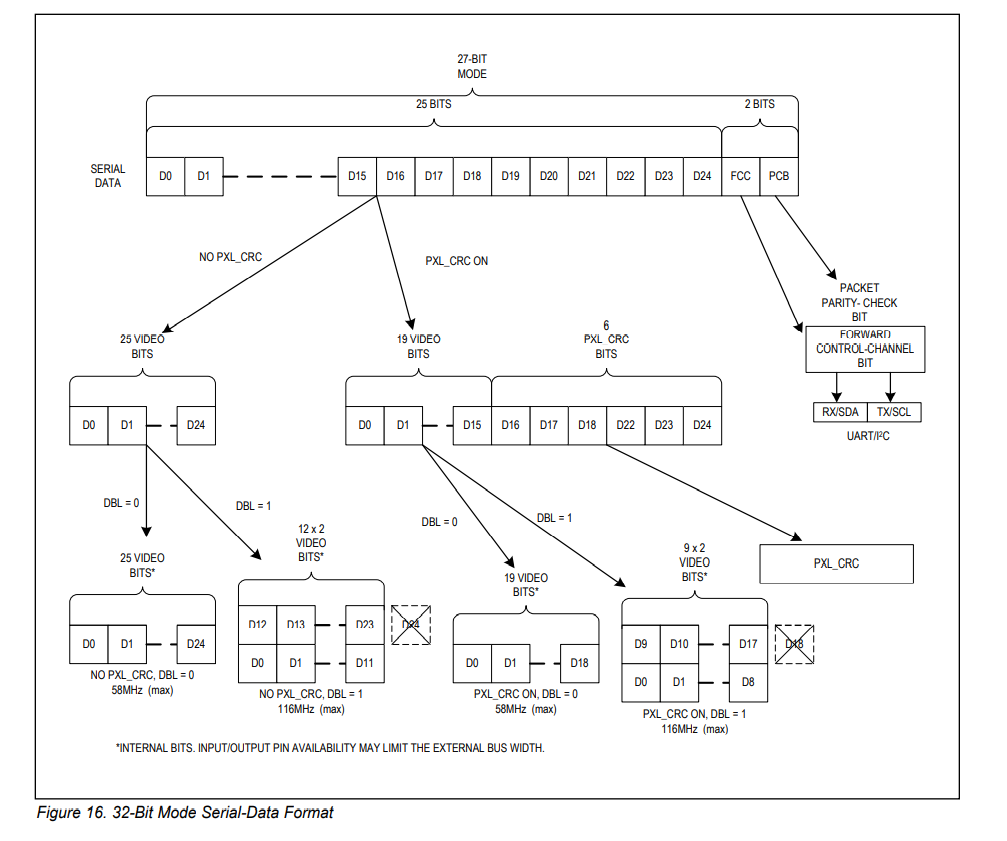

27位高带宽模式

当BWS=0和HIBW=1(高带宽模式)时,30位串行包与表示27位(27位模式)的三个9b/10b符号相对应。在奇偶校验和控制信道之后,如果使用或未使用CRC(单模式下),则留下19/25位视频数据;如果使用或未使用CRC(双模式下),则留下9/12位视频数据。

-

32位模式

当BWS=1时,40位串行包对应于表示32位(32位模式)的四个8b/10b符号。在奇偶校验和控制信道之后,如果使用或未使用CRC(单模式下),则留下24/30位视频数据,如果使用或未使用CRC(双模式下),则留下12/15位视频数据。

控制信道和寄存器编程

控制通道通过串行总线发送信息用于控制串行器、解串器和任何附加的外围设备。控制信道在串行链路上是多路复用的,无论有没有视频通道,都是可用的

前向控制信道

从串行器发送到解串器的控制数据为在前向控制信道上发送。数据被编码作为前向高速链路中的串行位之一。之后经过解串器,从串行链路中提取前向控制通道数据。前向控制信道带宽超过最大外部控制数据速率,并且前向控制通道上发送的所有数据均显示在传输延迟几位后的远程端。

反向控制通道

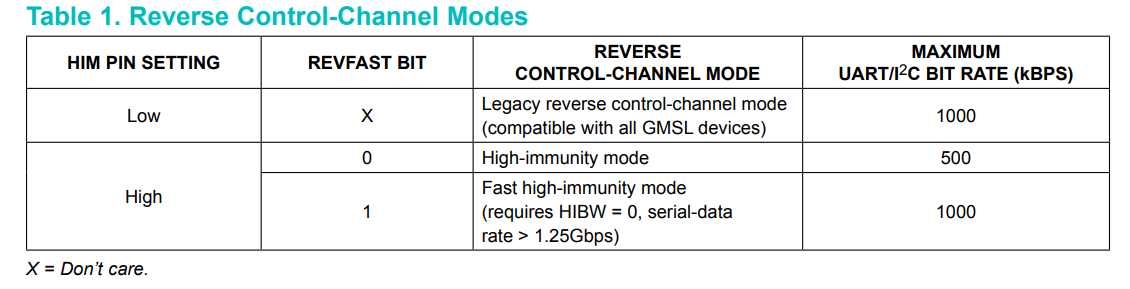

从解串器发送到串行器的控制数据通过反向控制通道发送。数据被编码为一系列1μs脉冲,最大原始

数据速率为1Mbps。高抗扰度模式可用于增加反向控制通道的鲁棒性,在一个降低后的500kbps原始比特率下。在下表中,设置REV_FAST bit=1将该速率增加回1Mbps。在I2C模式下,如果输入数据速率(编码后)超过反向数据速率,则通过时钟拉伸保持输入时钟,以减慢外部时钟进而满足内部比特率。

UART接口

UART接口与所有GMSL设备兼容,通过多个UART数据包在设备之间发送命令。有两种模式可用:基本模式和旁路模式。基本模式用于串行器、解串器和使用UART-to-I2C转换的I2C外围设备之间的通信。旁路模式允许使用任何UART协议与外围设备进行全双工UART通信

I2C接口

串行链路通过控制通道将串行器和解串器I2C接口连接在一起。当I2C主机向链路一侧(本地侧)发送命令时,控制通道将该信息转发至链路另一侧(远程侧),并从链路另一侧(远程侧)发送该信息,从而允许单个微控制器配置串行器,解串器和外围设备。微控制器可以位于串行器端(显示应用程序)和解串器端(相机应用程序)。只要使用软件仲裁方法,就支持双微控制器操作。串行链路认为在任何给定时间只有一个微控制器在通话。

远程操作

当I2C主设备在本地从设备(直接连接到主设备的串行器/解串器)上启动通信时,远程侧设备充当主设备,发送从本地端设备转发的数据,并转发从连接到远程设备的外围设备接收的任何数据。该远程侧主设备根据I2C主设置寄存器中的定时设置进行工作。设置主设置项来满足被外部微控制器所使用的定时设置。

时钟拉伸定时

I2C接口使用时钟拉伸来允许数据通过串行链路转发。主微控制器以及任何连接的外围设备必须接受GMSL设备的时钟拉伸。

基于数据包的I2C

基于数据包的控制信道可用于增强控制信道的错误处理。这种控制信道方法处理同时发生的GPI/GPO和I2C传输,以及错误检测和重传。

数据包协议摘要

基于数据包的控制信道使用一个同步的基于符号的系统通过控制信道进行发送数据,通过控制信道发送的数据被分割成符号并存储在传输队列中,然后通过链路发送。如果需要同时发送GPI和I2C数据(例如,在I2C传输期间GPI进行转换),则来自这两个命令的符号被组合在队列中。如果传输队列为空,则通过链路发送空闲数据包,以保持控制信道锁定。接收到的I2C数据包由微控制器SCL速率(本地设备)或编程主比特率(远程设备)确定输出。设备保持SCL低电平(时钟拉伸),直到从远端设备接收到数据

控制信道错误检测和数据包重传

当使用基于数据包的控制信道时,所有数据包的错误都会通过CRC检查。CRC使用1、5或8位检测数据包中的1、3或4个随机位错误。每当检测到错误时,发送器会重新传输数据包。如果重试次数超过8次,发送器将设置一个标志。接收器过滤掉有错误的数据包。

GPO/GPI控制

串行器上的GPO遵循解串器上的GPI转换。此GPO/GPI功能可用于传输信号,如环绕视摄像头系统中的帧同步。可选的,GPO可以通过寄存器位直接设置。

扩频

串行器包含一个可编程的扩频输出,通过将时钟频率峰值分散到整个频谱来降低发射电平。此外,串行器和解串器可以跟踪扩展输入时钟,消除对多个扩展时钟的需要

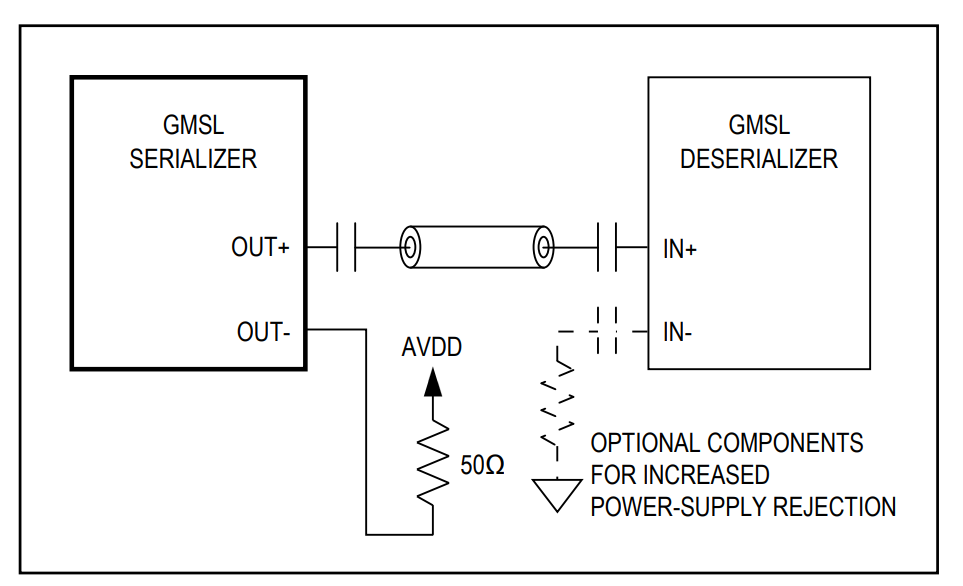

电缆类型配置

驱动器输出可编程为两种类型电缆,100Ω双绞线和50Ω同轴电缆。同轴模式下,将OUT+连接到解串器的IN+。将未使用的IN-引脚保持未连接状态,或将其通过50Ω接地和一个电容器增加电源拒绝。通过50Ω电阻器将OUT-连接至VDD

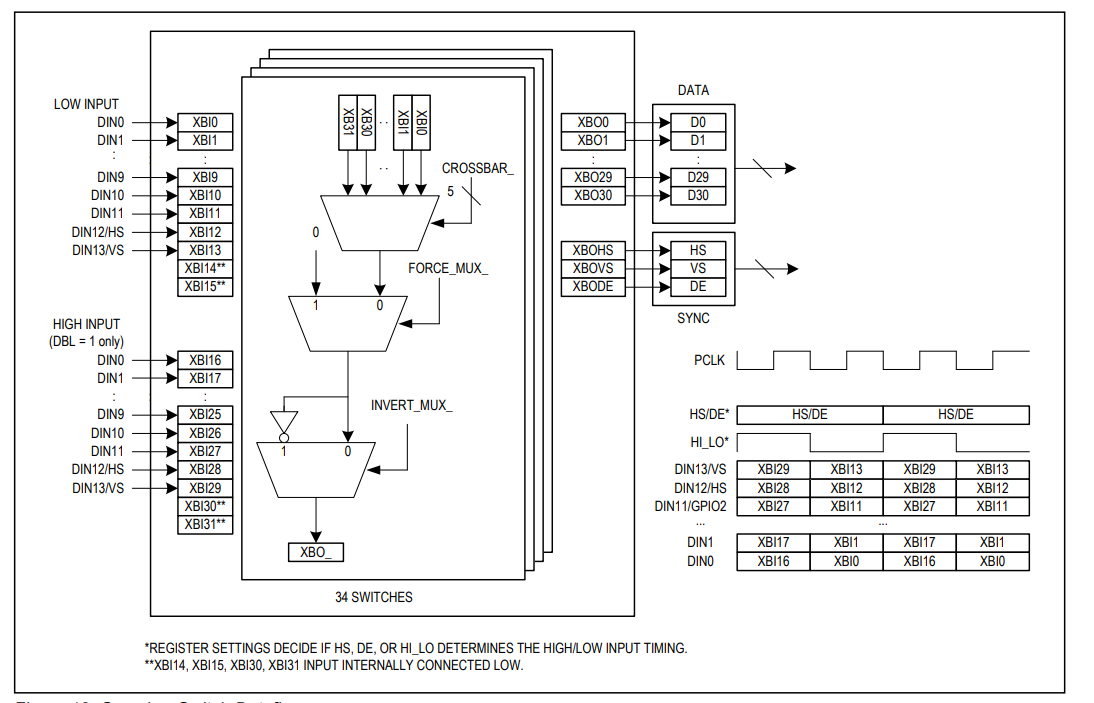

交叉开关

交叉开关在并行输入/输出和SerDes之间按路径发送数据。无障碍的路径确保了视频源和目标之间的映射。由于每个交叉开关矩阵输出 (XBO_)一个通过crossbar_寄存器位从可用的交叉矩阵输入 (XBI_)中进行选择的一个多路复用输入,因此多个交叉开关输出可以使用相同的交叉开关输入。默认情况下,同步信号共享相同的输入作为视频数据的MSB(最高有效位)

视频定时生成器

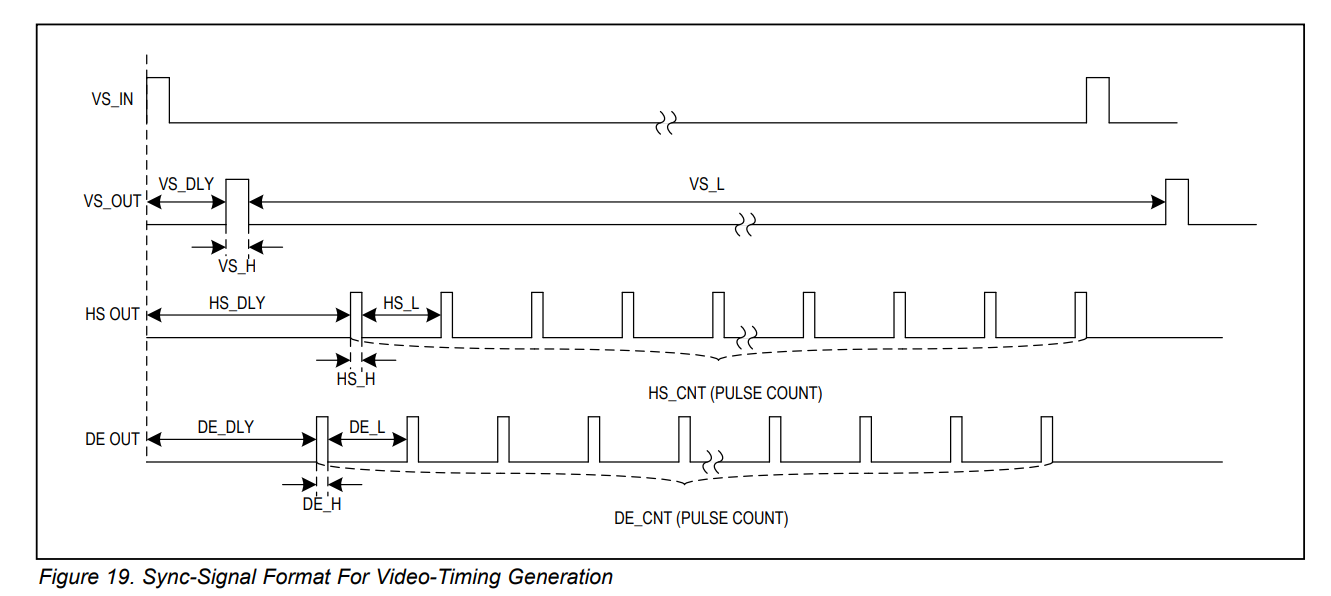

串行器包括可编程视频定时生成器用于生成/重定时输入同步信号。这个定时生成器可用于修改相机的输入定时,过滤掉同步信号中的小故障,或减少所需的输入同步信号数。每个同步信号可以单独重定时或不修改。几个寄存器决定定时参数的长度(PCLK循环)如下图所示。定时参数包括高/低周期长度、行计数和输入VS信号的延迟。

定时发生器使用三种不同的触发模式,跟踪、单触发和自动运行。跟踪模式查看输入VSYNC,一旦收到三个连续相同的VSYNC信号就锁定。跟踪器之后继续输出相同的信号,擦除任何VSYNC上可能出现的故障。如果三个连续的输入波形与锁定信号不匹配,跟踪器将尝试重新锁定到新信号。单触发器为每个输入VSYNC边生成一个已经生成的帧。自动运行以确定的速率(这个速率由VSYNC高/低周期决定)生成新帧。如果有新的VSYNC信号在帧(单触发或自动运行模式下生成的帧)之前出现,那么新帧立即开始,缩短前一帧。

关机和睡眠模式

当不需要完全运行时,可以使用几种睡眠和关机模式

- 配置链路

当高速视频链路不需要或不可用时,可以使用配置链路代替高速视频链路。在配置链路模式下,并行数字输入/输出被禁用,锁定引脚保持低位,串行链路内部生成自己的时钟,以允许控制通道(UART/I2C和GPIO)的完全操作。 - 串行器禁用

当串行链路不需要时,例如当下游设备断电时,用户可以禁用串行器。在此模式下,所有前向通信将关闭。用户可以通过本地或反向通道重新启用串行器 - 睡眠模式

为了进一步降低功耗,可以将设备置于睡眠模式。在此模式下,所有寄存器保持其编程值,设备中的所有功能均断电,本地控制接口上的唤醒检测器和串行链路除外。被唤醒检测器检测到的任何活动都会临时打开控制通道接口。在此期间,微控制器可以命令设备退出睡眠模式。 - 断电模式

最低功耗模式为断电模式。在此模式下,所有功能均断电,所有寄存器值丢失。

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/163330.html