前言:

为了方便查看博客,特意申请了一个公众号,附上二维码,有兴趣的朋友可以关注,和我一起讨论学习,一起享受技术,一起成长。

1. 定义

静电放电(Electrostatic Discharge,ESD):是指具有不同静电电位的物体互相靠近或直接接触引起的电荷转移。当带了静电荷的物体(也就是静电源)跟其它物体接触时,这两个具有不同静电电位的物体依据电荷中和的原则,存在着电荷流动,传送足够的电量以抵消电压。这个电量在传送过程中,将产生具有潜在破坏作用的电压、电流以及电磁场,严重时会将物体击毁。

2. 特点

2.1 ESD 可形成高电位、强电场、瞬时大电流

大多数情况下 ESD 过程往往会产生瞬时脉冲大电流,尤其是带电导体或手持小金属物体的带电人体对接地导体产生火花放电时,产生的瞬时脉冲电流的强度可达到几十安培甚至上百安培。

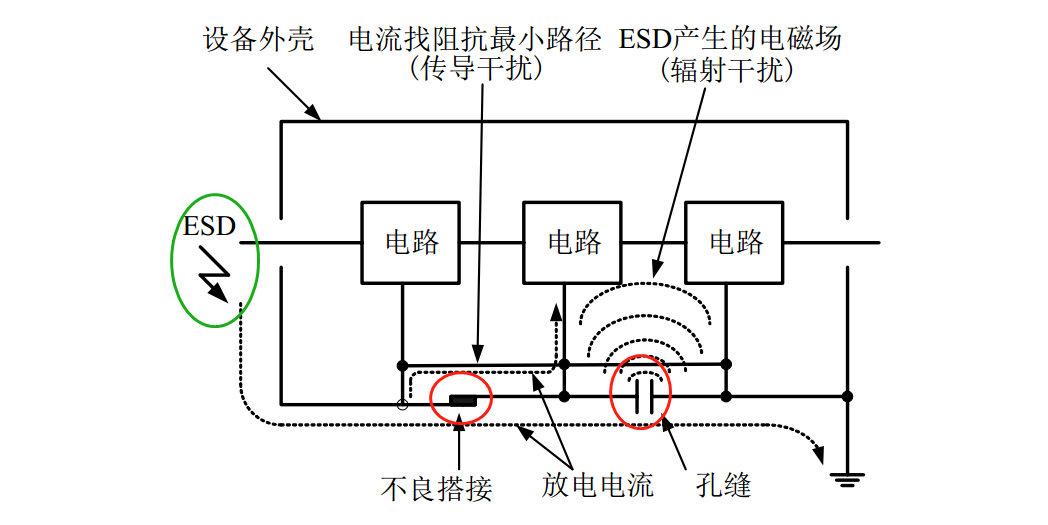

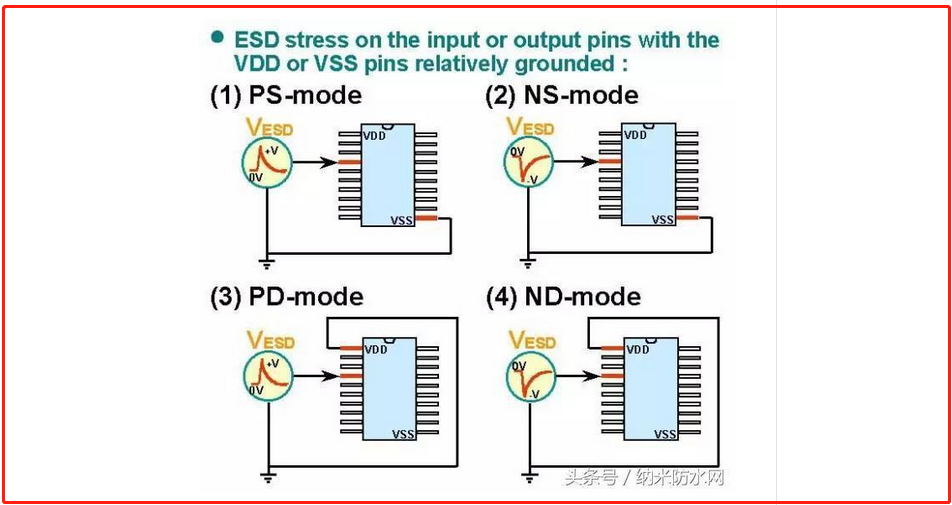

ESD 电流产生的电磁场可以直接穿透设备外壳,或通过孔洞、缝隙、输入输出等耦合到敏感电路,如图 所示:

2.2 ESD 过程会产生强烈的电磁脉冲辐射

在 ESD 过程中会产生上升时间极快、持续时间极短的初始大电流脉冲,并产生强烈的电磁辐射形成静电放电电磁脉冲(ESD Electromagnetic Pulse-ESD EMP),它的电磁能量往往会引起电子系统中敏感部件的损坏、翻转,使某些装置中的易爆品误爆,造成事故。

3. 危害

ESD 对电子设备的危害主要有两种机理,其一是 ESD 电流直接流过电路造成破坏,另一种是 ESD 电流产生的电磁场通过近场的电容耦合、电感耦合或远场的空间辐射耦合等途径对电路造成干扰。

ESD 可能引起易燃易爆物的起火或爆炸,也可能导致半导体器件和集成电路的击穿或失效。随着微电子技术的快速发展,特别是随着集成电路结构尺寸的减小以及 MOS 集成电路的广泛使用,静电危害已成为微电子器件的重要破坏源。静电防护问题越来越被关注,而 ESD 的防护领域也日渐广泛。

4. 三种模型

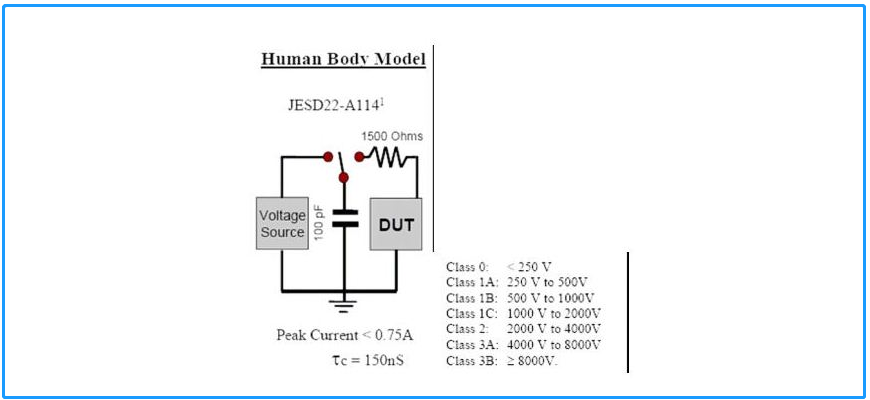

3.1 HBM:Human Body Model,人体模型:

该模型表征人体带电接触器件放电(人体摩擦产生了电荷突然碰到芯片释放的电荷导致芯片烧毁击穿),Rb 为等效人体电阻,Cb 为等效人体电容。等效电路如下图,同时给出了器件 HBM 模型的 ESD 等级。

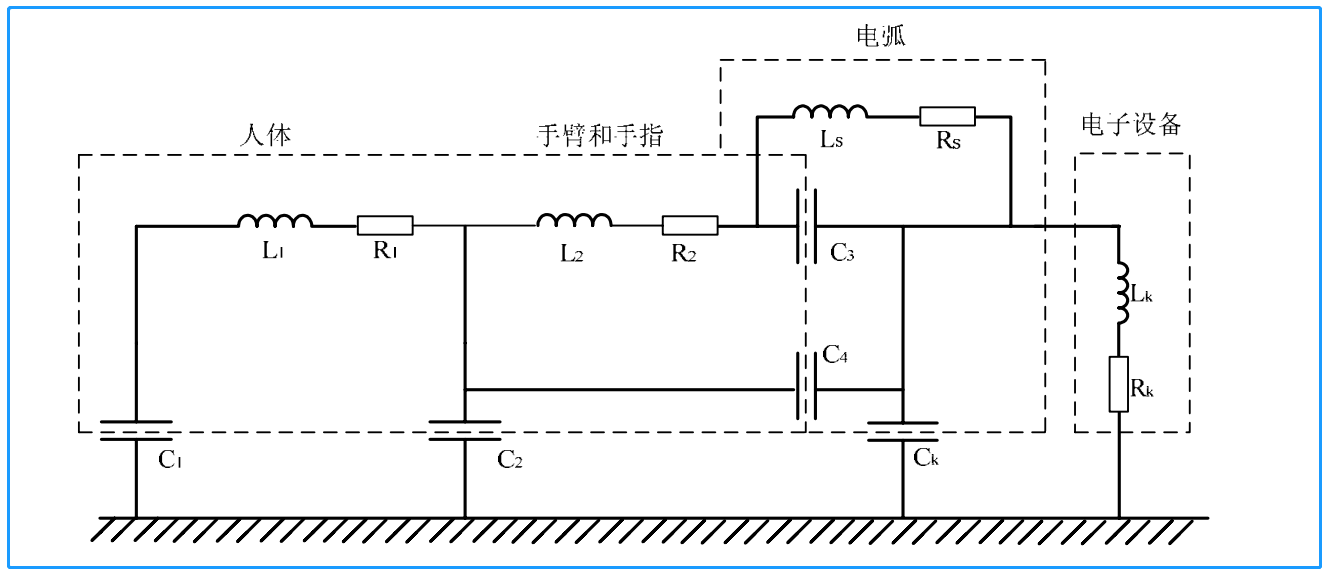

下图为人体 ESD 的等效电路。人体能储存一定的静电电量,因此人体明显地存在电容效应。人体也有电阻,其值依赖于人体肌肉的弹性、水分和接触电阻等因数。电荷转移路径中还存在电感。目前广泛使用的人体模型测试电路中人体等效电阻和电容分别为1500Ω 和 100pF。

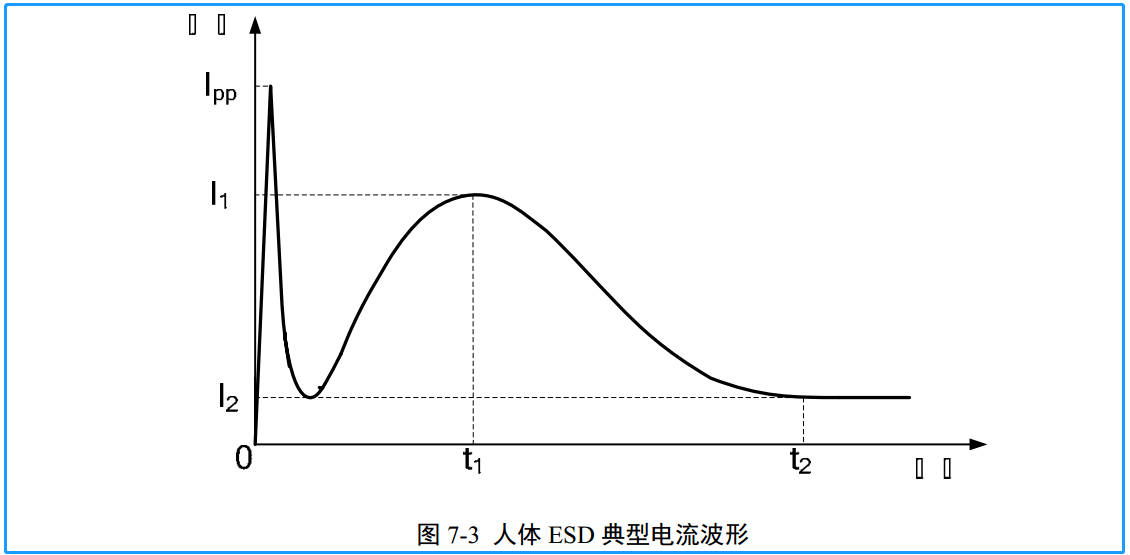

从电磁兼容的角度来看,ESD 最重要的指标是电流波形特性。来自人体的 ESD 的典型波形如下图所示。测量结果表明,ESD 波形具有很短的上升时间(<1ns)和很高的起始尖峰。起始尖峰是从手/前臂组合体经由低电感通路放电的结果,电流峰值越大,且人体接近速度越快,脉冲上升斜率越陡。另一方面,人体放电会产生时间长得多的脉冲(其它部位放电结果),持续时间可到数十微秒。因此,这两种波形组合就反映了包含人体在内的 ESD 特性。

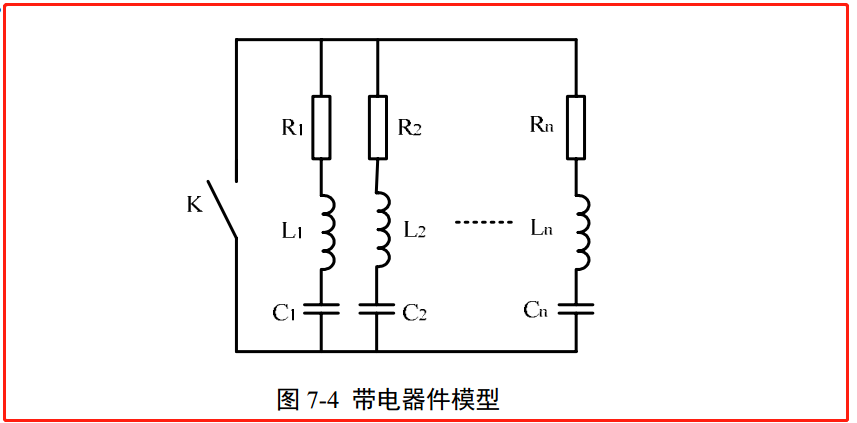

3.2 带电器件模型

由于器件本身积累静电而迅速放电造成对电子器件的损坏,带电器件模型是基于已带静电的器件通过管脚对地放电引起器件失效而建立的。

该模型电路对地放电时,得到的放电电流波形为迅速衰减的正弦波。带电器件有几个管脚同时与地接触时,就有几个放电通路,图中分别用不同的 Ri 、Li 、Ci 表示。器件放电时的脉冲峰值功率较高,可达几百瓦到几兆瓦,这么大的功率也会改变器件的参数,或使硅熔化造成器件的失效。对于多器件并联的放电通道模型,当有一个管脚接地时,器件的每条路径都有自己的放电特性,从而在路径之间产生电位差,严重时可以导致路径之间的绝缘击穿。

3.3 电场感应模型

所有的带电体周围总是存在电场,当一个器件处于静电场中时,其内部将感应出电位差。此时,当某一管脚与地相碰时,器件就会对地放电,这种放电模型称为电场感应模型。将一个 CMOS 器件置于静电场中时,其栅介质层两侧就会感应出电位差。如果电位差足够大,就可能使栅氧化层击穿。

典型的电场感应模型为:当集成电路等器件装在印制板上紧挨带电体的表面处时,由于静电感应使导电材料充电。由于集成电路通过某种方式接地,当电场强度较高时,器件上积累的电荷就会沿此接地路径放电,造成对 ESD 敏感的集成电路失效。集成电路等器件的 ESD 敏感度不仅取决于电路板和器件的感应电压,而且还取决于器件对地电容和放电路径上的电阻。同样,当设备感应的电压超过对地击穿电压,放电瞬变过程将导致设备受到干扰甚至失效。

一般情况下,静电场感应出来的电位差不会使器件立刻失效,但由于器件管脚相当于接收天线,引起与管脚相连导电部分的电场发生畸变,导致二氧化硅内部场强增加,此时就有可能引起 MOS 器件的栅极氧化膜被击穿。

5. 防护

静电及其危害的机理主要包括静电产生的强电场,ESD 产生的电弧电流所引起的电位不均,以及电弧电流感应的瞬态电磁场的影响等。

防护措施:

(1)阻止静电的产生和积累,消除 ESD 源;

(2)隔离导体,阻止放电;

(3)为 ESD 电流提供替换通路,使其旁路;

(4)屏蔽电路,阻止 ESD 产生的电磁干扰耦合到电路或设备;

(5)通过选择抗静电级别较高的器件,设计合理的工艺和电路来增强系统的抗干扰性

6. 常见电路应用

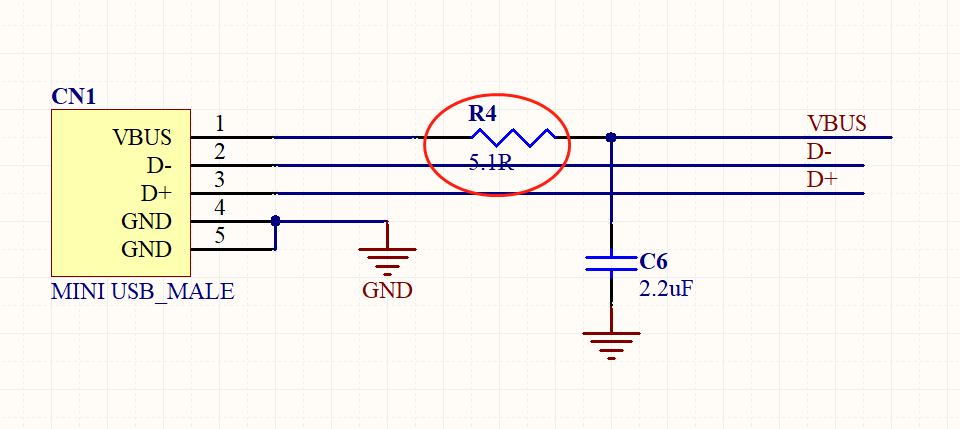

串联电阻:

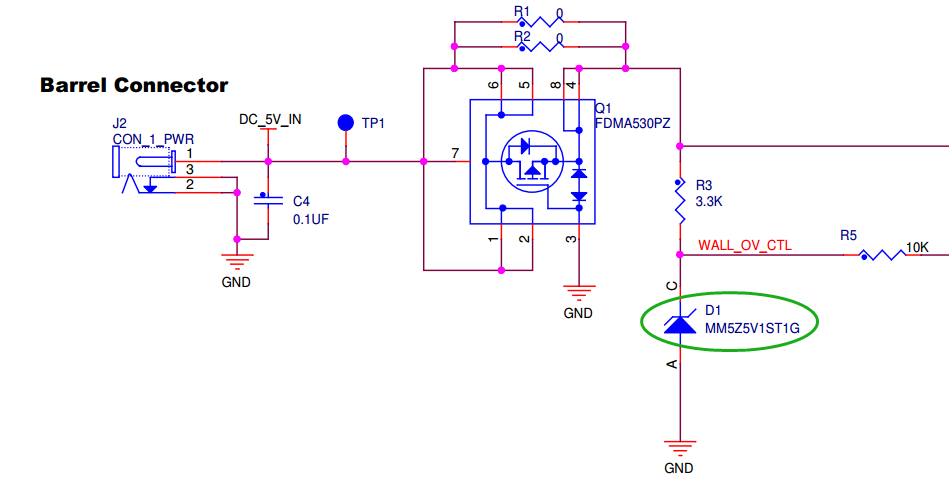

电路加齐纳二极管:(稳压二极管)

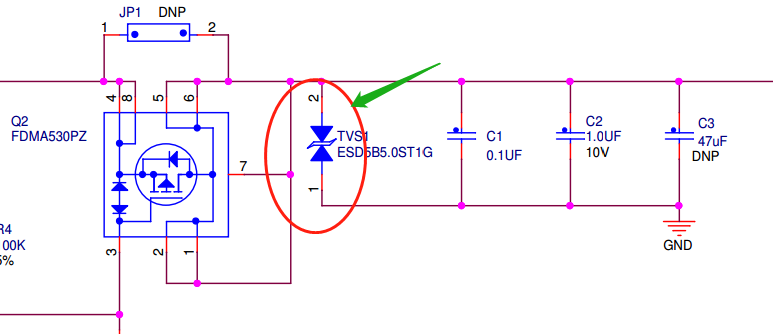

加TVS管:

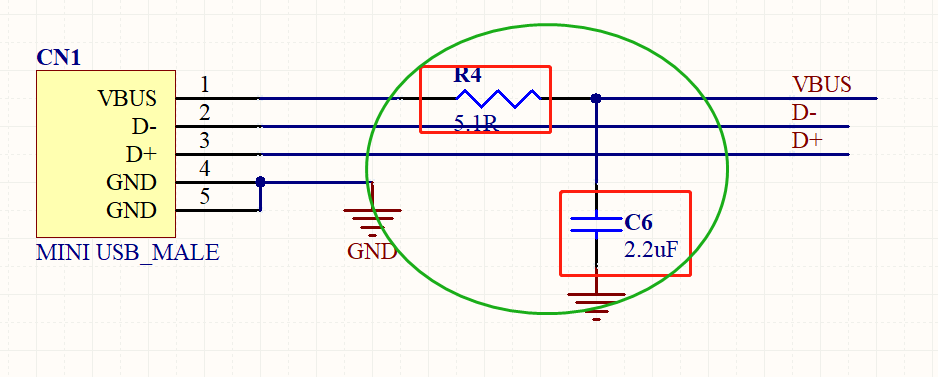

加滤波网络:

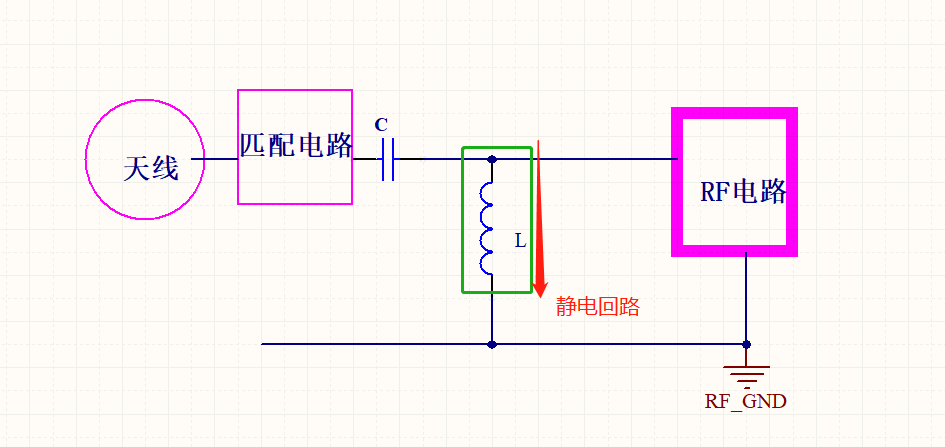

天线放电:

ESD涉及的知识广泛,这里仅仅是抛砖引玉。

参考:

- ESD 保护

2.ESD静电保护(ESD器件保护原理及选型)

3.关于静电放电(ESD)原理以及其保护方法的详细分析

4.电路及esd防护

5.[电磁兼容原理及应用]——林福昌、李化

2024最新激活全家桶教程,稳定运行到2099年,请移步至置顶文章:https://sigusoft.com/99576.html

版权声明:本文内容由互联网用户自发贡献,该文观点仅代表作者本人。本站仅提供信息存储空间服务,不拥有所有权,不承担相关法律责任。如发现本站有涉嫌侵权/违法违规的内容, 请联系我们举报,一经查实,本站将立刻删除。 文章由激活谷谷主-小谷整理,转载请注明出处:https://sigusoft.com/148630.html